### Università degli Studi di Padova Dipartimento di Ingegneria dell'Informazione

# Analysis and Design of a Transmitter for Wireless Communications in CMOS Technology

Tesi di

Antonio Passamani

Scuola di dottorato in Ingegneria dell'Informazione Indirizzo Scienza e Tecnologia dell'Informazione Ciclo XXVIII

Direttore della Scuola: Ch.mo Prof. Matteo Bertocco Coordinatore d'indirizzo: Prof. Carlo Ferrari Supervisore: Prof. Andrea Bevilacqua Padova, 29th January 2016

# Contents

| A             | cknov | wledgn        | nents                               | vi   |

|---------------|-------|---------------|-------------------------------------|------|

| $\mathbf{A}$  | bstra | $\mathbf{ct}$ |                                     | viii |

| Sc            | omma  | ario          |                                     | x    |

| $\mathbf{Li}$ | st of | Figure        | es                                  | xii  |

| Li            | st of | Tables        | 5                                   | xv   |

| Li            | st of | Symb          | ols and Abbreviations               | xvi  |

| 1             | Intr  | oducti        | on                                  | 1    |

|               | 1.1   | Growt         | h of Wireless Communications        | . 1  |

|               | 1.2   | Ubiqu         | itous Diffusion                     | . 2  |

|               | 1.3   | Standa        | ard Development                     | . 4  |

|               | 1.4   | Manda         | atory Requirements                  | . 5  |

| <b>2</b>      | Syst  | tem A         | nalysis                             | 7    |

|               | 2.1   | Releva        | nt Standards                        | . 7  |

|               | 2.2   | Maxin         | num Radiated Power                  | . 14 |

|               |       | 2.2.1         | Equivalent Isotropic Radiated Power | . 14 |

|               |       | 2.2.2         | Peak-to-Average Power Ratio         | . 16 |

|               |       | 2.2.3         | Constellation Power                 | . 18 |

|               |       | 2.2.4         | Total Radiated Power                | . 19 |

|   | 2.3                | Unwor                                               | nted Emissions                                                         | 19                                                                   |

|---|--------------------|-----------------------------------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------|

|   | 2.0                |                                                     |                                                                        |                                                                      |

|   |                    | 2.3.1                                               | Supply-Noise                                                           | 20                                                                   |

|   |                    | 2.3.2                                               | Spectral Images                                                        | 23                                                                   |

|   |                    | 2.3.3                                               | Quantization Noise                                                     | 26                                                                   |

|   |                    | 2.3.4                                               | Harmonic Distortion                                                    | 27                                                                   |

|   |                    | 2.3.5                                               | Phase Noise                                                            | 28                                                                   |

|   | 2.4                | Contri                                              | ibutors to Error-Vector Magnitude                                      | 31                                                                   |

|   |                    | 2.4.1                                               | Phase Noise                                                            | 33                                                                   |

|   |                    | 2.4.2                                               | Harmonic Distortion                                                    | 34                                                                   |

|   |                    | 2.4.3                                               | In-Phase/Quadrature-Phase Imbalance                                    | 35                                                                   |

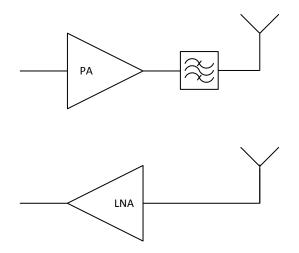

|   | 2.5                | Receiv                                              | ver Desensitization                                                    | 35                                                                   |

|   | 2.6                | Survey                                              | y of Transmitter Architectures                                         | 39                                                                   |

|   |                    | 2.6.1                                               | State-of-the-art Analog-Intensive Architecture                         | 39                                                                   |

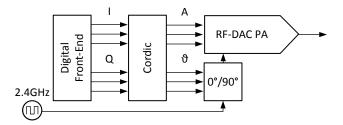

|   |                    | 2.6.2                                               | Polar Digital-Intensive Architecture                                   | 42                                                                   |

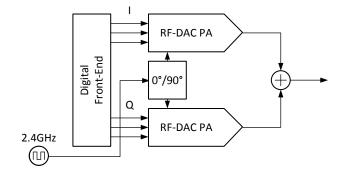

|   |                    | 2.6.3                                               | Proposed Digital I/Q Architecture                                      | 45                                                                   |

|   |                    |                                                     |                                                                        |                                                                      |

| 3 | Circ               | cuit De                                             | esign                                                                  | 48                                                                   |

| 3 | <b>Ciro</b><br>3.1 |                                                     | e <b>sign</b><br>itive and Radio-Frequency Digital-to-Analog Converter | <b>48</b><br>48                                                      |

| 3 |                    |                                                     |                                                                        |                                                                      |

| 3 |                    | Capac                                               | itive and Radio-Frequency Digital-to-Analog Converter                  | 48                                                                   |

| 3 |                    | Capac<br>3.1.1                                      | itive and Radio-Frequency Digital-to-Analog Converter                  | 48<br>49                                                             |

| 3 |                    | Capac<br>3.1.1<br>3.1.2<br>3.1.3                    | itive and Radio-Frequency Digital-to-Analog Converter                  | 48<br>49<br>51                                                       |

| 3 | 3.1                | Capac<br>3.1.1<br>3.1.2<br>3.1.3                    | itive and Radio-Frequency Digital-to-Analog Converter                  | 48<br>49<br>51<br>52                                                 |

| 3 | 3.1                | Capac<br>3.1.1<br>3.1.2<br>3.1.3<br>Switch          | itive and Radio-Frequency Digital-to-Analog Converter                  | 48<br>49<br>51<br>52<br>56                                           |

| 3 | 3.1                | Capac<br>3.1.1<br>3.1.2<br>3.1.3<br>Switch          | itive and Radio-Frequency Digital-to-Analog Converter                  | 48<br>49<br>51<br>52<br>56<br>56                                     |

| 3 | 3.1                | Capac<br>3.1.1<br>3.1.2<br>3.1.3<br>Switch          | itive and Radio-Frequency Digital-to-Analog Converter                  | 48<br>49<br>51<br>52<br>56<br>56<br>57                               |

| 3 | 3.1                | Capac<br>3.1.1<br>3.1.2<br>3.1.3<br>Switch          | itive and Radio-Frequency Digital-to-Analog Converter                  | 48<br>49<br>51<br>52<br>56<br>56<br>57<br>61                         |

| 3 | 3.1                | Capac<br>3.1.1<br>3.1.2<br>3.1.3<br>Switch          | itive and Radio-Frequency Digital-to-Analog Converter                  | 48<br>49<br>51<br>52<br>56<br>56<br>56<br>57<br>61<br>63             |

| 3 | 3.1                | Capac<br>3.1.1<br>3.1.2<br>3.1.3<br>Switch<br>3.2.1 | itive and Radio-Frequency Digital-to-Analog Converter                  | 48<br>49<br>51<br>52<br>56<br>56<br>56<br>57<br>61<br>63<br>64       |

| 3 | 3.1                | Capac<br>3.1.1<br>3.1.2<br>3.1.3<br>Switch<br>3.2.1 | itive and Radio-Frequency Digital-to-Analog Converter                  | 48<br>49<br>51<br>52<br>56<br>56<br>57<br>61<br>63<br>64<br>66       |

| 3 | 3.1                | Capac<br>3.1.1<br>3.1.2<br>3.1.3<br>Switch<br>3.2.1 | itive and Radio-Frequency Digital-to-Analog Converter                  | 48<br>49<br>51<br>52<br>56<br>56<br>57<br>61<br>63<br>64<br>66<br>66 |

|          |                      |        | 3.2.2.4 Validation                                          | 73  |  |  |

|----------|----------------------|--------|-------------------------------------------------------------|-----|--|--|

|          |                      | 3.2.3  | Power-Combiners for Highly-Mismatched Transformation Ratios | 75  |  |  |

|          |                      |        | 3.2.3.1 Series Power Combiner Circuit                       | 76  |  |  |

|          |                      |        | 3.2.3.2 Design Example                                      | 78  |  |  |

|          |                      |        | 3.2.3.3 Validation                                          | 82  |  |  |

| 4        | $\operatorname{Res}$ | ults   |                                                             | 88  |  |  |

|          | 4.1                  | Sampl  | es Description                                              | 88  |  |  |

|          |                      | 4.1.1  | Block Diagram of the Transmitter                            | 89  |  |  |

|          |                      | 4.1.2  | In-Die (a) and In-Package (b) Power Combiner                | 89  |  |  |

|          |                      | 4.1.3  | Die and Substrate Photographs                               | 97  |  |  |

|          |                      | 4.1.4  | Engineering Platform                                        | 98  |  |  |

|          | 4.2                  | Simula | ation Results                                               | 105 |  |  |

|          |                      | 4.2.1  | Continuous-wave Simulations                                 | 105 |  |  |

|          |                      | 4.2.2  | Envelope simulations                                        | 109 |  |  |

|          |                      | 4.2.3  | Simulations of System Performance                           | 112 |  |  |

|          | 4.3                  | Comp   | arison with the State-of-the Art                            | 114 |  |  |

| <b>5</b> | Con                  | clusio | ns                                                          | 119 |  |  |

| Li       | List of Publications |        |                                                             |     |  |  |

| Li       | st of                | Paten  | ts                                                          | 123 |  |  |

| Bi       | ibliog               | graphy |                                                             | 124 |  |  |

v

## Acknowledgments

The development of this Work comprised exciting discoveries, fascinating journeys into magnificent lands, but sometimes, as well, getting lost into the unknown. In these moments, everything seemed to be stuck, and lost, beyond recovery. It has taken courage to get through the shadows, making a way out to the lights. It has taken, as well, precious help from great people who shared their precious time and valuable experience.

I want to thank my supervisor, Andrea, who has been setting ambitious targets, and has been defending them throughout, helping me keeping focused. My mentor, Davide, who has been the first one to recognize and carry forward the potentials of this Work's findings, and Gerhard and Andreas, who have never stopped innovation, even when it seemed crazy that it could ever be possible to get through. I would like to thank Alan, who has cranked up all the pieces necessary to get the test-chip done, supported by Markus, Gerald, but also Blaz, Matvey, Dirk and Andrea. I thank Andreas, Ralf and Martin for all the patience in following mine, and Gracielle, crazy requests for the package. A thank you is needed to Christian and Saravana as well, who openly helped with measurements, simulations and in planning new developments. And I have to thank Edwin and Daniel, who have envisioned our test platform, in its digital and analog partitioning, and Michael and Franz, a reference amongst the many doubts. My thanks go as well to the number of people at Intel who have been bothered by myself during these time, a long list, including people coming from all over the world.

Furthermore, I want to thank Andrea, supervisor back at the time of my master thesis, who has believed in me for this opportunity, and Luca, my mentor at Canovatech, who started me to industrial microelectronics design, together with Alessandro and Nicola and the people at the company. A silent thank you to Aoki and Hajimiri for their precious articles, to Lee for his precious book, and to all who inspired. I would like to thank the people of ICARUS, Fabio and Alberto, and all those who are and have been part of the Lab, and all my friends in Villach, Padova, and Rovereto. Amongst friends I have to mention Marco, who kindly hosted me several times here in Padova, and Federico and Marco, in Rovereto. We have shared many visions together. Finally my thoughts go to Samantha and to my family. I guess, that sometimes they have not been seeing the path that I have been going through, but nonetheless they never discouraged me to get through.

## Abstract

The number of wireless devices has grown tremendously over the last decade. Great technology improvements and novel transceiver architectures and circuits have enabled an astonishingly expanding set of radio-frequency applications.

CMOS technology played a key role in enabling a large-scale diffusion of wireless devices due to its unique advantages in cost and integration. Novel digital-intensive transceivers have taken full advantage of CMOS technology scaling predicted by Moore's law. Die-shrinking has enabled ubiquitous diffusion of low-cost, small form factor and low power wireless devices.

However, Radio Frequency (RF) Power Amplifiers (PA) transceiver functionality is historically implemented in a module which is separated from the CMOS core of the transceiver. The PA is traditionally dictating power and battery life of the transceiver, thus justifying its implementation in a tailored technology. By contrast, a fully integrated CMOS transceiver with no external PA would hugely benefit in terms of reduced area and system complexity.

In this work, a fully integrated prototype of a Switched-Capacitor Power Amplifier (SCPA) has been implemented in a 28 nm CMOS technology. The SCPA provides the functionalities of a PA and of a Radio-Frequency Digital-to-Analog Converter (RF-DAC) in a monolithic CMOS device. The switching output stage of the SCPA enables this circuital topology to reach high efficiencies and offers excellent power handling capabilities. In this work, the properties of the SCPA are analyzed in an extensive and detailed dissertation.

Nowadays Wireless Communications operate in a very crowded spectrum, with strict coexistence requirements, thus demanding a strong linearity to the RF-DAC section of the SCPA. A great part of the work of designing a good SCPA is in fact designing a good RF-DAC. To enhance RF-DAC linearity, a precision of the timing of the elements up to the *ps* range is required. The use of a single core-supply voltage in the whole circuit including

the CMOS inverter of the switching output stage enables the use of minimum size devices, improving accuracy and speed in the timing of the elements.

The whole circuit operates therefore on low core-supply voltage. Throughout this work, a detailed analysis carefully describes the electromagnetic structures which maximize power and efficiency of low-voltage SCPAs.

Due to layout issues subsequent to limited available voltages, however, there is a practical limitation in the maximum achievable power of low-voltage SCPAs. In this work, a Multi-Port Monolithic Power Combiner (PC) is introduced to overcome this limitation and further enhance total achieved system power. The PC sums the power of a collection of SCPAs to a single output, allowing higher output powers at a high efficiency. Benefits, drawbacks and design of SCPA PCs are discussed in this work.

The implemented circuit features the combination of four differential SCPAs through a four-way monolithic PC and is simulated to obtain a maximum drain efficiency of 44% at a peak output power of  $29\,dBm$  on  $1.1\,V$  supply voltage. Extensive spectrum analysis offers full evaluation of system performances. After exploring state-of-the-art possibilities offered by an advanced  $28\,nm$  CMOS technology, this work predicts through rigorous theoretical analysis the expected evolution of SCPA performances with the scaling of CMOS Technologies. The encouraging forecast further emphasizes the importance of SCPA circuits for the future of high-performance Wireless Communications.

### Sommario

Il numero dei dispositivi senza fili è cresciuto esponenzialmente negli ultimi dieci anni. Grandi progressi tecnologici e nuove architetture di ricetrasmettitori hanno reso possibile un'impressionante insieme di applicazioni a radio-frequenza.

La tecnologia CMOS ha giocato un ruolo centrale nel rendere possibile una diffusione in larga scala di dispositivi senza fili grazie ai suoi esclusivi vantaggi in termini di costo e integrazione. Nuovi ricetrasmettitori marcatamente digitali hanno preso pieno vantaggio dell'evoluzione tecnologica prevista dalla legge di Moore. La riduzione della dimensione degli integrati microelettronici ha permesso una diffusione capillare di dispositivi senza fili a basso costo, di ridotte dimensioni e dal basso consumo.

D'altra parte, la funzionalità degli amplificatori di potenza (PA) per radio frequenza (RF) è storicamente implementata in un modulo che è separato dal nucleo CMOS del ricetrasmettitore. Il PA determina tradizionalmente la potenza e la durata della batteria del ricetrasmettitore, e per ciò è giustificata la sua implementazione in una tecnologia dedicata. All'opposto, un ricetrasmettitore CMOS pienamente integrato senza PA esterno beneficerebbe largamente in termini di riduzione di area e di complessità di sistema.

In questo lavoro, un prototipo completamente integrato di Amplificatore di Potenza a Capacità Commutate (SCPA) è stato implementato in una tecnologia CMOS a 28 nm. L'SCPA fornisce le funzionalità di un PA e di un Convertitore Digitale-Analogico in Radio Frequenza (RF-DAC) in un dispositivo CMOS monolitico. Lo stadio d'uscita commutato dell'SCPA rende questa topologia capace di raggiungere alte efficienze e offre un'eccellente capacità di generare potenza. In questo lavoro, le proprietà dell'SCPA sono analizzate in una discussione estensiva e dettagliata.

Le comunicazioni senza fili di oggi operano in uno spettro molto affollato, con requisiti

di coesistenza molto stretti, che quindi richiedono un'alta linearità alla sezione RF-DAC dell'SCPA. Una grande parte del lavoro di progetto di un SCPA è infatti progettare un buon RF-DAC. Per migliorare la linearità dell'RF-DAC, è richiesta una precisione della temporizzazione degli elementi fino all'ordine di grandezza dei *ps*. L'uso di una singola tensione di alimentazione, incluso l'invertitore CMOS dello stadio di uscita commutato, rende possibile l'uso di dispositivi di dimensione minima, migliorando l'accuratezza e la velocità della temporizzazione degli elementi.

L'intero circuito opera quindi su una bassa tensione di alimentazione. Nel corso di questo lavoro, un'analisi dettagliata descrive con attenzione le strutture elettromagnetiche che massimizzano la potenza e l'efficienza degli SCPA a bassa tensione.

A causa di problemi di maschere dovuti alle limitate tensioni disponibili, comunque, c'è una limitazione pratica nella massima potenza che un SCPA a bassa tensione può raggiungere. In questo lavoro, un Sommatore di Potenza Monolitico Multi-Porta (PC) è introdotto per superare questa limitazione e incrementare ulteriormente la potenza di sistema totale. Il PC somma la potenza di una collezione di SCPA in una singola uscita, rendendo possibili potenze più alte con un'alta efficienza. I benefici, i problemi e il progetto dei PC per SCPA sono discussi in questo lavoro.

Il circuito progettato comprende la combinazione di quattro SCPA attraverso un Sommatore di Potenza (PC) monolitico ed è simulato ottenere un'efficienza massima di collettore del 44 % con una potenza di picco di 29 dBm da una tensione di alimentazione di 1.1 V. Estensive analisi di spettro offrono una completa valutazione delle prestazioni di sistema. Dopo aver esplorato le prestazioni dello stato-dell'arte offerte da un'avanzata tecnologia CMOS a 28 nm, questo lavoro predice attraverso un'analisi teorica rigorosa l'evoluzione attesa delle prestazioni dell'SCPA con l'evoluzione delle tecnologie CMOS. L'incoraggiante previsione enfatizza ulteriormente l'importanza dei circuiti SCPA per il futuro delle comunicazioni senza fili ad alte prestazioni.

# List of Figures

| 1.1  | In-plane Wireless Connection deployment                                                                                                | 3  |

|------|----------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.1  | Means of encoding digital information into one carrier                                                                                 | 9  |

| 2.2  | Means of multiple access at one physical channel $\ \ldots \ $ | 10 |

| 2.3  | Means of duplexing transmission and reception through TDD $\ldots$                                                                     | 11 |

| 2.4  | Means of duplexing transmission and reception through FDD $\ldots$                                                                     | 12 |

| 2.5  | Carrier-Aggregation (CA)                                                                                                               | 12 |

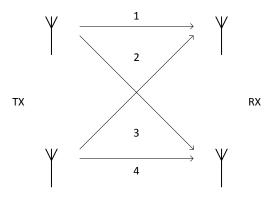

| 2.6  | Multiple-Inputs Multiple-Outputs (MIMO)                                                                                                | 13 |

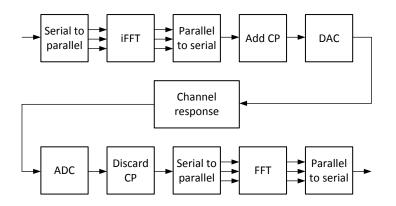

| 2.7  | Orthogonal-Frequency Division (OFDM) System                                                                                            | 13 |

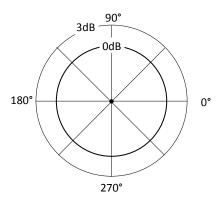

| 2.8  | Half-Wave Dipole Antenna Radiation Pattern                                                                                             | 15 |

| 2.9  | Magnitude of the trajectory of an IEEE 802.11 Signal                                                                                   | 16 |

| 2.10 | Cumulative distribution function of an IEEE 802.11 Signal $\hdots$                                                                     | 17 |

| 2.11 | Partial Trajectory of an IEEE 802.11 Signal                                                                                            | 18 |

| 2.12 | ETSI 300 328 Unwanted Spectrum Emissions Limits                                                                                        | 21 |

| 2.13 | IEEE 802 11 Unwanted Spectrum Emissions Limits                                                                                         | 22 |

| 2.14 | Impulse Response                                                                                                                       | 23 |

| 2.15 | Frequency Response                                                                                                                     | 24 |

| 2.16 | Quantization of an Analog Signal                                                                                                       | 25 |

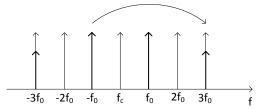

| 2.17 | Third-order Harmonics of a Sine-Wave centered at $f_c$                                                                                 | 28 |

| 2.18 | Reference clock phase-noise                                                                                                            | 29 |

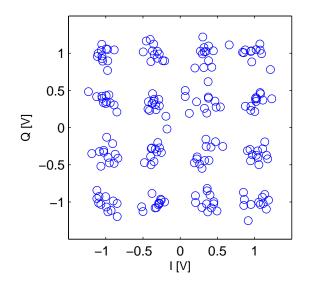

| 2.19 | Noisy Constellation                                                                                                                    | 32 |

| 2.20 | Degradation of Signal Quality by Harmonic Distortion                                                                                   | 34 |

| 2.21 | Coexistence                                                                                                                            | 38 |

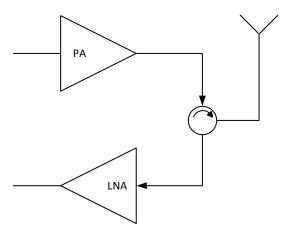

| 2.22 | Analog Intensive Architecture                                                                         | 39 |

|------|-------------------------------------------------------------------------------------------------------|----|

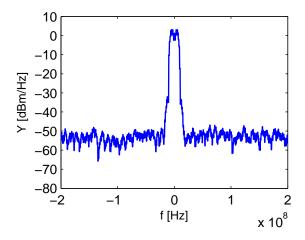

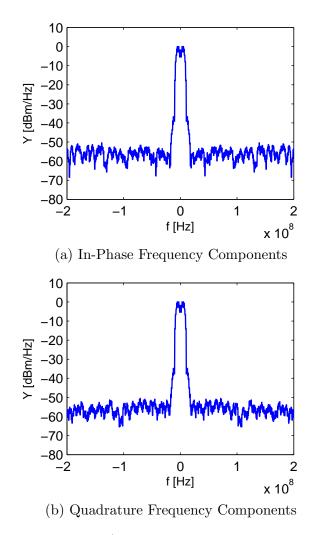

| 2.23 | Absolute Value of Signal Frequency Components                                                         | 41 |

| 2.24 | Polar Digital-Intensive Architecture                                                                  | 42 |

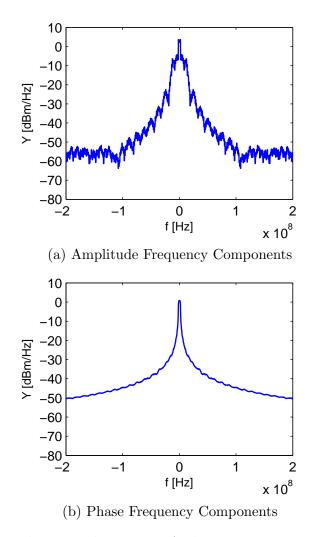

| 2.25 | Polar Digital-Intensive Architecture Frequency Components                                             | 44 |

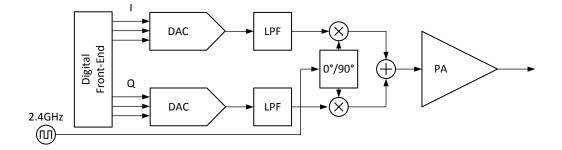

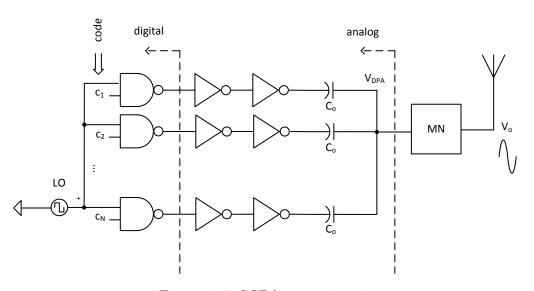

| 2.26 | Digital I/Q Architecture                                                                              | 45 |

| 2.27 | Digital I/Q Architecture Frequency Components                                                         | 47 |

| 3.1  | Capacitive Digital-to-Analog Converter                                                                | 49 |

| 3.2  | Radio-Frequency Capacitive Digital-to-Analog Converter                                                | 51 |

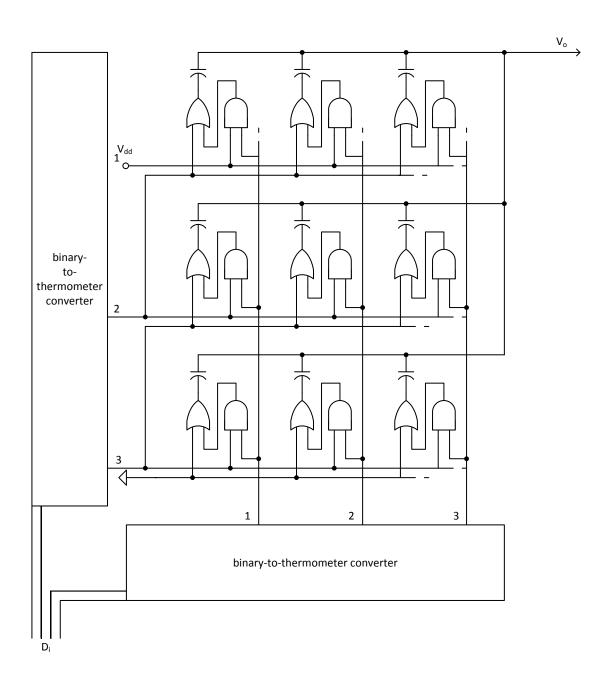

| 3.3  | Thermometric Array                                                                                    | 54 |

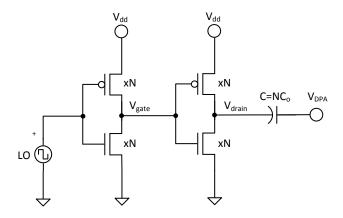

| 3.4  | SCPA array circuit                                                                                    | 58 |

| 3.5  | SCPA equivalent full scale circuit                                                                    | 58 |

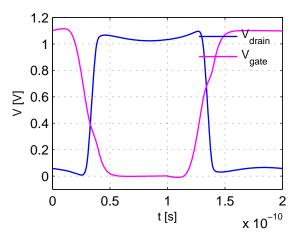

| 3.6  | Output $MOSFETs$ drain voltage at LO operating frequency of $5GHz$                                    | 59 |

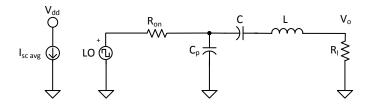

| 3.7  | Linear model of the SCPA at full scale                                                                | 59 |

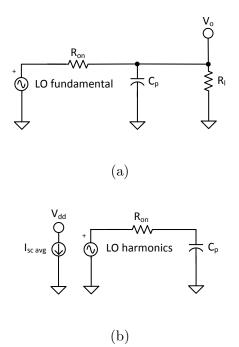

| 3.8  | Equivalent circuit models for the fundamental and the harmonics $\ldots \ldots \ldots$                | 60 |

| 3.9  | Load pull analysis to find the optimal load for a fixed source $\ldots \ldots \ldots \ldots$          | 61 |

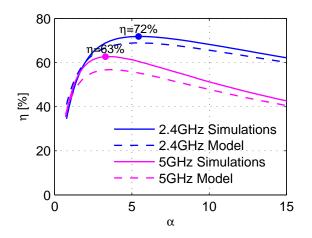

| 3.10 | Comparison between linear model and $SpectreRF$ simulations                                           | 64 |

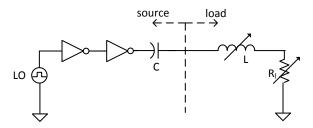

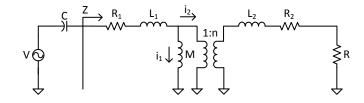

| 3.11 | Simplified Full-Scale Model of SCPA as shown in Sec. 3.2.1 $[1]$                                      | 67 |

| 3.12 | Equivalent Single-Ended Circuit of the SCPA                                                           | 67 |

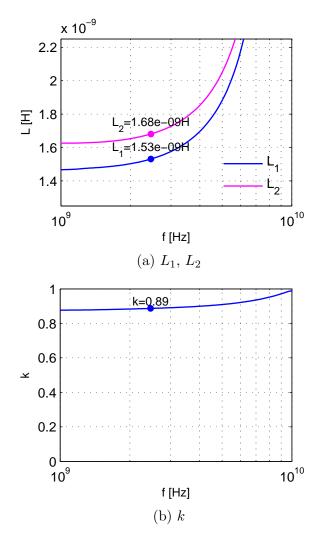

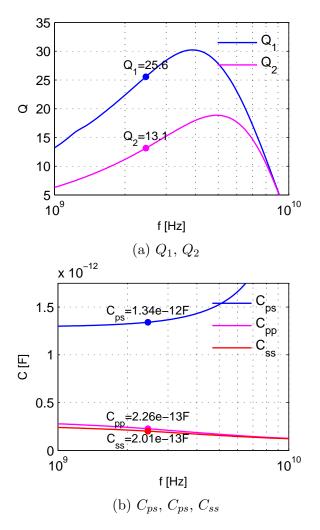

| 3.13 | Model plots for typical RF stack quality and coupling factor $\ldots \ldots \ldots \ldots$            | 70 |

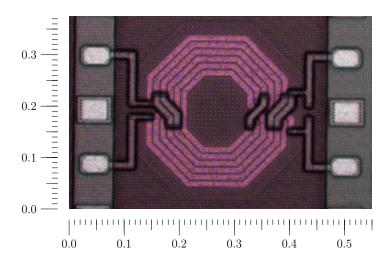

| 3.14 | Design Choices with $Q_1 = Q_2 = 15$ and $k = 0.75$                                                   | 71 |

| 3.15 | Die photo of the fabricated $16.7 dBm$ transformer $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 72 |

| 3.16 | Maximum efficiency of third-order matching networks                                                   | 73 |

| 3.17 | Measured Output Power and IL of Structure I $\ldots$                                                  | 74 |

| 3.18 | Series Power Combiner Circuit                                                                         | 77 |

| 3.19 | Equivalent Circuit Transformation.                                                                    | 79 |

| 3.20 | Impedance Levels as a function of Number of Combined Circuits (N) $\ . \ . \ .$ .                     | 80 |

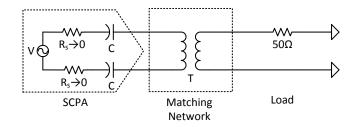

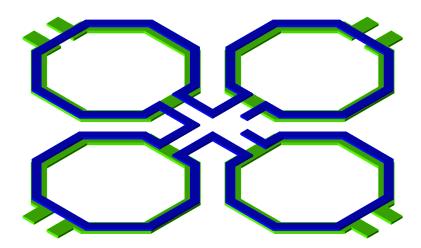

| 3.21 | Overall Circuit                                                                                       | 81 |

| 3.22 | Overall Impedance Transformation on the Smith Chart                                                   | 83 |

| 3.23 | Designed $1:50\Omega$ Power Combiner                                                                  | 84 |

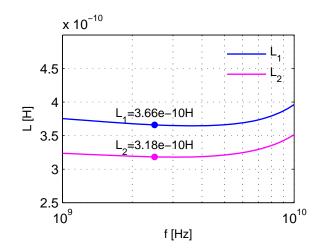

| 3.24 | Inductances and coupling factors                                                                      | 85 |

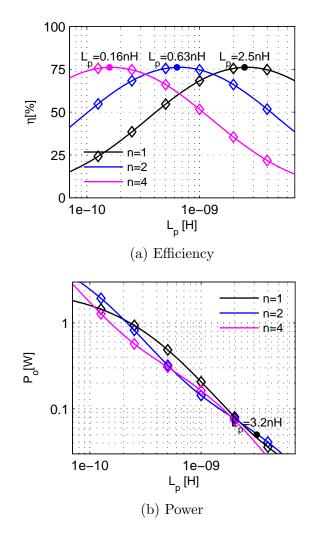

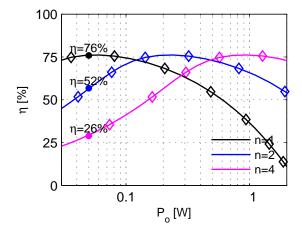

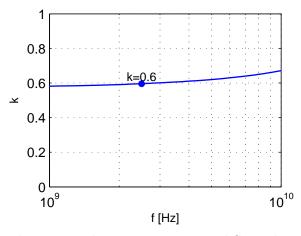

| 3.25 | Evaluation of the Parasitics of the Combiner                                                       | 86  |

|------|----------------------------------------------------------------------------------------------------|-----|

| 3.26 | Simulated Output Power and Efficiency                                                              | 87  |

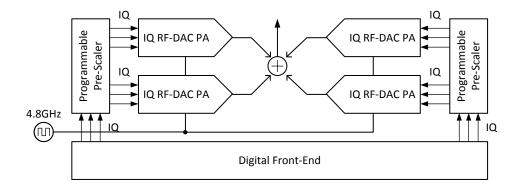

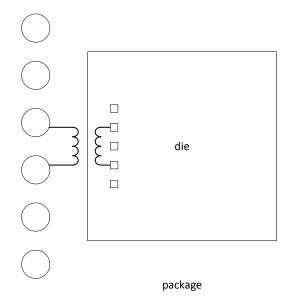

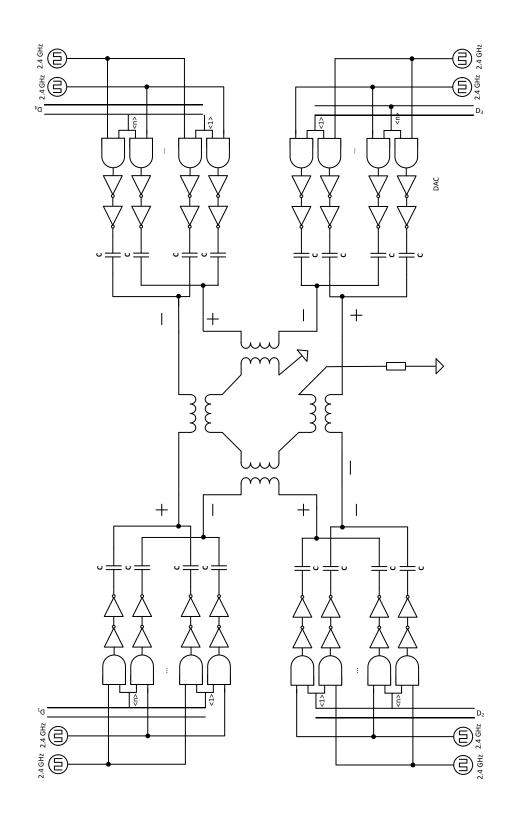

| 4.1  | System                                                                                             | 90  |

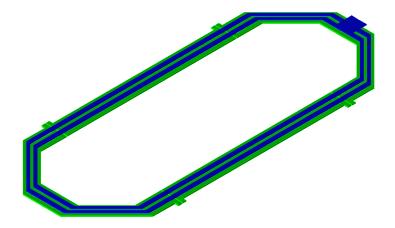

| 4.2  | Three-Dimensional View of the Combiner-in-die                                                      | 91  |

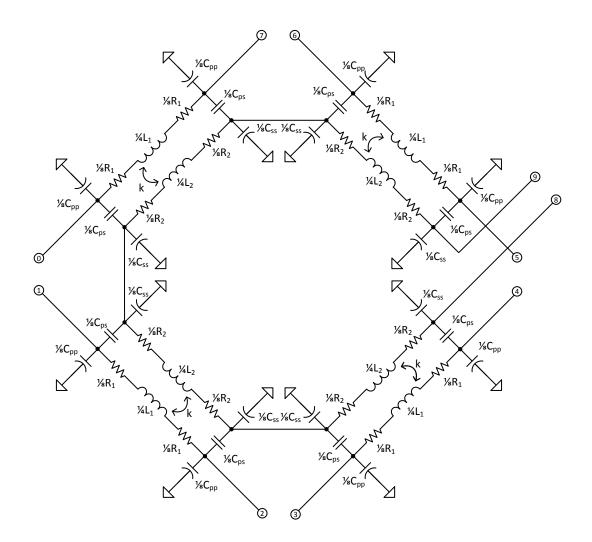

| 4.3  | Symmetrical model of the power combiner, where $R_1 = \omega L_1/Q_1$ and $R_2 = \omega L_2/Q_2$ . | 92  |

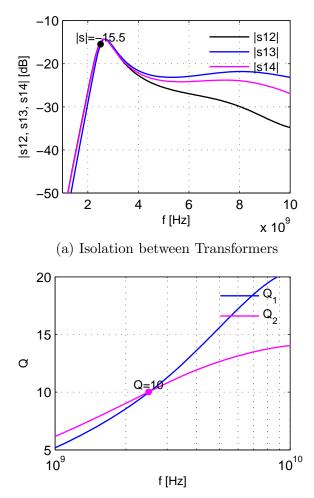

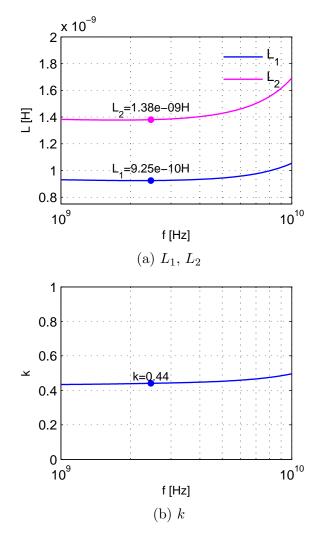

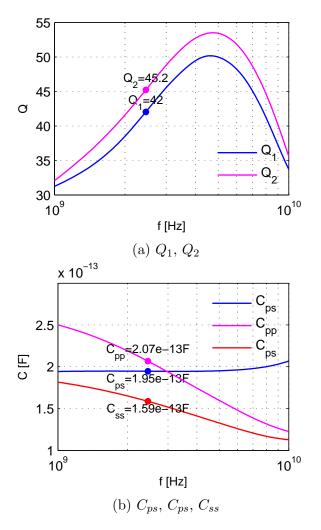

| 4.4  | Characterization of the combiner-in-die                                                            | 93  |

| 4.5  | Characterization of parasitics of the combiner-in-die                                              | 94  |

| 4.6  | Implementation of in-package passives                                                              | 95  |

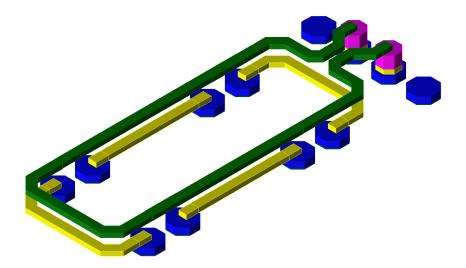

| 4.7  | Three-Dimensional View of the Combiner-in-package                                                  | 96  |

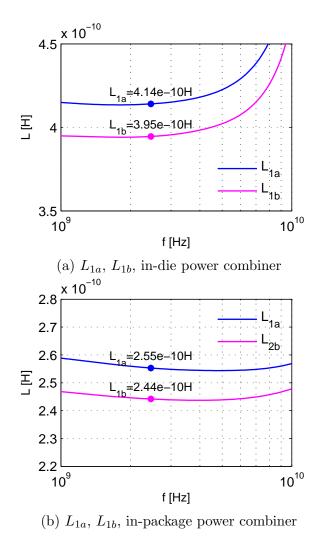

| 4.8  | Characterization of the combiner-in-package                                                        | 97  |

| 4.9  | Characterization of parasitics of the combiner-in-package                                          | 98  |

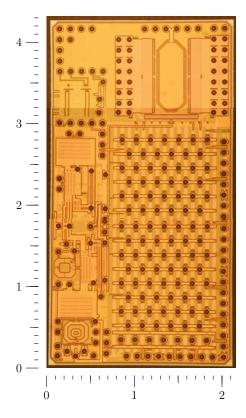

| 4.10 |                                                                                                    | 99  |

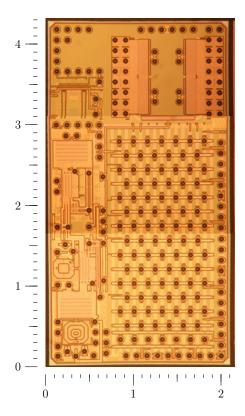

|      | ATELP Die with Combiner-in-die                                                                     | 100 |

|      | ATETP Die with Combiner-in-packag                                                                  | 101 |

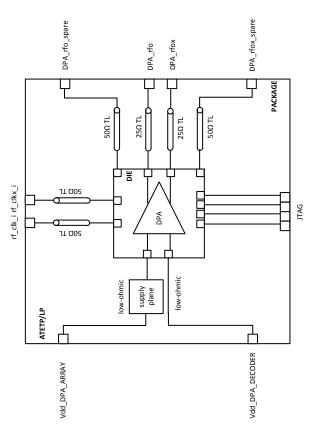

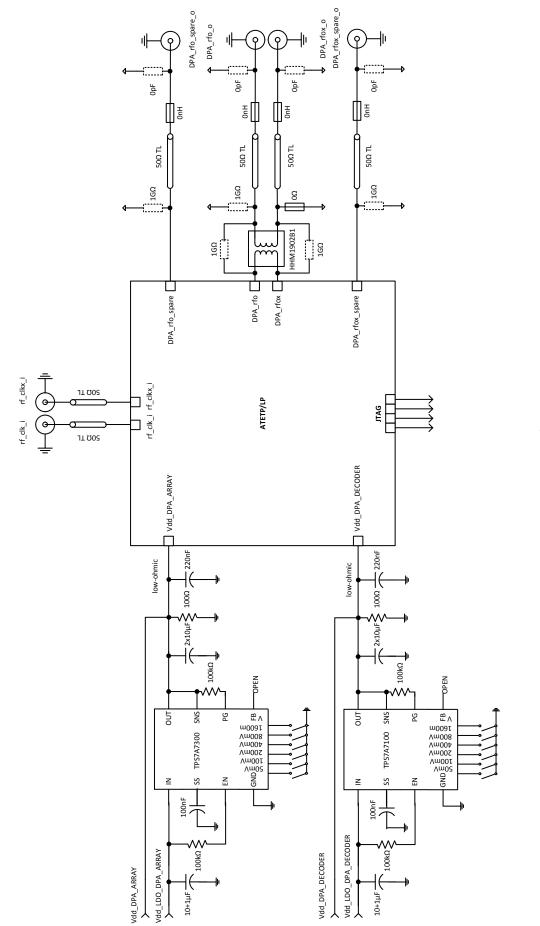

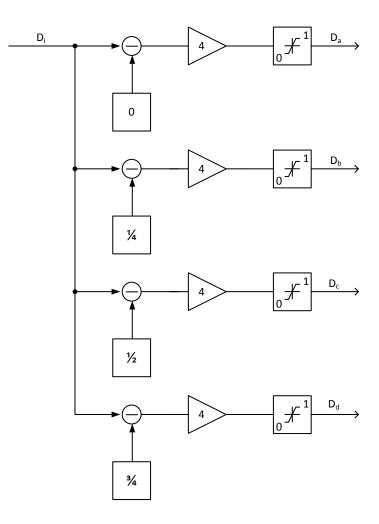

|      | ATETP/LP DPA Circuit                                                                               | 102 |

|      | ATETP/LP Package                                                                                   | 103 |

|      | ATETP/LP Board                                                                                     | 104 |

|      | ATETP implemented combiner-in-package                                                              | 105 |

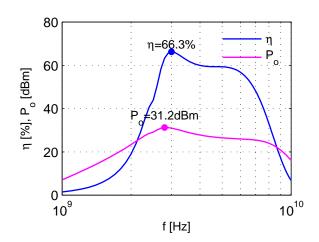

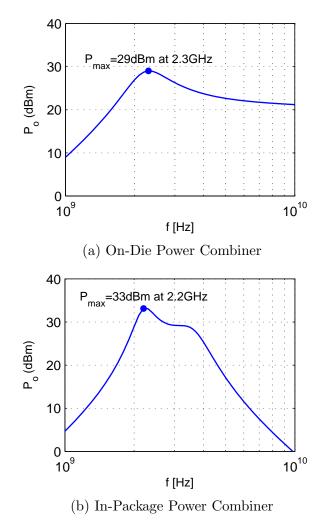

|      | Continuous-wave Simulations, Power                                                                 | 106 |

| 4.18 |                                                                                                    | 107 |

| 4.19 | Continuous-wave Simulations, Drain Efficiency                                                      | 108 |

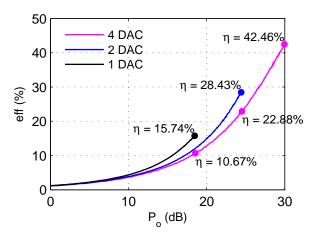

|      | Envelope Simulations                                                                               | 110 |

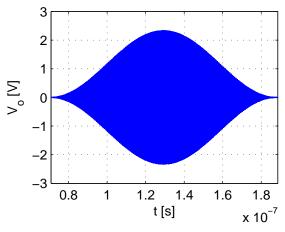

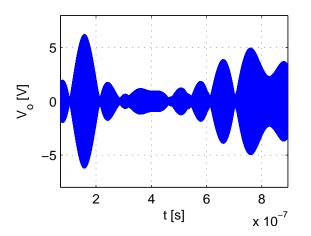

| 4.21 | Envelope while transmitting a $20MHz$ signal                                                       | 112 |

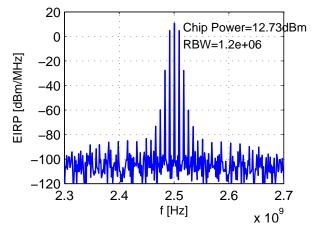

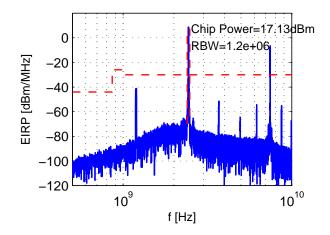

| 4.22 | Close-in spectrum while transmitting a $20MHz$ signal                                              | 113 |

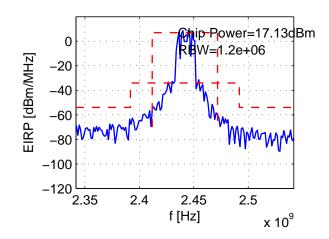

| 4.23 | Far-off spectrum while transmitting a $20MHz$ signal                                               | 113 |

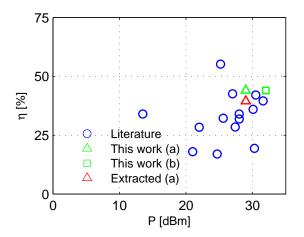

|      | Power and Efficiency of the State-of-the-art and of this Work                                      | 115 |

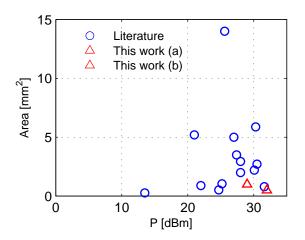

| 4.25 | Power and Area of the State-of-the-art and of this Work                                            | 116 |

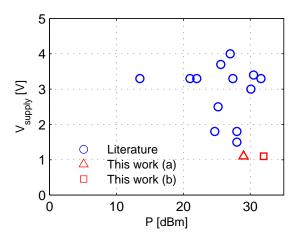

| 4.26 | Power and Supply Voltage of the State-of-the-art and of this Work                                  | 117 |

# List of Tables

| 1.1 | Wireless LAN Throughput by IEEE Standard                                              | 4   |

|-----|---------------------------------------------------------------------------------------|-----|

| 2.1 | Transmitter limits for spurious emissions                                             | 20  |

| 2.2 | Allowed relative constellation error versus constellation size and coding rate $\ $ . | 32  |

| 2.3 | Evolved Universal Terrestrial Radio Access (E-UTRA) operating bands [4] $\ . \ .$     | 36  |

| 3.1 | Comparison of Maximum Efficiency in Model and Simulations                             | 65  |

| 3.2 | Measured Test Structures at frequency $f$                                             | 75  |

| 4.1 | Sinusouidal Envelope                                                                  | 111 |

| 4.2 | Counter-Inter Modulation (CIM) Products                                               | 112 |

| 4.3 | Extracted and Schematic Comparison of Simulation Results                              | 117 |

## List of Symbols and Abbreviations

AM/AM Amplitude-to-Amplitude

AM/PM Amplitude-to-Phase

C-DAC Capacitive Digital-to-Analog Converter

CA Carrier Aggregation

CDMA Code-Division Multiple Access

CIM Counter Inter-Modulation

DAB Digital-Audio Broadcast

DAC Digital-to-Analog Converter

DCO Digital Control Oscillator

DFE Digital Front-End

- DNL Differential-non-Linearity

- DPA Digital Power-Amplifier

DPD Digital Pre-Distortion

- DPLL Digital Phase-Locked Loop

- DSB Double-Sided Bandwidth

- DVB Digital-Video Broadcast

- EDA Electronic design automation

- EM Electro-Magnetic

- EN European Standard

- ETSI European Telecommunications Standards Institute

- EVM Error-Vector Magnitude

- FCC Federal Communications Commission

- FDD Frequency Division Multiplex

- FFT Fast-Fourier Transform

- FM Frequency Modulation

- FOM Figure-of-merit

- I/Q In-Phase and Quadrature-Phase

- IEEE Institute of Electrical and Electronics Engineers

- IFFT Inverse Fast-Fourier Transform

- INL Integral-non-Linearity

- IOT Internet Of Things

- JTAG Joint Test Action Group

- KPI Key-Performance Indicator

- LAN Local-Area Network

- LDO Low-Dropout Voltage Regulator

- LTE Long-Term Evolution

- MIC Japan Ministry of Internal Affairs and Communications

- MIMO Multiple-Input Multiple-Output

- OFDM Orthogonal Frequency Division Multiplex

- PA Power Amplifier

- PSD Power Spectral Density

- PSK Phase-Shift Keying

- PSRR Power-Supply-Rejection-Ratio

- QAM Quadrature-Amplitude Modulation

- RF-DAC Radio-Frequency Digital-to-Analog Converter

- SCPA Switched-Capacitor Power Amplifier

- SNR Signal-to-Noise Ratio

- SSB Single-Sided Bandwidth

- TDC Time-to-Digital Converter

- TDD Time Division Duplex

### Chapter 1

## Introduction

Past and future development trends of Wireless Communications, the broad adoption of Wireless Technologies and the important minimum requirements mandatory for safe operation of Wireless devices are the key elements which are described throughout the Introduction of this Work. At first, an historical *excursus* identifies the origin of IEEE 802.11 standard popularly known, as, Wireless. Subsequently, facts concerning the diffusion of Wireless Communications remark a broad, and growing, world-wide adoption of the Technology. Next, present and future evolution of the Technology, including novel target applications, are discussed. Finally, the origin of the minimum requirements set by the law for safe operation of Wireless devices are tracked back to their essential motivations.

### 1.1 Growth of Wireless Communications

In 1990, a new committee under the IEEE organization, called IEEE 802.11, was set up to look into getting an open standard started [5]. A decision in 1985 by the United States Federal Communications Commission (FCC), in fact, opened several bands of the wireless spectrum for use without a government license. These so-called "garbage bands" were allocated to equipment such as microwave ovens which use radio waves to heat food [6].

The standard was published seven years later, in 1997. However, demand for wireless devices was so high by the time, that devices adhering to the new standard were already shipping by then. IEEE 802.11 standard defines an over-the-air interface between a wireless client and a base station (or access point), or between two or more wireless clients. IEEE 802.11 is inherently compatible with 802 networks, specifically with the 802.3 wired Ethernet networks. In fact, and perhaps a cornerstone of the success for the standard, the 802.11 address space allows 802.11 networks to interact with the original 802.1 Local-Area-Network (LAN) specification that provides for bridging between separate physical networks. Accordingly, Wireless devices can operate seamlessly together with their wired counterpart.

As capabilities were are added over the years to the IEEE 802.11, some become known by the name of the amendment, such as IEEE 802.11b, IEEE 802.11g and IEEE 802.11n. Each of these amendments defines a maximum speed of operation, the radio frequency band of operation, how data is encoded for transmission, and the transmitter and receiver features. The amendments to which a device adheres are referred to in a sequential manner, for example 802.11 b/g/n indicates that a device can operate against amendment b, g and n of IEEE 802.11.

Lately, IEEE 802.11 standard, which celebrated its first 25 years in 2015, is so widely diffused that it is usually thought as a synonymous of Wireless LAN in general. Subsequently, IEEE 802.11 standard is colloquially simply referred to as "Wireless". For simplicity, the keyword Wireless, with capital letter, is then sometime used for referring to IEEE 802.11 throughout the entire scope of this Work as well.

#### 1.2 Ubiquitous Diffusion

As already hinted in the previous section, the diffusion of Wireless Technologies is remarkable. Evidences of ubiquitous Wireless Diffusion, include

• Large wireless diffusion in private households, i.e. to semi-static contexts. Worldwide home network penetration is expected to climb up from 24.8% in 2013 to 33.2% by 2018. I.e., in the present, one out of four inhabitants of the planet have access to a Wireless Network at home, and this ratio is expected to climb up to one over three in the near future. Growth is being driven by the continued spread of broadband services and demand for multi-screen video services. Wireless is seen as commonplace in mature

Figure 1.1: In-plane Wireless Connections have been lately deployed by all major airlines companies and are available, while flying, on selected airplanes

markets, including server provided broadband routers with integrated Wireless access points. [7]

- Wild diffusion of Wireless in hotels, i.e. to users on-the-go. 57%, i.e. over one half of all European hotels offer nowadays a Wireless connection to guests. Wireless is greatly appreciated by guests, and sometime even a deal breaker, for example, a report from Forrester Consulting discovered that more than 90% of business travelers, i.e. the vast majority, wanted Wireless in their room, and for a third it was a deal breaker without it they would not return. [8]

- Major airlines companies offering the possibility to subscribe an in-flight Wireless service on selected planes, i.e. diffusion of Wireless in technologically-challenging environments, as per Fig. 1.1. For example, the three leading American airlines companies including American Airlines Group, Delta Air Lines and United Continental Holdings offer in-flight wireless connections, and, in Europe, the two leading airlines companies, such as Lufthansa and Airfrance-KLM offer in-flight wireless connection on selected planes. The number of airline companies offering this possibility has been rapidly expanding over the years.

Similar statistics can be obtained about any other facility where users are likely to stay with a laptop, including, airports, cafes, libraries and public spots, with the notable exception of Hospital. However, Wireless connection could get into Hospitals as well. In fact, free

| WLAN<br>Standard | MIMO<br>streams,<br>Bandwidth   | Operating<br>Frequency               | Single-User<br>Throughput |  |

|------------------|---------------------------------|--------------------------------------|---------------------------|--|

| IEEE 802.11b     | 1x20MHz                         | 2.4GHz                               | 11 Mbit/s                 |  |

| IEEE 802.11g     | 1x20MHz                         | 2.4GHz                               | 54 Mbit/s                 |  |

| IEEE 802.11n     | $1 \mathrm{x40MHz}$             | $2.4 \mathrm{GHz}, 5.4 \mathrm{GHz}$ | $150 \mathrm{Mbit/s}$     |  |

|                  | 4x40MHz                         | $2.4 \mathrm{GHz}, 5.4 \mathrm{GHz}$ | $600 \mathrm{Mbit/s}$     |  |

| IEEE 802.11ac    | $1 \mathrm{x} 160 \mathrm{MHz}$ | 5.4GHz                               | 867 Mbit/s                |  |

|                  | 4x160MHz                        | 5.4GHz                               | $3.47 \mathrm{Gbit/s}$    |  |

| IEEE 802.11ad    | 1x2.16GHz                       | $60 \mathrm{GHz}$                    | $6.757 \mathrm{Gbit/s}$   |  |

Table 1.1: Wireless LAN Throughput by IEEE Standard

Wireless in the Hospitals would allow patient hospitalized for long periods of time, to keepup with their daily life, for example, to keep updated with their businesses, or, for kids, to keep up with their school classes.

#### **1.3** Standard Development

Whilst 802.11 standard is originally intended to provide a Wireless Local-Area Network access, IEEE 802.11ad extends the purpose of the wireless link to novel applications. For instance, a primary target for IEEE 802.11ad is streaming HD video. For example, a person could bring a laptop into a room and have it automatically linked wirelessly to a large display, digital projector and/or storage system to stream video or data. [9]

However, IEEE 802.11ad provides a viable solution delivering high speeds for applications requiring just a few meters of transmission [9], in fact, IEEE 802.11ad compatible APs are able to cover not much more than a room. Communication in the 60 GHz range are in fact not as robust as those used in previous standards. Should the high-speed connection be lost for any reason, devices will fall back to 2.4 GHz and 5 GHz signals to continue communications without interruptions. For aforementioned motivations, critical for future Wi-Fi adapters is to support both IEEE 802.11ad and IEEE 802.11 previous standards,

backwards.

The deployment of novel Wi-Fi transceivers requires thus the integration of a high number of circuits, for delivering all standards required. Beside implementing circuits enabling new standards, it is then as well critical to innovate circuits implementing legacy standards, so that they can be implemented in a smaller area and at a high efficiency, enabling future devices offering interoperability to a large number of standards to be small and slim regardless on their functionalities.

#### **1.4 Mandatory Requirements**

Importantly, for a Wireless transceiver being allowed to operate, it is required, not to harm human health, neither for the active user of the transceiver, nor for other people staying nearby, and not to disturb other transceivers operating in other frequency bands. Minimum requirements are set so that safety of health, and of communications are met.

Any transmitter operating in the European region shall adhere European Telecommunications Standards Institute (ETSI) requirements [10]. Other world regions are governed by Federal Communications Commission (FCC), Japan Ministry of Internal Affairs and Communications (MIC) and Korean Standard. Technical requirements are described in the following-chapter, with a particular focus for ETSI standard, since this Work has been developed in the European Union. It is important to notice that, for the legislator, the fact that the transceiver is, or is not, able to communicate with the others, is irrelevant. In fact, the effectiveness of the wireless transmission is not ruled by the ETSI, which is concerned about safety of health and of the communications.

In order not to harm human health, transmitters are only allowed to operate below a certain maximum power level. As a general principle, an idea behind the specification of the maximum power level is that, a transmitter which could harm human health produces a potentially-harming field F which is inversely proportional to the square of the distance d, and directly proportional to the transmitted power P,

$$F \propto \frac{P}{d^2} \tag{1.1}$$

therefore, the farther a human body is located from a transmitter, the lower the potentially harmful field to the body. Therefore, devices which are supposed to be kept i.e. by hand, are subject to severe laws, limiting maximum transmittable power and thus maximum operating range, whilst, i.e. TV broadcasting antenna towers, high-on-the-ground and far from any urban environment are allowed to transmit at a much higher power level, and offer larger operating ranges.

Next, it is in the legislator interest to ensure that licensed band operations are not harmed by unlicensed band transmitter. In fact, it is important to keep in mind that, to be awarded the permission to operate in the licensed frequencies, big operators, such as Radio and Video broadcasters and Mobile operators, have to pay an important fee, and that, even more critical, certain frequencies are of crucial importance for the state itself, i.e., are allocated for the military forces.

To ensure safety and pacific inter-operations of the totality of deployed transceivers, every transceiver which is directly available on the market to a final consumer, has to undergo a certification process, ensuring that it is safe for health and that it does not disturb any other licensed transceivers.

### Chapter 2

## System Analysis

This part of the Work describes a Wireless Transmitter System and the Standards and Technical Specifications which the System has to fulfill. At first, an introductory section mentions the Standards which are relevant to a Wireless Transmitter. With the knowledge of the Standards, and of ETSI and IEEE Technical Documentations, important metrics of the Transmitter are reviewed, including Peak Power, Unwanted Emission Spectrum, and Error-Vector Magnitude. The major System non-idealities contributors to these Transmitter metrics, including Supply Noise, Spectral Images, Quantization Noise, Harmonic Distortion and Phase Noise are then analyzed. Next, after a read-through of in-device Receiver Desensitization Issue, a Survey of Transmitter Architectures is proposed. Thread-offs of Classical and Evolved Transmitter Architectures are analyzed, and finally, the proposed Digital I/Q Architecture is chosen due to its superior Modulated Bandwidth Performance.

### 2.1 Relevant Standards

The vast majority of Radio-Frequency Communications are either digital already or slowly transitioning towards digital domain, with the last notable example of analog transmission found in the FM radio, which is anyhow slowly fading towards digital-audio-broadcast (DAB) as well. Television, which used to rely on analog communications not long ago, has recently undergone an evolution towards digital-video-broadcast (DVB). Therefore, during any evolved Radio-Frequency Communication, digital symbols are being transmitted all the time. The air is but always a physical object, therefore, before transmission, digital signal are always converted to an analog counterpart. Analog symbols are then transmitted through the air, and converted back to their digital counterparts at the receiver side. There are many ways into which the digital information can be encoded into analog symbols.

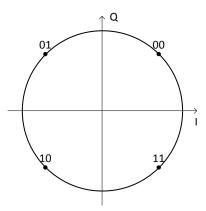

In the case, for example, in which the radio link includes a carrier being transmitted at a fixed frequency from a Transmitter to a Receiver, the amplitude of the carrier can be varied over time, in a discrete manner, to encode many different digital symbols. Or, alternatively, the phase of the carrier can be modulated, in a discrete manner, to differently encode many digital symbols (PSK). Most notably, if the information of a symbol is encoded in a combination of both phase and amplitude modulation of a carrier, the System operates a Quadrature-Amplitude-Modulation (QAM), as in Fig. 2.1. [11]

Digital systems are extremely sensitive to noise in the digital domain. A single wrong bit in a long sequence of words can invalidate a whole content transferred Wirelessly. Immunity to interferences is therefore critical and immunity in the digital domain is improved by adding redundancy to the transmitted information. By means of redundant codes, it is possible to identify and even correct errors (i.e., Hamming Distance), or automatically request for a new copy in case of invalidated contents. Since typical RF interferers are narrow-band and have a short time-duration, Orthogonal-Frequency Division Multiplexing (OFDM), as in Fig. 2.2b, encoding is a good way to resist interferers. A temporary interfering spur typically invalidates only a small offsets of frequencies, making therefore possible for standards where each frequency bin represent one symbol only, to guarantee that in the transmitted symbol only few bits are wrong. Such an error is even recovered directly through forward error correction techniques, since it is an invalidation of only one little part of the stream, making the narrow-band interferer irrelevant to the correct radio-device link operation. Beside, since OFDM encodes information into a large set of sub-carriers, a way to maximize spectral efficiency is provided.

To enable simultaneous connection between many devices and avoiding large interferences between simultaneously operating Transceivers, the whole spectrum is divided in channels. These channels can be assigned permanently to a single link between devices, dynamically assigned at the beginning of the device connections, or, such as in Bluetooth Devices, con-

|           | /         | Q         |      |        |

|-----------|-----------|-----------|------|--------|

| 0000      | 0001      | 0010      | 0011 |        |

| 0100      | 0101<br>• | 0110<br>• | 0111 | ,      |

| 1000<br>• | 1001<br>• | 1010      | 1011 | →<br>I |

| 1100<br>• | 1101<br>• | 1110<br>• | 1111 |        |

|           |           |           |      |        |

(a) 16-QAM, Constellation Diagram

(b) 4-PSK, Constellation Diagram

Figure 2.1: Means of encoding digital information into one carrier

tinuously re-assigned during transmission (frequency hopping).

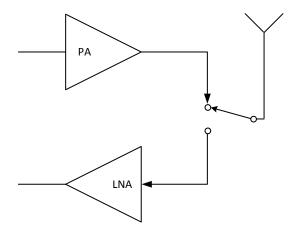

Many applications require to enable simultaneous Transmission and Reception of data between devices. With a unique channel being assigned, one could assign the channel for Transmission at a certain moment, and switch it to Reception subsequently. This method, which requires accurate synchronization between receiver and transmitter, providing a halfduplex transmission rate, is called Time-Domain-Division (TDD) and is depicted in Fig. 2.3. Alternately, for full-duplex transmissions, one channel is dedicated for Transmission and another channel for Reception. In Frequency-Domain-Division (FDD), a particular care

(a) Code-Division Multiple Access (CDMA)

(b) Orthogonal-Frequency Division Multiple Access (OFDM)Figure 2.2: Means of multiple access at one physical channel

has to be given to avoid the generated spectrum to couple between the Transmitter and received channel at the Receiver, which would result in a decreased receiver sensitivity. In fact, in FDD both receiver and transmitter are active at the same time as shown in Fig. 2.4.

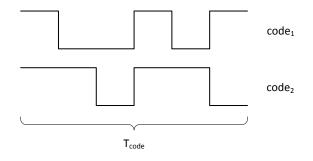

In some cases, many devices can transmit and receive at the same time on the same channel. In CDMA standard, as in Fig. 2.2a, i.e., one transceiver always operates on codes which are orthogonal to the codes operated by other transceivers. This way, all transceivers can operate a the same time on the same channel. By contrast, in Orthogonal-Frequency-Division-Modulation (OFDM) channel division, the orthogonality between the transceivers is obtained by allocating different sub-carriers within the channel bandwidth to each of the users of the channel. Each transceiver operates then on an assigned subset of the available carriers which is orthogonal to the subset assigned to other transceivers, and therefore

multiple transceivers can operate at the same time on the same channel. OFDM as a way to split a channel to multiple users, requires spurious emissions of the Transmitters to be low enough not hurt adjacent subcarriers of other Transmitters. Since guaranteeing such an orthogonality is a challenging topic, CDMA, where orthogonality is instead obtained in the time-domain has often been preferred for Wireless and Mobile Communications.

(a) Time Division Multiplex (TDD)

(b) Time Division Duplex. Either Transmitter or receiver are active at once.

Figure 2.3: Means of duplexing transmission and reception through TDD

Modern communications techniques include as well Carrier-Aggregation (CA), Fig. 2.5, standards where many channels are employed at the same time for one link, improving overall Transmission and Reception throughput. Furthermore, lately, multiple-input-multipleoutput (MIMO) transceivers have been introduced, empowered by multiple, spatially separated, independently driven antennas. MIMO transceivers feature higher spectral efficiency compared to single-antenna systems, and can route optimal channels even in case of poor line-of-sight visibility or of crowded spectrum by means of constructive/disruptive interfer-

(a) Frequency Division Multiplex (FDD)

(b) Frequency Division Duplex. Transmitter and receiver are both active at the same time. Figure 2.4: Means of duplexing transmission and reception through FDD

Figure 2.5: Carrier-Aggregation (CA)

ence with the environment building up diverse transmissions paths.

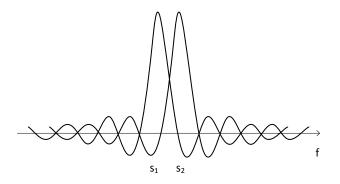

A practical implementation of the OFDM transceiver concept already described before, is provided in Fig. 2.7. The standard is particularly relevant to Wireless Communications, since by means of orthogonal-frequency division multiplexing (OFDM) the allocated channel is divided in a collection of sub-carriers, improving spectral efficiency and providing resilience

Figure 2.6: Multiple-Inputs Multiple-Outputs (MIMO)

Figure 2.7: Orthogonal-Frequency Division (OFDM) System

to interferes, which easily crowd the Wireless frequencies spectrum. The Transmitter System comprises a scheme where,

- Digital information is encoded into QAM symbols

- QAM symbols are grouped to form OFDM subcarriers, through IFFT

- Cyclic Prefix is added to avoid Inter-Symbol-Interference (ISI)

consequently, and in the opposite order, the Receiver rejects the Cyclic Prefix and QAM symbols are reconstructed through FFT.

### 2.2 Maximum Radiated Power

The European Telecommunications Standards Institute (ETSI) is an European Standards Organization, which produces standards to support European regulation and legislation. By adhering to these standards, manufacturers and service providers can claim 'presumption of conformity' with the essential requirements of a directive by self-declaration. Rather than having to go through costly type approval processes in different Members States, by respecting ETSI standards, manufacturers and service providers safely ensure that their devices operate in conformity with applicable regulations.

#### 2.2.1 Equivalent Isotropic Radiated Power

ETSI EN 300 328 V1.9.1 Harmonized European Standard (EN) [12] is the reference for Wide Band Data Transmission equipments such as IEEE 802.11<sup>TM</sup> RLANs, Bluetooth® Wireless Technologies, Zigbee<sup>TM</sup>, etc. capable of operating in the band 2.4*GHz* to 2.4835*GHz*. The document describes requirements for RF output power, defined as the mean equivalent isotropic radiated power (EIRP), of aforementioned equipments that typically operate on a fixed frequency, during a transmission burst. To comply with the European Standard, RF output power of devices operating under these conditions shall not exceed (clause 4.3.2.2.3) 20dBm, for any combination of power level and intended antenna assembly.

Equivalent isotropic radiated power, referred to by the EN as RF output power, is the power that a theoretical isotropic antenna, evenly distributing power in all directions, would radiate to produce the peak power density observed in the particular direction of maximum antenna gain. For the same transmit power, in fact, different antenna types have different radiation patterns, with a higher field being radiated in some directions compared to other directions, i.e., antennas which are directional enhance the radiated field in some directions and weaken it in some others. In the direction where the field is enhanced, a higher power is measured when a directional antenna is operated compared to that which would be radiated in the that direction by an isotropic antenna.

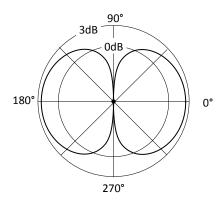

The simplest and most widely used antenna, the dipole, has a radiation pattern which covers  $360^{\circ}$  uniformly on the horizontal plane, and has a direction of zero gain (node) at  $\pm 90^{\circ}$

(a) Horizonal Radiation Pattern

(b) Vertical Radiation Pattern

Figure 2.8: Half-Wave Dipole Antenna Radiation Pattern

on the vertical plane. A half-wave dipole is typically chosen for Wireless Communications, due to its smaller size compared to the dipole antenna. Physical size of the a half-wave dipole antenna  $l_h$  is in fact half the size of a dipole antenna for the same frequency, namely

$$l_h = \frac{1}{2}\lambda = \frac{1}{2}\frac{c}{f} = \frac{1}{2}12.5cm$$

(2.1)

Radiation patter of the half-wave dipole antenna is shown in Fig. 2.8. Fig. 2.8a shows that horizontal radiation pattern of a half-wave dipole antenna is isotropic. Vertical radiation pattern of Fig. 2.8b, instead, exhibits a direction of maximum power, where power is 2.15 dBi.

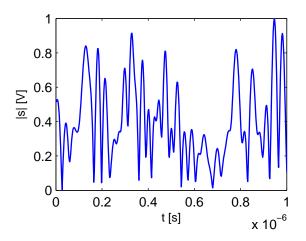

Figure 2.9: Magnitude of the trajectory of an IEEE 802.11 Signal

Therefore, combining horizontal and vertical radiation patterns, overall antenna gain of the half-wave dipole antenna is observed to be 2.15 dBi.

To improve the coverage range of a transceiver, i.e. the maximum distance at which a link is available, the receiver is designed for low-noise and high-sensitivity and the transmitter is designed to have high-power and low error-vector-magnitude. The maximum RF power which can be allowed at the RF transmitter output connector is therefore transmitted, and since

$$EIRP = P_{RF} + G_{antenna}[dB]$$

(2.2)

the maximum power results  $P_{RF} \approx 17.85 dBm$ .

#### 2.2.2 Peak-to-Average Power Ratio

High-speed IEEE 802.11 standards encode information in a number of OFDM sub-carriers within the transmitted spectrum, tightly spaced one another, as shown in Fig. 2.2b. Each sub-carrier's amplitude and phase information resemble a fragment of the information which is being transmitted, encoded i.e. with a QAM modulation. A time-domain signal is obtained through Inverse-Fast-Fourier Transform (IFFT) from the OFDM signal. Amplitude and phase of the transmitted signal vary over time resembling the desired OFDM signal frequency content.

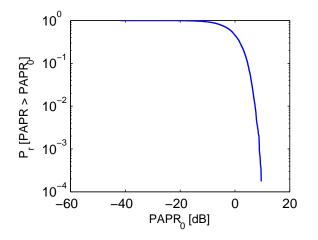

Figure 2.10: Cumulative distribution function of an IEEE 802.11 Signal

The trajectory of a high-speed IEEE 802.11 signal, as per Fig. 2.9, contains symbols whose magnitude can be subsequently large and small in magnitude. Over time, the signal exhibits therefore a peak-to-average ratio (PAPR); i.e., the maximum magnitude of transmitted symbols is higher than the average transmitted symbol magnitude. Namely,

$$PAPR = \frac{\max\left(P\right)}{\frac{1}{T}\int P \cdot dt}$$

(2.3)

usually expressed in decibel. ETSI EN 300 328 V1.9.1 Harmonized European Standard claims (clause 4.3.2.4.3) that RF output power is the highest average equivalent isotropic radiated power measured on any 10ms or less Tx-sequence. A 10ms Tx-sequence contains a large number of subsequent transmitted symbols. As shown in Fig. 2.9, a large number of symbols is in fact already observed in a  $1\mu s$  Tx-sequence.

The theoretical PAPR of an OFDM signal with n uncorrelated sub-carriers is [13]  $PAPR = 10 \log(n) + CFc$  where CFc is the crest factor (in dB) for each sub-carrier. CFc is 3.01dB for the sine waves used for BPSK and QPSK modulation. A signal spanning over a 20MHz channel, composed by BPSK and QPSK subcarriers spaced 312.5 KHz apart, having 64 sub-carriers, exhibits a theoretical PAPR exceeding 21dB.

Due to the large-value of the theoretical PAPR, a complementary cumulative distribution function (CCDF) of the PAPR is usually introduced [14]. In fact, it is observed that it is

Figure 2.11: Partial Trajectory of an IEEE 802.11 Signal

possible to highly reduce the PAPR by clipping each signal exceeding a practical threshold, with a probability of error  $P_r < 10^{-4}$ . This reduces the clipped PAPR of a high-speed IEEE 802.11 signal to a value in the range of PAPR = 12dB. The clipped PAPR is then subsequently diminished by means of a PAPR reduction techniques (i.e., Clipping and Filtering, Coding, PTS, SLM, Interleaving, TR, TI and ACE [14]) to a reduced value of i.e. PAPR = 9.6dB with a probability of error  $P_r < 10^{-4}$ , Fig. 2.10.

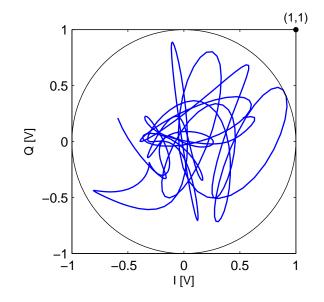

#### 2.2.3 Constellation Power

IEEE 802.11 standards require high modulation bandwidths, with IEEE 802.11n requiring up to 40Mhz base-band signal bandwidth. Due to superior modulation bandwidth performance, as describe in Section 2.6, designed system employs of a Digital I/Q RF architecture. A Digital I/Q RF Transmitter directly generates antenna signal by summing up two vectors, one in-phase with the RF clock and one in-quadrature with the RF clock. Each of the vector amplitude is controlled individually through a digital code.

Fig. 2.11 presents the trajectory of a IEEE 802.11 Signal on an I/Q Diagram. The trajectory can be circumscribed by a circle whose ray is equal to  $P_{trajectory} = P_{RF} - G_{antenna} + G_{antenna}$

*PAPR*, normalized to 1*V* in Fig. 2.11. However, none of the points inside the circle of ray  $P_{trajectory}$  ever reaches the maximum power which a Digital I/Q RF Transmitter can generate. In fact, point (1*V*, 1*V*), see Fig. 2.11, does not belong inside the  $P_{trajectory}$  circle, and the normalized voltage of point (1*V*, 1*V*) is  $\sqrt{1^2 + 1^2}V = \sqrt{2}V$ . The maximum power generated by a Direct I/Q RF Transmitter is therefore  $20 \log \sqrt{2} = 3dB$  above the power of the points within the circle defined by  $P_{trajectory}$ .

#### 2.2.4 Total Radiated Power

Recalling previously defined figures, maximum RF power which is instantaneously generated by the Transmitter for a high-speed IEEE 802.11 2.4GHz standard is, therefore,

$$P_t = P_{RF} - G_{antenna} + PAPR + P_{constellation}$$

=20dBm - 3dB + 9.6dB + 2.15dB \approx 29dBm (2.4)

Losses in the system, such as cable losses, board losses, package losses, variations due to temperature, aging and process, degrade overall antenna radiated power. However this particular  $P_t$  specification ensures that, regardless of the entity of the unknown system losses, the system is safe to operate, with an output power which is not exceeding *ETSI* Harmonized European Standard Recommendations.

#### 2.3 Unwanted Emissions

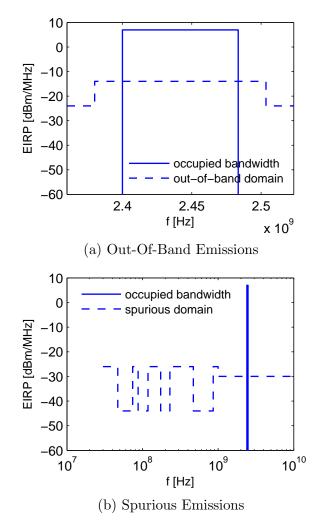

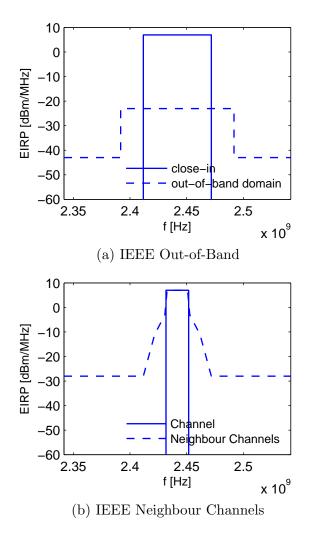

A Wireless Device does not only radiate useful power, but does also radiate power outside its channel bandwidth. ETSI EN 300 328 V1.9.1 Harmonized European Standard (EN) [12] specifies the level of the unwanted emissions outside the 2.4GHz to 2.4835GHz operating band, discerning between the out-of-band domain and the spurious domain of unwanted spectral emissions. IEEE 802.11 regulates then unwanted emissions within the 2.4GHz to 2.4835GHz operating band, to the neighbor channel domain, to ensure the coexistence of multiple channels within allowed operating band as shown in Table 2.1 and Fig. 2.13.

| Frequency range                           | Maximum power | Bandwidth           |  |

|-------------------------------------------|---------------|---------------------|--|

| 30 MHz to 47 MHz                          | -36 dBm       | 100 kHz             |  |

| $47~\mathrm{MHz}$ to $74~\mathrm{MHz}$    | -54 dBm       | 100  kHz            |  |

| $74~\mathrm{MHz}$ to $87,5~\mathrm{MHz}$  | -36  dBm      | $100 \mathrm{~kHz}$ |  |

| $87,5~\mathrm{MHz}$ to $118~\mathrm{MHz}$ | -54  dBm      | $100 \mathrm{~kHz}$ |  |

| $118~\mathrm{MHz}$ to $174~\mathrm{MHz}$  | -36  dBm      | $100 \mathrm{~kHz}$ |  |

| $174~\mathrm{MHz}$ to $230~\mathrm{MHz}$  | -54  dBm      | 100  kHz            |  |

| $230~\mathrm{MHz}$ to $470~\mathrm{MHz}$  | -36  dBm      | 100  kHz            |  |

| $470~\mathrm{MHz}$ to $862~\mathrm{MHz}$  | -54  dBm      | $100 \mathrm{~kHz}$ |  |

| $862~\mathrm{MHz}$ to $1~\mathrm{GHz}$    | -36  dBm      | $100 \mathrm{~kHz}$ |  |

| $1~\mathrm{GHz}$ to 12,75 GHz             | -30 dBm       | 1 MHz               |  |

Table 2.1: Transmitter limits for spurious emissions

### 2.3.1 Supply-Noise

A Low-Dropout Voltage Regulator (LDO) typically regulates the supply voltage of the System to a constant voltage reference. On-board DC/DC converter generating low core-supply voltage used in the system introduces, in fact, tones at its switching frequency, which then the LDO removes through its voltage drop on its series path on the supply. The LDO rejects therefore supply noise and generates a new reference with its own noise spectral content, usually specified in terms of  $\mu V/\sqrt{Hz}$  for a given output voltage, i.e. below  $0.1\mu V/\sqrt{Hz}$  in the voltages and bands of interest. [15]

Supply noise translates then to load noise through Power-Supply-Rejection-Ratio (PSRR) of the System. PSRR of an RF-DAC System Architecture is, in this case, a moderate gain. On average, in fact, it is observed that out of the 1.1V supply voltage, 17dBm of output power is generated on  $50\Omega$  load, i.e.

$$V_{rms} = \sqrt{PR} \tag{2.5}$$

therefore, to deliver 50mW load output power, 1.58Vrms are generated on a  $50\Omega$  load

Figure 2.12: ETSI 300 328 Unwanted Spectrum Emissions Limits, Fixed Transmission Frequency, 20MHz Channel Bandwidth

resistance. Ratio between supply and output voltage is 1.43; i.e. any noise with power level P on the supply is translated to a noise with power level  $P[dB]+20 \log (1.43) = P+3dB$  on the output. The matching network introduces an attenuation outside channel frequencies, but no active feedback mechanism attenuates noise from the supply in the capacitive RF-DAC open-loop design described in Sec. 3 for in-band components.

Output spectral noise contribution from the LDO is calculated to be below

$$P = 20\log(0.1\mu V/\sqrt{Hz}) + 3dB = -137dB/Hz$$

(2.6)

Figure 2.13: IEEE 802 11 Unwanted Spectrum Emissions Limits, Fixed Transmission Frequency, 20MHz Channel Bandwidth

which reads -107dBm/Hz, or -47dBm/MHz on ETSI EN 300 328 and IEEE 802.11 spectral mask, and therefore within specifications. For the lower part of the spectrum, i.e., for the part of the spectrum which goes from DC to 1GHz, the attenuation introduced by the matching network is more pronounced, further helping the design achieving target specifications.

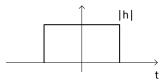

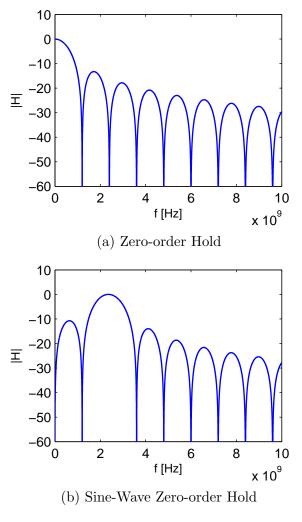

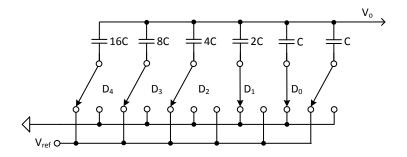

## 2.3.2 Spectral Images

A zero-order hold Digital-to-Analog Converter (DAC) such as i.e. that of Fig. 3.1, reconstructs digital input to an analog signal with a rectangular reconstruction filter as in Fig. 2.14a. The analog equivalent of digital input signal is held for the time a sample lasts, before the next sample is introduced.

(a) Zero-order Hold

(b) Sine-Wave Zero-order Hold

Figure 2.14: Impulse Response

$$x(t) = \sum_{n=-\infty}^{+\infty} x[n] \cdot rect\left(\frac{t-nT_s}{T_s} - \frac{1}{2}\right)$$

(2.7)

and

$$h_{ZOH}(t) = \frac{1}{T_s} rect \left(\frac{t}{T_s} - \frac{1}{2}\right)$$

$$H_{ZOH}(f) = e^{-i\pi fT_s} sinc(fT_s)$$

(2.8)

Transfer function of zero-order hold reconstruction filter is shown in Fig. 2.15a.

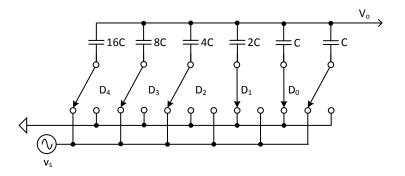

Instead, a Radio-Frequency DAC (RF-DAC), such as i.e. that of Fig. 3.2, ideally produces for each digital sample a sine-wave whose amplitude corresponds to the analog equiv-

Figure 2.15: Frequency Response

alent of the digital input signal as in Fig. 2.14b. The sine-wave is then held for one sample, before the next sample is introduced.

$$x(t) = \sum_{n=-\infty}^{+\infty} x[n] \cdot \sin(2\pi \frac{t - nT_s}{T_{RF}}) \cdot rect\left(\frac{t - nT_s}{T_s} - \frac{1}{2}\right)$$

(2.9)

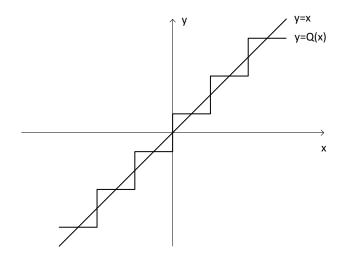

Figure 2.16: Quantization of an Analog Signal

and

$$h_{ZOH}(t) = \sin\left(2\pi \frac{t - nT_{RF}}{T_s}\right) \cdot \frac{1}{T} rect\left(\frac{t}{T_s} - \frac{1}{2}\right)$$

$$= a(t) \cdot b(t)$$

$$H_{ZOH}(f) = (A * B)(f)$$

$$= \int \left[\delta(f - u + f_{RF}) + \delta(f - u - f_{RF})\right] e^{-i\pi u T_s} sinc(uT_s) \cdot du$$

$$= e^{-i\pi (f - f_{RF})T_s} sinc\left[(f - f_{RF})T_s\right] + e^{-i\pi (f + f_{RF})T_s} sinc\left[(f + f_{RF})T_s\right]$$

(2.10)

The transfer function of sine-wave zero-order hold reconstruction filter is shown in Fig. 2.15b. The main lobe is centered at radio-frequency  $f_{RF}$ , and the first zero of the sinc appears at  $f_{RF} - f_s$  and then at  $f_{RF} + f_s$ . Images of the reconstructed signal are generated at frequencies which are integer multiples of  $f_s$ , i.e.  $kf_s$ . Therefore the strongest spectral component is at  $f_{RF}$ , where a replica of the desired signal appears unattenuated.

Undesired replicas of the signal, located at  $kf_s$ , are attenuated by the zero of the sinc function. For signals with a small bandwidth, all replicas are hugely attenuate. For signal with larger signal bandwidth, however, spectral images attenuation is limited, with a minimum attenuation  $\alpha$  at the edge of the signal bandwidth, centered at image frequency, i.e.  $f_{edge} = f_{RF} - BW/2$ , being,

$$\alpha = 20 \log \left[ \left( e^{-i\pi f_{edge}T_s} + e^{-i\pi f_{edge}T_s} \right) sinc\left( f_{edge}T_s \right) \right]$$

(2.11)

For example, a signal with BW = 20MHz, where  $f_{RF} = 2.4GHz$  and  $f_s = 1.2GHz$ has a minimum attenuation  $\alpha = -40dB$ . The attenuation is enough to meet ETSI 300 328 masks. Signal power, measured to be 7dBm/MHz in the channel bandwidth, attenuated by 40dB drops to -33dBm/MHz, meeting the spurious-domain specifications at 1.2GHz and at further images frequencies.

## 2.3.3 Quantization Noise

The uniform quantization of the digital signal operated at the digital-to-analog converter introduces a noise, whose power is uniform over the quantization interval  $-\Delta/2$  to  $+\Delta/2$ . Its integral yields

$$\sigma^2 = \frac{\Delta^2}{12} \tag{2.12}$$

while signal power for full-scale sinusoidal-signal is

$$\sigma_{signal}^2 = \left(\frac{2^N}{\sqrt{2}}\Delta\right)^2 \tag{2.13}$$

signal-to-noise ratio (SNR) of the quantized signal, when N bits are employed for quantization thus with a peak signal power of, is therefore

$$SNR = 1.76 + 6.02 \cdot N[dB] \tag{2.14}$$

When transmitting an OFDM signal, however, PAPR and  $P_{constellation}$  decrease signal power with respect to full-scale sinusoidal-signal power, of a factor  $PAPR + P_{Constellation}$ . Furthermore, quantization noise is spread over whole Nyquist Bandwidth, i.e.

$$P_{noise}[dBm/MHz] = P_{signal}[dBm/MHz] - SNR - 10 \cdot \log(f_{Nyquist}[MHz]) + PAPR + P_{constellation}$$

$$= 6dBm/Hz - 62dB + 9.6dB + 2.15dB - 30dB \approx -74dBm/Hz$$

(2.15)

for N = 10 thermometric bits.  $P_{Noise}$  stays therefore within ETSI EN 300 328 requirements for the whole spectrum with the proposed number of thermometric bits in example.

## 2.3.4 Harmonic Distortion

The Amplitude-to-Amplitude (AM/AM) static distortion characterizes the digital-to-analog converter relationship between input-referred voltage, which is linear to digital-code amplitude, and the output voltage, measured at the output. The output voltage of a RF-DAC, is defined as the amplitude of the fundamental-tone measured on the output. Since the measure is static, after changing input-referred voltage, enough time is allowed for the output to settle before measuring the output voltage. Integral-non-linearity (INL) and differentialnon-linearity (DNL) are derived out of AM/AM characterization of the circuit.

AM/AM curve can be often approximated by a polynomial equation, i.e.

$$y = x + \alpha x^2 + \beta x^3 \tag{2.16}$$

where if  $\alpha = 0$  and  $\beta = 0$  the AM/AM relationship of an ideal DAC if found, where output voltage is perfectly linear to the input-referred voltage. When, for example,  $\beta = 0$ and  $\alpha \neq 0$ , a sinusoidal tone at the input of the circuit is distorted to

$$y = \sin(\omega t) - \alpha \sin(\omega t)^{2}$$

=  $\sin(\omega t) - \frac{\alpha}{2} [1 - \cos(2\omega t)]$  (2.17)

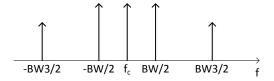

and a tone with frequency  $2\omega$  is appearing in the spectrum. In the specific case of the RF-DAC, the sum of many sinusoidal tones, building up the OFDM base-band spectrum, is shifted at frequency  $f_c$ , and then undergoes a high-order polynomial distortion. In particular, the third-order distortion of a sine-wave tone at frequency  $\omega_2$  mixed with a tone at frequency

Figure 2.17: Third-order Harmonics of a Sine-Wave centered at  $f_c$

$\omega_1$  introduces tones at frequencies  $\omega_1 \pm \omega_2$ ,  $\omega_1 \pm 3\omega_2$ ,  $3\omega_1 \pm \omega_2$  and  $3\omega_1 \pm 3\omega_2$ , with a spectrum which resembles that of Fig. 2.17,

In a modulated signal, a tone at the edge of the bandwidth BW, i.e. at frequency  $f_c - BW/2$ , produces a harmonic tone at  $f_c - BW \cdot 3/2$ . Furthermore, all tones between  $f_c \pm BW/2$  produce harmonic tones between  $f_c \pm BW \cdot 1/2$  and  $f_c \pm BW \cdot 3/2$ . The distance between  $f_c \pm BW \cdot 3/2$  and  $f_c \pm BW/2$  is BW, so that all close-in third-harmonics intermodulation products fall within ETSI 300 328 out-of-band emissions specifications, which have to be met when both first or last channels within ISM bandwidth are selected. The distance measured between in-band and out-of-band power on Fig. 2.12a is 21*dB*, therefore this is the maximum level of *CIM*3 which can be allowed.

In case CIM3 is too high, with respect to achieved system performance, a Digital Pre-Distortion (DPD) algorithm can reduce the amount of second and higher-order distortion with a counter-equalization curve. However, the presence of hysteresis in the distortion could require a very complex and computation-intensive algorithm, and in general degrade SNR performance of the system, therefore the level of inter-modulation products should be kept as low as possible.

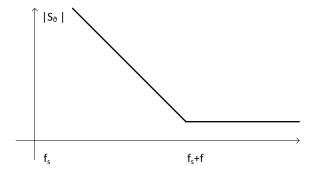

#### 2.3.5 Phase Noise

Active and passive devices in the signal chain of the System introduce thermal noise which sums up to other circuit's noise sources. The analog signal is generated at the node where the digital-input code is converted to an analog voltage, by means of switching as many cells from  $V_{ss}$  to  $V_{dd}$  as required, as described in Sec. 3.1. The impact of noise introduced by active devices, when operated in linear region, i.e. when operating as a clamp, is limited. By

Figure 2.18: Reference clock phase-noise

contrast most of the noise accumulates during switching activities, in terms of phase noise, translating into an uncertainty in RF-DAC clock timing, i.e. jitter.

A detail explanation of off-band phase-noise of over-sampled DAC systems can be found in [16]. Formally, given the signal at the output of the DAC,

$$S_{output}(\omega) = \frac{1}{T} \frac{4sin^2 \left(\frac{\omega T}{2}\right)}{\omega^2} S_{baseband}(\omega)$$

(2.18)

noise spectral density is calculated by means of a convolution of the spectral noise of the clock at  $f_{sample}$  with the signal itself, i.e.

$$S_{noise}(\omega) = \frac{1}{T} \left[ \frac{4sin^2 \left(\frac{\omega T}{2}\right)}{\omega^2} S_{baseband}(\omega) * \frac{\omega^2}{f_{sample}^2} S_{phase \ noise} \right]$$

(2.19)

therefore, for a single tone signal (i.e.,  $A_i \cos \omega_i t$ ), phase noise error becomes

$$S_{noise}(\omega) = \frac{1}{T} \left[ \frac{4sin^2 \left(\frac{\omega T}{2}\right)}{\omega^2} \frac{\pi A_i^2}{2} \left(\delta(\omega - \omega_i) + \delta(\omega + \omega_i)\right)(\omega) * \frac{\omega^2}{f_{clock}^2} S_{phase \ noise} \right]$$

(2.20)

$$= \frac{1}{T} \frac{4sin^2 \left(\frac{\omega T}{2}\right)}{\omega^2} \frac{\pi A_i^2}{2} \frac{\omega^2}{f_{clock}^2} \left[ \left(S_{phase \ noise}(\omega - \omega_i) + S_{phase \ noise}(\omega + \omega_i)\right) \right]$$

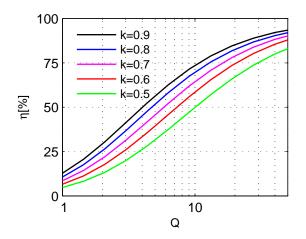

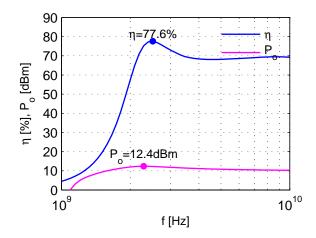

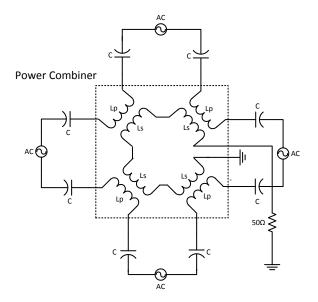

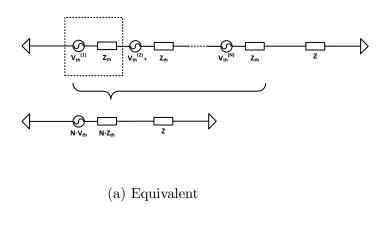

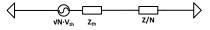

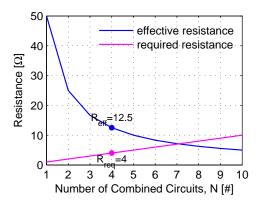

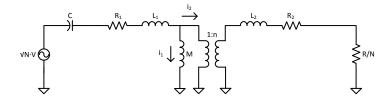

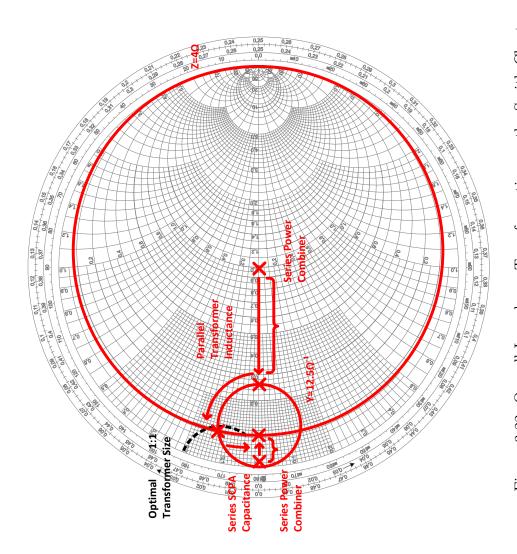

and