## UNIVERSITÀ DEGLI STUDI DI PADOVA Dipartimento di Fisica e Astronomia "Galileo Galilei"

PH.D. COURSE IN PHYSYCS

DOCTORAL THESIS

# Innovative readout architecture for Monolithic Active Pixel Sensors

**Ph.D. school coordinator:** PROF. GIULIO MONACO **Supervisor:** PROF. PIERO GIUBILATO

**Ph.D. student:** Davide Chiappara 1229775

#### Abstract

Particle tracking plays an important role in many fields, from fundamental High Energy Physics research performed in the experimental halls at CERN, to the latest medical imaging equipment for the treatment of cancer; from industrial cameras used to spot manufacturing defects, to space telescopes used to study the universe. In the technology of particle tracking, the leading role belongs to silicon sensors, which over the last decades have improved performance with respect to all key metrics: high spatial and timing resolution, low power consumption, low material budget, decreasing production and exercise costs, and high adaptability to several tracking contexts. In particular, Monolithic Active Pixel Sensors (MAPS), which embed in the same silicon die both the sensor and the signal handling electronics, are the latest incarnation of the silicon sensor paradigm, and they show great potentialities to further advance the state-of-the-art in particle tracking.

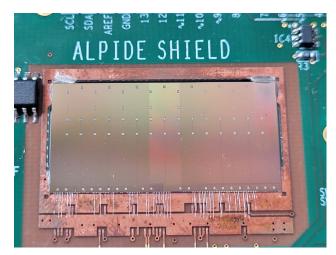

Currently there are many MAPS developments in the worldwide scientific and industrial communities. The ARCADIA collaboration of the National Institute for Nuclear Physics (INFN) aims to develop a MAPS tailored towards large-area and low-power tracking applications. The ARCADIA sensor design is inspired by the ALPIDE sensor, a MAPS developed by the CERN ALICE collaboration which is the current benchmark for monolithic tracking pixel detectors.

This thesis first briefly introduces the overall development of ARCADIA sensor, and then it details the implementation of the experiment-driven readout, describes validation tests, and reports on a preliminary campaign of displacement damage dose effects performed to verify the sensor durability in a harsh environment.

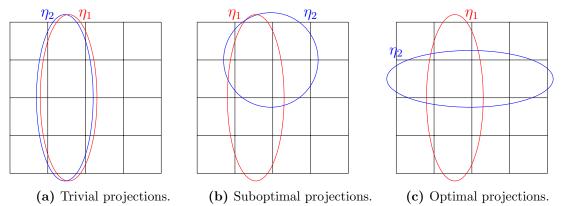

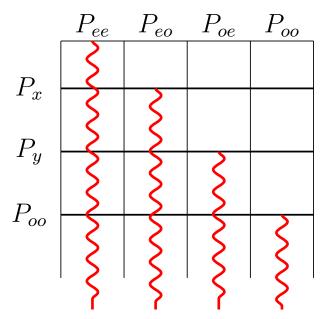

Moreover, a very innovative readout architecture relying on an alternative approach for MAPS readout is discussed, with the intent of developing a sensor suitable for extreme-low power applications (such as for outer space applications). The idea takes advantage of several projections on different axes to reconstruct the addresses of the hits; this approach is made possible by data sparsification in the targeted applications. This architecture is ready at a digital electronics level and its performance has been evaluated both with a mathematical approach, using a specifically developed formalism, and with Monte Carlo simulations reproducing potential applications. Simulations were developed using both a hardware-level language as testbenches for validation, and a software framework capable of providing higher statistics. Preliminary calculations on the power consumption and on the timing performances of the architecture are mentioned. Tentative silicon runs are planned in the near future.

The immediate scope of this work is to contribute to the effort to validate the ARCADIA device, currently under development. However the larger scope is an attempt to lay the foundations of new devices capable of improving the state-of-the-art performances in tracking; in this respect, future developments and further analysis will often be pointed to.

#### Abstract

Determinare le traiettorie delle particelle è un'operazione che viene effettuata all'interno di vari contesti. Si fa, per esempio, nelle sale sperimentali del CERN dove si studia la fisica delle alte energie, negli ospedali dove si ricostruiscono le immagini del corpo del paziente prima di una terapia, nelle industrie dove si rivelano eventuali difetti di produzione e nei telescopi per studiare i segreti dell'universo. Tra i dispositivi capaci di traccaire particelle, dominano i sensori in silicio, che negli ultimi decenni hanno migliorato le proprie performances sotto ogni aspetto: hanno buone risoluzioni spaziali e temporali, basso consumo, cambiano poco la traiettoria delle particelle passanti, sono relativamente facili ed economici da produrre e sono facilmente adattabili alle diverse applicazioni. In particolare, i recenti dispositivi a pixel monolitici (MAPS), che implementano nello stesso chip sia il sensore che la logica necessaria per l'amplificazione, il trasporto, e l'interpretazione del segnale, si stanno diffondendo, promettendo notevoli miglioramenti.

In questo momento, sia nella comunità scientifica che in quella industriale, ci sono molte realtà che stanno sviluppando dei MAPS. La collaborazione ARCADIA, dell'Istituto Nazionale di Fisica Nucleare (INFN), sta cercando di sviluppare un sensore monolitico che sia orientato ad applicazioni che richiedono grande area e basso consumo. ARCADIA si ispira ad ALPIDE (sviluppato dall'esperimento AL-ICE del CERN) considerato, ad oggi, un punto di riferimento nel mondo dei MAPS.

Questa tesi introduce inizialmente il processo che ha portato alla creazione del primo sensore di ARCADIA, per poi discutere più in dettaglio l'implementazione del protocollo di lettura, dettato dalle esigenze sperimentali. Inoltre, nell'ottica della validazione del sensore, si presentano i risultati preliminari di una campagna di studio volta all'indagine degli effetti dovuti al danneggiamento del reticolo causato da radiazione non-ionizzante.

La parte centrale di questo lavoro è la discussione di una innovativa architettura di lettura da utilizzare in un MAPS, pensata per applicazioni a potenze estremamente basse (come per esempio le applicazioni spaziali), che permette di ridurre la dimensione dei pixel. L'idea è quella di ricostruire la posizione in cui è passata la particella usando delle funzioni che la proiettino su diversi assi. Questo approccio sfrutta la sparsificazione dei dati prevista dalle applicazioni del sensore. Questa architettura è stata sviluppata dal punto di vista dell'elettronica digitale e le sue performances sono state studiate sia con un approccio matematico (usando un formalismo appositamente creato), sia con un approccio simulativo che riproducesse le condizioni sperimentali. Le simulazioni sono state scritte sia in un linguaggio di descrizione hardware (per la validazione), che all'interno di una struttura puramente software che permettesse uno studio a più alta statistica. Si discutono brevemente anche dei calcoli preliminari sulle performances di questa architettura in termini di potenza. Nel prossimo futuro, si programmano delle prove su silicio.

Questo lavoro è parte di un progetto atto alla validazione del sensore ARCADIA e, inserito in un contesto più ampio, è una prova dedita al miglioramento delle operazioni di tracciamento in silicio.

# Contents

| 1        | Exe              | Executive summary                                                                                                   |                                  |                                                                      |  |  |  |  |  |  |  |

|----------|------------------|---------------------------------------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------|--|--|--|--|--|--|--|

|          | 1.1              | Overvi                                                                                                              | ew                               | 1                                                                    |  |  |  |  |  |  |  |

|          | 1.2              | Target                                                                                                              | application and state-of-the-art | 2                                                                    |  |  |  |  |  |  |  |

|          | 1.3              | Metho                                                                                                               | dology                           | 5                                                                    |  |  |  |  |  |  |  |

|          | 1.4              | Results                                                                                                             | S                                | 5                                                                    |  |  |  |  |  |  |  |

|          | 1.5              | Outloc                                                                                                              | bk                               | 6                                                                    |  |  |  |  |  |  |  |

| <b>2</b> | Cha              | Charged particle tracking 9                                                                                         |                                  |                                                                      |  |  |  |  |  |  |  |

|          | 2.1              | Tracki                                                                                                              | ng principles and history        | 9                                                                    |  |  |  |  |  |  |  |

|          | 2.2              |                                                                                                                     | sensors types                    | 16                                                                   |  |  |  |  |  |  |  |

|          | 2.3              |                                                                                                                     | pixels development               | 20                                                                   |  |  |  |  |  |  |  |

|          |                  | 2.3.1                                                                                                               | Techonological node              | 24                                                                   |  |  |  |  |  |  |  |

|          | 2.4              | Tracki                                                                                                              | ng applications                  | 26                                                                   |  |  |  |  |  |  |  |

|          |                  | 2.4.1                                                                                                               | ALICE and ALPIDE                 | 26                                                                   |  |  |  |  |  |  |  |

|          |                  | 2.4.2                                                                                                               | AMS-02                           | 28                                                                   |  |  |  |  |  |  |  |

|          |                  | 2.4.3                                                                                                               | PRAvDA                           | 29                                                                   |  |  |  |  |  |  |  |

|          |                  | 2.4.4                                                                                                               | iMPACT and ALPIDE                | 30                                                                   |  |  |  |  |  |  |  |

| 3        |                  | ARCADIA 37                                                                                                          |                                  |                                                                      |  |  |  |  |  |  |  |

| 3        | AR               | CADIA                                                                                                               | Α                                | 37                                                                   |  |  |  |  |  |  |  |

| 3        | <b>AR</b><br>3.1 |                                                                                                                     | <b>A</b><br>t Overview           | <b>37</b><br>37                                                      |  |  |  |  |  |  |  |

| 3        |                  |                                                                                                                     | t Overview                       |                                                                      |  |  |  |  |  |  |  |

| 3        |                  | Projec                                                                                                              | t Overview                       | 37                                                                   |  |  |  |  |  |  |  |

| 3        |                  | Projec<br>3.1.1                                                                                                     | t Overview                       | $\frac{37}{38}$                                                      |  |  |  |  |  |  |  |

| 3        |                  | Projec<br>3.1.1<br>3.1.2                                                                                            | t Overview                       | 37<br>38<br>39                                                       |  |  |  |  |  |  |  |

| 3        |                  | Project<br>3.1.1<br>3.1.2<br>3.1.3                                                                                  | t Overview                       | 37<br>38<br>39<br>41                                                 |  |  |  |  |  |  |  |

| 3        |                  | Projec<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5                                                                 | t Overview                       | 37<br>38<br>39<br>41<br>42                                           |  |  |  |  |  |  |  |

| 3        | 3.1              | Projec<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5                                                                 | t Overview                       | 37<br>38<br>39<br>41<br>42<br>44                                     |  |  |  |  |  |  |  |

| 3        | 3.1              | Project<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>ARCA                                                        | t Overview                       | 37<br>38<br>39<br>41<br>42<br>44<br>46                               |  |  |  |  |  |  |  |

| 3        | 3.1              | Projec<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>ARCA<br>3.2.1                                                | t Overview                       | 37<br>38<br>39<br>41<br>42<br>44<br>46<br>46                         |  |  |  |  |  |  |  |

| 3        | 3.1              | Project<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>ARCA<br>3.2.1<br>3.2.2                                      | t Overview                       | 37<br>38<br>39<br>41<br>42<br>44<br>46<br>46<br>47                   |  |  |  |  |  |  |  |

| 3        | 3.1              | Project<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>ARCA<br>3.2.1<br>3.2.2<br>3.2.3                             | t Overview                       | 37<br>38<br>39<br>41<br>42<br>44<br>46<br>46<br>47<br>49             |  |  |  |  |  |  |  |

| 3        | 3.1              | Project<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>ARCA<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5           | t Overview                       | 37<br>38<br>39<br>41<br>42<br>44<br>46<br>46<br>47<br>49<br>53       |  |  |  |  |  |  |  |

| 3        | 3.1<br>3.2       | Project<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>ARCA<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5           | t Overview                       | 37<br>38<br>39<br>41<br>42<br>44<br>46<br>46<br>47<br>49<br>53<br>58 |  |  |  |  |  |  |  |

| 3        | 3.1<br>3.2       | Project<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>ARCA<br>3.2.1<br>3.2.2<br>3.2.3<br>3.2.4<br>3.2.5<br>Bulk d | t Overview                       | 37<br>38<br>39<br>41<br>42<br>44<br>46<br>47<br>49<br>53<br>58<br>63 |  |  |  |  |  |  |  |

| <b>4</b>     | Has                  | h readout architecture 75                                                                                                                                        |  |  |  |  |  |  |  |  |  |

|--------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

|              | 4.1                  | CMOS circuits and pixel readout                                                                                                                                  |  |  |  |  |  |  |  |  |  |

|              |                      | 4.1.1 CMOS circuits                                                                                                                                              |  |  |  |  |  |  |  |  |  |

|              |                      | 4.1.2 A readout circuit $\ldots \ldots \ldots$   |  |  |  |  |  |  |  |  |  |

|              | 4.2                  | Three readout architectures                                                                                                                                      |  |  |  |  |  |  |  |  |  |

|              |                      | 4.2.1 A clockless column readout                                                                                                                                 |  |  |  |  |  |  |  |  |  |

|              |                      | 4.2.2 ALPIDE digital architecture                                                                                                                                |  |  |  |  |  |  |  |  |  |

|              |                      | 4.2.3 Hash architecture                                                                                                                                          |  |  |  |  |  |  |  |  |  |

|              | 4.3                  | Hash projections - a mathematical approach                                                                                                                       |  |  |  |  |  |  |  |  |  |

|              |                      | 4.3.1 Formal framework                                                                                                                                           |  |  |  |  |  |  |  |  |  |

|              |                      | 4.3.2 Projections scoring $\ldots \ldots \ldots$ |  |  |  |  |  |  |  |  |  |

|              |                      | 4.3.3 Number of perfectly reconstructable addresses                                                                                                              |  |  |  |  |  |  |  |  |  |

|              |                      | 4.3.4 Examples of optimal projections sets                                                                                                                       |  |  |  |  |  |  |  |  |  |

| <b>5</b>     | Uoo                  | h architecture implementation and performance 111                                                                                                                |  |  |  |  |  |  |  |  |  |

| J            | 5.1                  | Physical implementation                                                                                                                                          |  |  |  |  |  |  |  |  |  |

|              | 0.1                  | 5.1.1       Pixel region       111                                                                                                                               |  |  |  |  |  |  |  |  |  |

|              |                      | 5.1.1         I Ref Tegion         113           5.1.2         Column State Machine (CLSM)         118                                                           |  |  |  |  |  |  |  |  |  |

|              |                      | 5.1.3 Column                                                                                                                                                     |  |  |  |  |  |  |  |  |  |

|              |                      | 5.1.4 HASH code propagation                                                                                                                                      |  |  |  |  |  |  |  |  |  |

|              |                      | 5.1.4       IIASH code propagation       121         5.1.5       Hash decoder (HDCD)       134                                                                   |  |  |  |  |  |  |  |  |  |

|              |                      | 5.1.6 Configuration Manager (CFGSM)                                                                                                                              |  |  |  |  |  |  |  |  |  |

|              |                      | 5.1.7 DataGatherer $\dots \dots \dots$                           |  |  |  |  |  |  |  |  |  |

|              | 5.2                  | Timing and power Performances                                                                                                                                    |  |  |  |  |  |  |  |  |  |

|              | 0.2                  | 5.2.1 Timing performances                                                                                                                                        |  |  |  |  |  |  |  |  |  |

|              |                      | 5.2.2 Power performances                                                                                                                                         |  |  |  |  |  |  |  |  |  |

|              | 5.3                  | Monte Carlo simulations                                                                                                                                          |  |  |  |  |  |  |  |  |  |

|              | J.J                  | 5.3.1 Mathematical properties                                                                                                                                    |  |  |  |  |  |  |  |  |  |

|              |                      | 5.3.2 Efficiency simulations varying the particle rate                                                                                                           |  |  |  |  |  |  |  |  |  |

|              |                      | 5.3.3 RTL simulation and Timing Validation                                                                                                                       |  |  |  |  |  |  |  |  |  |

|              | 5.4                  | 5.5.5       If I Simulation and Thing Valuation       105         Further improvements       165                                                                 |  |  |  |  |  |  |  |  |  |

|              | 0.4                  | $5.4.1  A \text{ faster decoder} \qquad \dots \qquad $   |  |  |  |  |  |  |  |  |  |

|              |                      | 5.4.2 Approach alternative: the derivative approach                                                                                                              |  |  |  |  |  |  |  |  |  |

|              |                      | 5.4.3 Reset-without-readout                                                                                                                                      |  |  |  |  |  |  |  |  |  |

|              |                      | 5.4.5 Reset-without-readout                                                                                                                                      |  |  |  |  |  |  |  |  |  |

| 6            | Con                  | iclusions 169                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

| $\mathbf{A}$ | Radiation Damage 173 |                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |

|              | A.1                  |                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |

|              |                      | A.1.1 Soft Errors                                                                                                                                                |  |  |  |  |  |  |  |  |  |

|              |                      | A.1.2 Hard errors                                                                                                                                                |  |  |  |  |  |  |  |  |  |

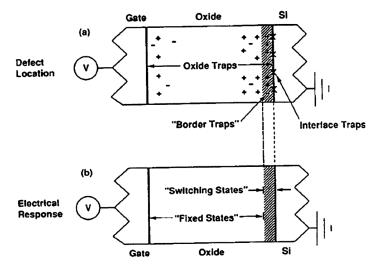

|              | A.2                  |                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |

|              |                      | A.2.1 Oxides in a CMOS detector                                                                                                                                  |  |  |  |  |  |  |  |  |  |

|              |                      | A.2.2 Defects creation in the oxide                                                                                                                              |  |  |  |  |  |  |  |  |  |

|              |                      | A.2.3 Defects in gate oxide                                                                                                                                      |  |  |  |  |  |  |  |  |  |

|              |                      |                                                                                                                                                                  |  |  |  |  |  |  |  |  |  |

|                                   |                                        | A.2.4 | Defects in STI     | 180 |  |  |  |  |

|-----------------------------------|----------------------------------------|-------|--------------------|-----|--|--|--|--|

|                                   | cement/Bulk Damage Effects             | 180   |                    |     |  |  |  |  |

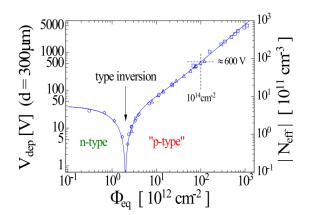

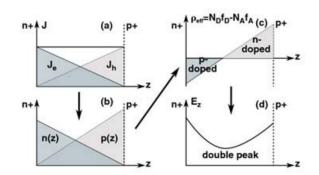

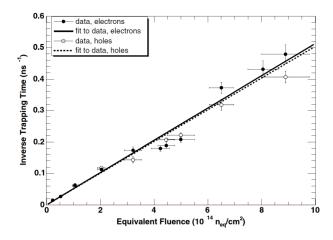

|                                   |                                        | A.3.1 | Modelling          | 181 |  |  |  |  |

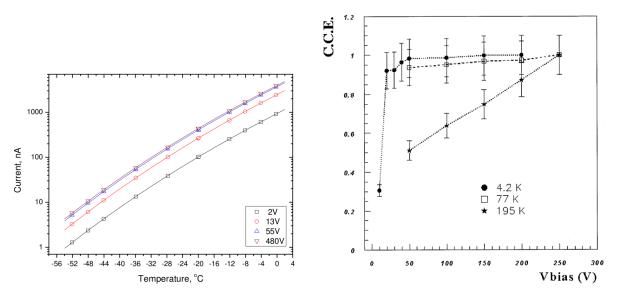

|                                   |                                        | A.3.2 | Effects on silicon | 184 |  |  |  |  |

|                                   |                                        | A.3.3 | Dependencies       | 187 |  |  |  |  |

| B ARCADIA-MD1 coincidences seeker |                                        |       |                    |     |  |  |  |  |

| С                                 | C A single hit through the Monte Carlo |       |                    |     |  |  |  |  |

| Bi                                | Bibliography                           |       |                    |     |  |  |  |  |

## Chapter 1

## Executive summary

### 1.1 Overview

In the field of particle tracking, the scientific community routinely uses solid-state pixel sensors to detect and track ionising particles with micrometric spatial resolutions, from elementary particles produced at the CERN Large Hadron Collider (LHC) [1]–[4], to cosmic rays arriving from distant galaxies detected by space-born telescopes [5]. The very same sensors have also found successful applications in many fields where particle tracking may provide critical information, such as medical imaging [6] or hazardous material security [7].

This thesis focuses on a specific category of pixel sensors, the so-called Monolithic Active Pixel Sensors (MAPS), which to a first approximation share both their working principle and most of their structure with the pixel sensors commonly found in standard consumer electronics, such as smartphones and cameras, and indeed they are manufactured with the very same microelectronic CMOS imaging processes [8]. The *monolithic* term in the acronym highlights the difference with respect to the *hybrid* pixel sensors, where a pixellated sensor layer, typically made of semiconductor material such as silicon or germanium, is bonded to a matching readout layer, realised with the very same CMOS technology used for MAPS. Hybrid sensors are the mainstay in particle tracking applications, as well as in photon science, where the possibility to fine-tune the sensor layer both in terms of material thickness and material type allows the detection of a wide range of particles, at different energies, and also offers higher radiation resistance with respect to MAPS. However, in recent years, MAPS have reached sufficient maturity to be successfully employed in several scientific experiments, where they offer some key advantages over hybrid solutions, as discussed in this work in detail.

Where scientific MAPS (and hybrid sensors as well) certainly differ from their commercial siblings is in one key design element: they are optimised to read only a very small portion of pixels (less than 1 per mille on average) instead of the entire, full-frame image. Such a procedure, commonly referred as **sparsification** or **zero suppression**, allows to achieve readout speeds otherwise impossible to obtain with traditional full-frame sensors. Sensors

aimed at particle tracking also have, depending on their target application, much more stringent requirements in terms of radiation hardness; i.e., the device capability to survive and operate in hostile radiation environments, such as those found, for example, at particle accelerators, medical beams, or in outer space [9].

The focus of this thesis work is the study and development of an innovative readout architecture for MAPS aimed at particle tracking, and the characterisation of a sensor prototype device incorporating an innovative, fully-depleted substrate. This work attempts to improve the current state-of-the-art in MAPS in the key areas of power consumption, readout speed, pixel pitch, and verified radiation hardness.

## 1.2 Target application and state-of-the-art

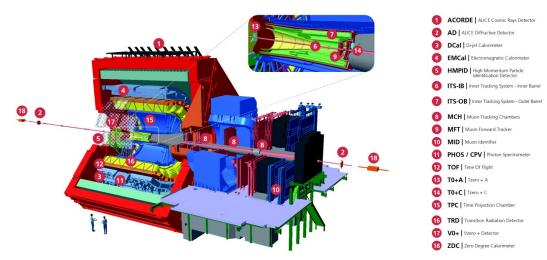

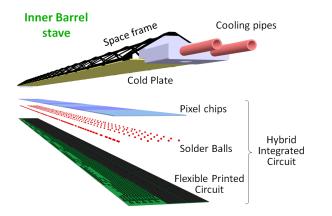

In the scientific world, MAPS find prominent applications in the tracker detectors developed for particle physics experiments, and every big experiment at the CERN LHC already uses MAPS [10], or plans to use them in the near future [11]–[13]. These devices are also being used in space-born trackers onboard satellite missions [14]. Tracker detectors usually consist of several stacked layers, arranged in planar or cylindrical symmetry, where each plane registers a passing particle position in space and time; by combining the positions recorded by each layer, it is possible to reconstruct the particle trajectory in 3D space, the so-called **track**. Unlike commercial applications, the reduction of the material budget is of paramount importance to minimise the interference of the sensor with the particle path, as the tracking operation often is only a component of the overall experiment. This, in turn, pushes for the minimisation of the power consumption in order to reduce the thickness of the cooling system [15].

The specifications for tracking MAPS change widely, depending on the application, and there is no way to meet all of them with a single design. Therefore, this work narrows its target to the optimisation of MAPS used in tracking applications that require the lowest possible material budget and, consequently, the lowest achievable power consumption (below  $35 \text{ mW cm}^{-2}$ ), together with a small pixel pitch (10 to 20 µm), and moderate radiation resistance (5 kGy,  $2 \times 10^{12} \text{ 1 MeV } n_{eq}/\text{cm}^2$ ). This is a reference case for space experiments and some High Energy Physics (HEP) ones too.

To better frame the *small pixel pitch* figure, it is worth recalling that the current generation pixel sensors installed at the LHC experiments have a pixel pitch ranging from 150 µm [16], [17] down to 28 µm [10], while pixels found in commercial imaging devices usually are in the 1 µm to 10 µm range. The above "small" pitch attribute therefore refers to the pixels sensors typically employed in high energy physics tracking applications, where pixel dimensions below 20 µm are considered small. The case for a finer pitch is prompted by the need of improving the spatial resolution of the particle origin position to the 1 µm level, which implies a pixel pitch on the order of 10 µm size, when utilising at least 3 measurement points in space, each characterised by a  $\frac{10}{\sqrt{12}}$  µm uncertainty (Particle track reconstruction resolution approximately goes as  $\frac{\sigma}{\sqrt{N+1}}$  for an ideal detector, where  $\sigma$  is the single layer spatial resolution and N is the number of tracking layers, as a consequence of a simple linear interpolation).

From the point of view of radiation damage, MAPS are considered moderately radiation resistant when compared to tracking detectors at accelerator facilities: the benchmark for high radiation levels is established by high repetition rate (40 MHz) proton-proton collision, where over the lifetime of an experiment (typically 5-10 years) the integrated radiation levels may reach 10 Mrad and  $2 \times 10^{16}$  1 MeV n<sub>eq</sub>/cm<sup>2</sup> respectively. Conversely, experiments where the interaction rate is lower [10] and/or the colliding particles are leptons instead of hadrons [18], typical integrated radiation levels over the experiment lifetime are on the order of 500 krad and  $2 \times 10^{12}$  1 MeV n<sub>eq</sub>/cm<sup>2</sup>.

For what concerns the power consumption, the current benchmark for scientific MAPS is the ALPIDE sensor developed by the ALICE collaboration [10], which has a reference power consumption of  $35 \text{ mW cm}^{-2}$  (depending on various operational modalities, this value may change up to a factor 2 in both directions). The hybrid pixel sensors planned for installation in the near future at the ATLAS and CMS experiments [19] [20], has much larger consumption, in the order of 1000 mW cm<sup>-2</sup>. Such larger power dissipation is due in part to the different technology (hybrid versus monolithic) and in part to the different specifications, the maximum hit rate in particular, which greatly exceed that of the ALPIDE sensor. These considerations about the power dissipation highlight how, aiming for minimum consumption and a small pixel pitch, will require a trade-off in terms of maximum particle rate. For reference, the aforementioned ATLAS and CMS sensors have been designed to handle a maximum rate of 3000 MHz cm<sup>-2</sup>, while the ALPIDE can withstand up to 10 MHz cm<sup>-2</sup>, more than a two orders of magnitude difference.

This work aims at improving the experiments in which ALPIDE is currently used; hence, the reference specifications given above are an improvement over the current gold standard in the field. Such a device would meet the requirements of a few different applications, for example:

- precision experiments at next generation lepton colliders: The interaction between leptons, such as electrons or muons, is much cleaner and lepton colliders produce a less dense particle field with respect to hadron machines (like the LHC). To best record these fine details requires sensors with the lowest possible material budget, and hence power dissipation. The power level goal is the one which would allow air cooling; i.e., below 20 mW cm<sup>-2</sup> [21] (or even in-vacuum radiation only cooling see space applications). The sparser particle field allows relaxing the radiation resistance of the exposed device with respect to the present detectors installed at the LHC [22] by 2 orders of magnitude, rendering MAPS a viable choice;

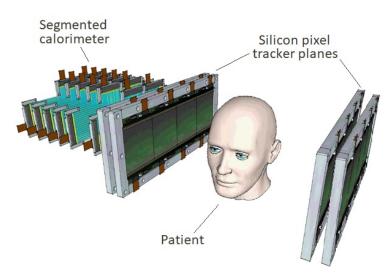

- medical tracking: The usage of light ions (protons, He, Ca) medical pencil-beam is the most advanced and effective radiotherapy available for cancer treatment. Protons of the order of 250 MeV will be used as well to render 3D images of the body, like in a CT scan, with the added benefit of a much lower dose to the patient, and a better tissue density resolution [23] (see Section 2.4.4). Such 3D imaging requires precise proton tracking, just like in a HEP tracking particle experiment, with the caveat that

in order to avoid excessive multiple scattering of the protons requires that the sensors be as thin as possible;

- space applications: Space telescopes tracking cosmic radiation embed at their heart a particle tracker, conceptually identical to those found in ground-based particle physics experiments. Like any space application, energy consumption is paramount, due to the limited space vessel power sources as well as problematic dissipation issues. For this reason, all major space telescopes still use micro-strips because of power budget constrains [24], the current limit being about 5 mW cm<sup>-2</sup>, far below the current state-of-the-art ALPIDE power budget;

- industrial applications: Industry is interested in imaging, metrology, tomographic reconstruction, and range-finding applications. For this purposes almost exclusively visible, infra-red, and x-ray photons are used because of the complexity, cost, and restrictions for using other radiation sources that are employed in scientific, medical, and military facilities. Whereas silicon has efficient photon detection in the visible and near-IR band, it is almost transparent to higher energy photons: in scientific applications the sensors of choice for x-ray imaging are the hybrid pixel sensors, with Germanium or other high-density semiconductor materials used for the sensor layer. However, the intrinsic high costs of hybrid pixel productions renders this solution unpractical for industrial applications, where instead x-ray panels (based on TFT monitor technology) are the most widespread sensor, with the trade-off of low resolution (1 mm) and speed (10 Hz). MAPS, although in principle not optimal for x-ray detection, may be adapted to improve x-ray detection efficiency (for example, by reaching full depletion [25]); in addition their low production cost (compared with other technologies) boosts their convenience when there is the necessity to instrument large detection area, as in industrial Computed Tomography systems.

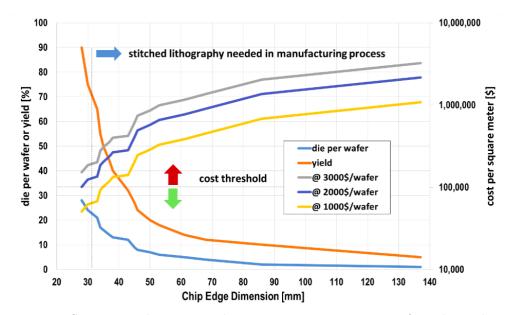

The challenge in meeting these specifications scales with the device area: whereas a very small sensor of few square millimetres may be (almost) promptly designed, realising a single-piece detector of several square centimetres with the target performance level requires pushing the state-of-the-art. It is worth stressing here again that, in many applications like those just presented, tiling several small sensors is not an option, usually due to extremely tight material budget constraints and, therefore, the goal is indeed maximising the area covered by a single sensor. Likewise, the maximum sustainable rate affects also the design complexity: at extremely low rates, large area sensors with extremely low power dissipation are indeed possible, as exemplified by astronomical CCDs [26].

Looking at the present state-of-the-art, and reviewing the requirement for some planned experiments in the field of high energy physics [27] [28], it is apparent how a single sensor having an active area equal or bigger than  $10 \text{ cm}^2$ , and capable to withstand a maximum rate of 20 MHz cm<sup>-2</sup> or more, would be able to meet the requirements for such future scientific applications when coupled with small pixel pitch and low power consumption.

Summarising, the target specifications for the device envisioned by thesis are the following:

• pixel pitch:  $O(10 \,\mu\text{m})$

- power consumption:  $\leq 35 \,\mathrm{mW \, cm^{-2}}$

- radiation tolerance:  $\geq 500 \,\mathrm{krad}$  and  $2 \times 10^{12} \,\mathrm{1 \, MeV} \,\mathrm{n_{eq}/cm^2}$

- active area:  $\geq 10 \,\mathrm{cm}^2$

- maximum rate:  $\geq 20 \,\mathrm{MHz} \,\mathrm{cm}^{-2}$

## 1.3 Methodology

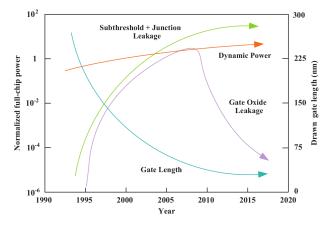

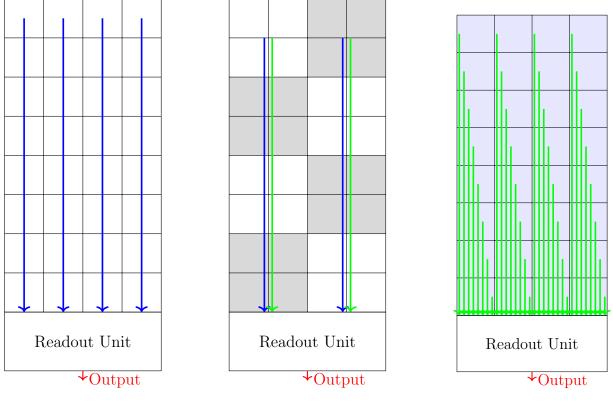

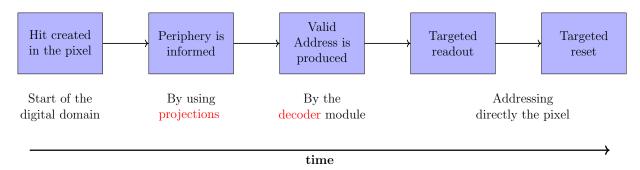

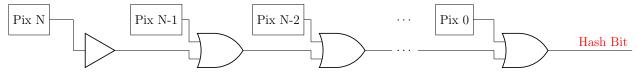

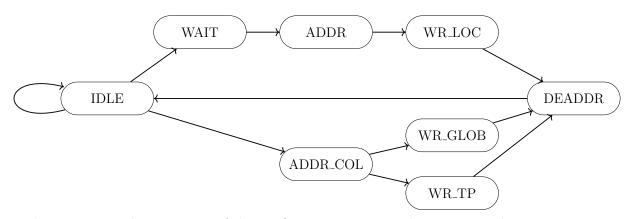

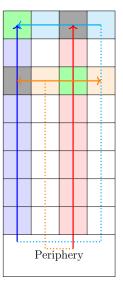

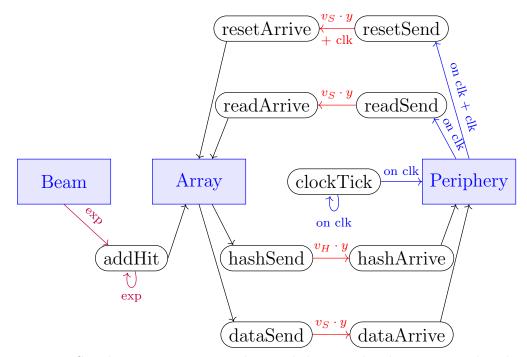

The idea pursued in this work in order to meet these goals heavily relies on performing sparsification at the architectural level: in the proposed architecture, called **hash**, a hit pixel asynchronously triggers multiple signals through a net of multiple metal wires, where each line is shared among different subsets of the pixel array. These wires take the signals to the periphery, where they produce a so-called **hash code**, which is used to reconstruct the hit pixel address. This approach reduces the number of in-pixel transistors necessary to communicate the hit position to the periphery, when compared to the current state-of-the-art architectures, leading to the following improvements:

- fewer transistors occupy less space; hence, make the pitch shrinking feasible;

- fewer transistors reduce the power consumption, as there will be both less leakage and less transistions on average;

- fewer transistors free more layout area for routing, simplifying the realization of a scalable architecture for very large area sensors.

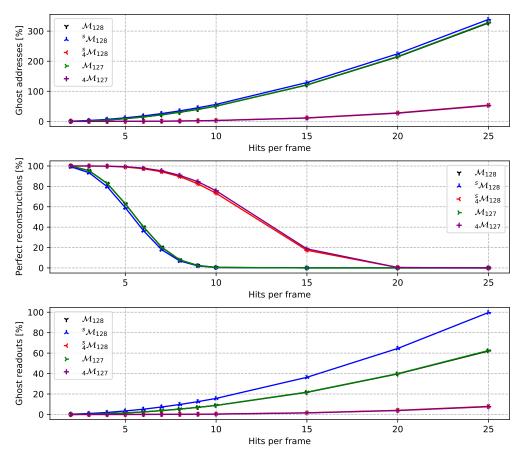

The trade-off of such solution is the maximum sustainable particle flux: according to the simulations discussed in this work, such limit is however higher than the current benchmark set by the ALPIDE sensor collaboration.

The proposed hash architecture is indeed an abstract concept, not necessarily limited to silicon pixel sensors, that might be successfully applied for the readout of any matrix of binary values where sparsification conditions are met. In this work it is applied to MAPS, and several implementations flavours are discussed.

### 1.4 Results

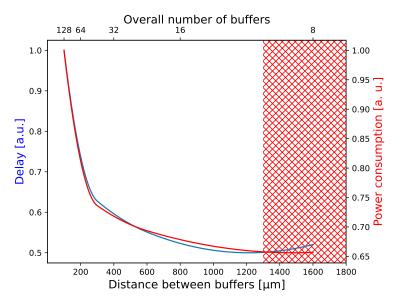

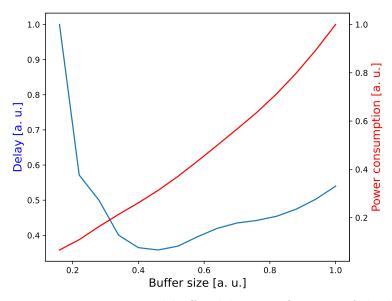

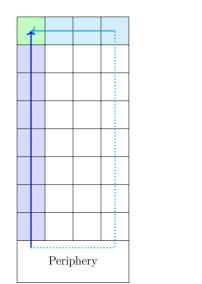

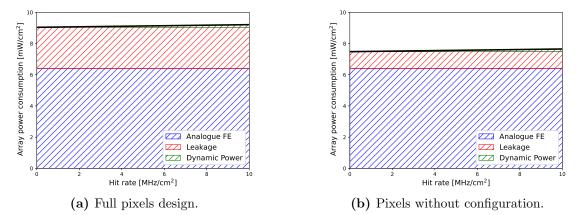

The hash readout architecture has been completely developed at the Register Transfer Level (RTL). The design has been validated through both mathematical analysis and intensive Monte Carlo simulations, and shows no major concerns; the pixel area was estimated post-synthesis (LFoundry 110 nm technological node); the power consumption has been evaluated through analytical calculations performed manually (communication power) or using proper circuit synthesis and simulation tools (switching and leakage power) for the pixels. The maximum sustainable flux was estimated through a software fully replicating the architecture in a computationally-faster environment.

The results obtained clearly depend on the implementation chosen (flavour), as several

have been outlined to try and assess the potentialities and the limits of this innovative approach. For the most conservative case that was studied in detail, the results are:

- a full sensor sector sized  $0.8 \times 12.8$ mm<sup>2</sup> tilable on the long side. Currently, ALPIDE sensor has a size of  $15 \times 30$ mm<sup>2</sup>; hence, a first MAPS implementing of the hash readout could have a similar size by tiling 32 such sectors (or a square one by tiling 16 sectors). The design is scalable and can be adapted to bigger devices;

- a complete pixel digital part sized  $\approx 125 \,\mu\text{m}^2$  per pixel, compared with the  $\approx 250 \,\mu\text{m}^2$  of the ALPIDE sensor pixel digital part;

- an estimated power consumption for the sensor pixels bulk  $\leq 10 \,\mathrm{mW \, cm^{-2}}$ , to be compared to  $35 \,\mathrm{mW \, cm^{-2}}$ , the total power consumption of ALPIDE;

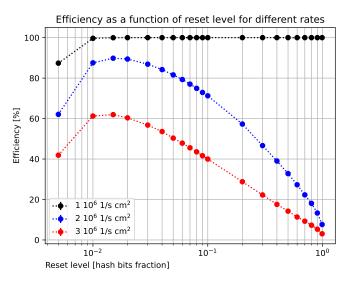

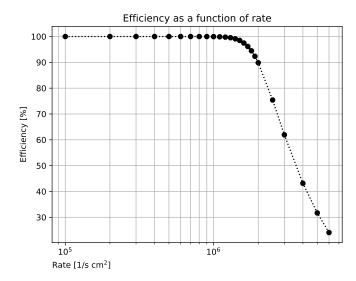

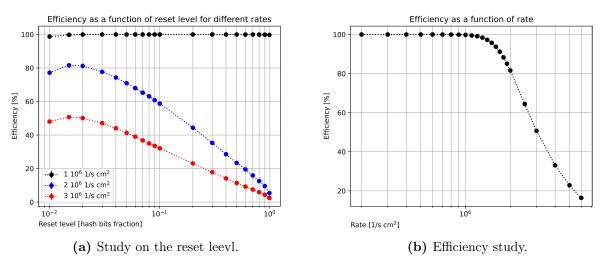

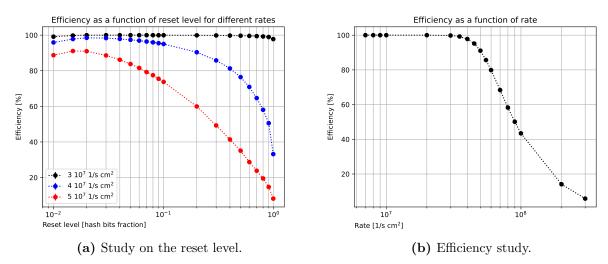

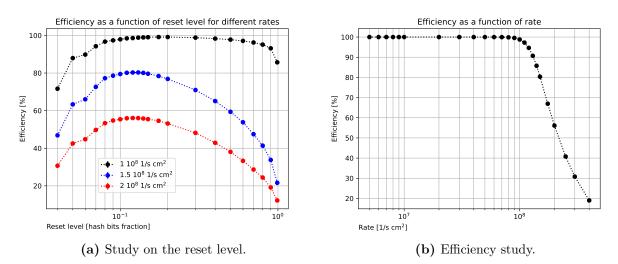

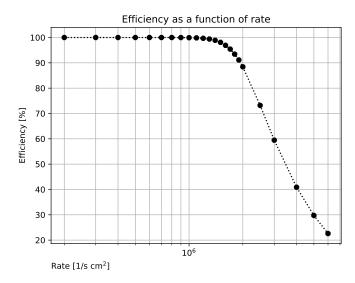

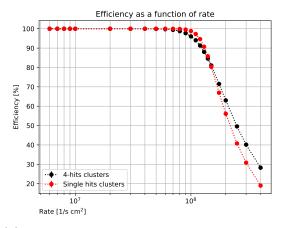

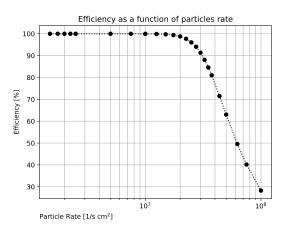

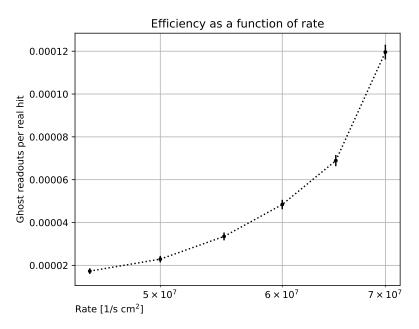

- an efficiency curve that starts dropping at about  $1 \times 10^8$  particles per square centimeter, assuming that a cluster is in one pixel region; a tracker in ALICE like the ALPIDE has an expected peak flux of  $2 \times 10^6$  particles per square centimeter [29] (even in a very pessimistic corner where the hit is 4-regions large, the efficiency remains high in ALPIDE working context).

These figures can be further improved by implementing some extra design optimizations, which are discussed at the end of this work, and which give confidence on how this architecture might effectively improve the current state-of-the-art. Such bolder solutions would make it feasible to:

- create bigger sensors trying more complex place-and-route;

- reduce the power consumption changing the readout-and-reset scheme taking further advantage of the hash approach;

- shrink the pixel further by optimising the place-and-route;

- push the rate limit further by optimising the periphery.

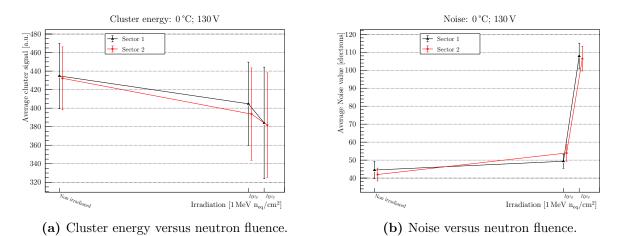

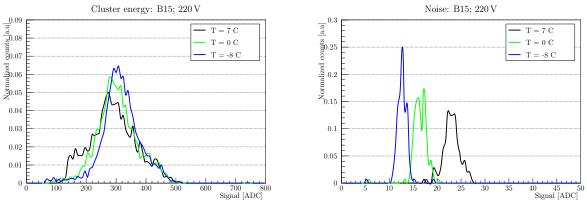

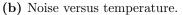

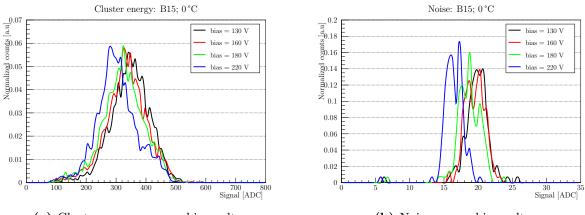

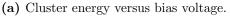

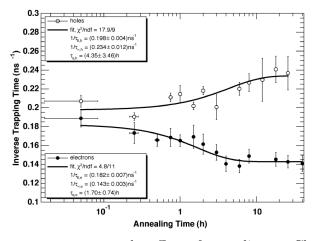

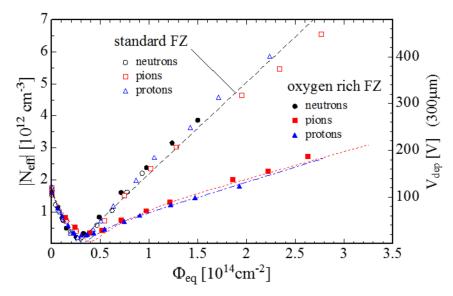

From the radiation-resistance point of view, the performances of the reference LFoundry 110 nm modified CIS technological node [30] has been measured by using a fully depleted MAPS (ARCADIA) that is developed in the very same technology planned for the hash readout architecture. Some tests discussed in this work showed how from the bulk damage point of view the sensor is still functional at around 15 °C for an irradiation level of  $1 \times 10^{13}$  1 MeV n<sub>eq</sub>/cm<sup>2</sup>. The damage due to ionising radiation has not been quantified in this thesis but an experimental campaign [31] measured a two-fold increase of the noise (still usable sensor) after a dose of 10 Mrad.

## 1.5 Outlook

Chapter 2 introduces the scientific interest for the issues that are addressed in this thesis. Section 2.1 presents the history of trackers as well as the driving principles that make charged particle tracking possible; Section 2.2 presents the three ways that are used to move the information around the array (CCDs, hybrid solutions, MAPS); Section 2.3 lists the three problems that need to be addressed in order to develop a working silicon tracker (sensor design, analogue design, digital design) together with few necessary thoughts on the choice of the technological node; Section 2.4 shows four experiments and points out why silicon tracking is important for them and how it is implemented.

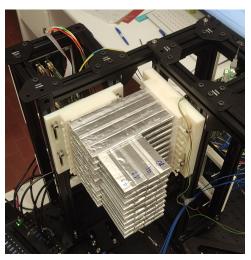

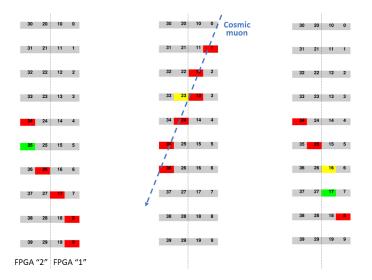

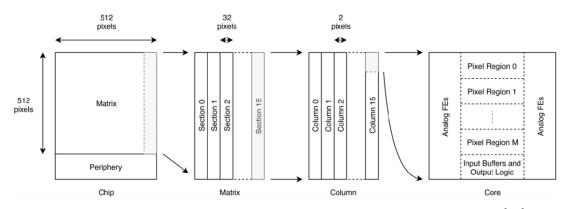

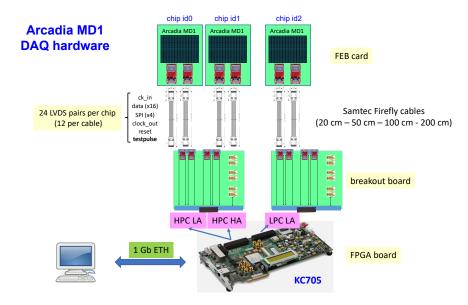

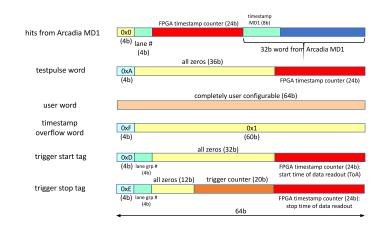

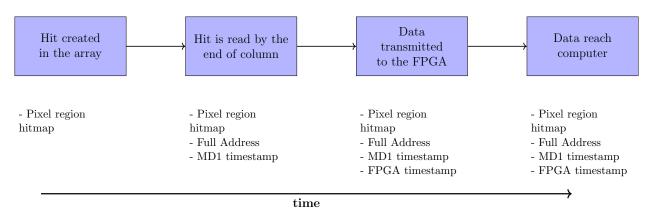

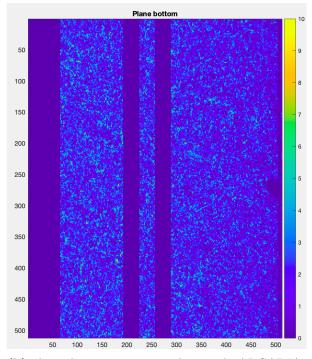

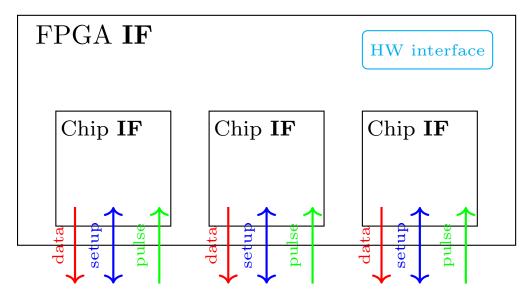

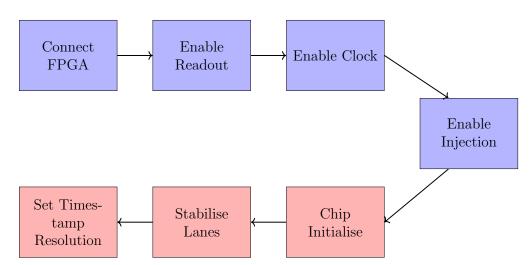

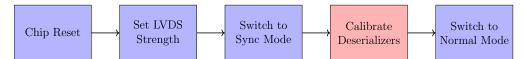

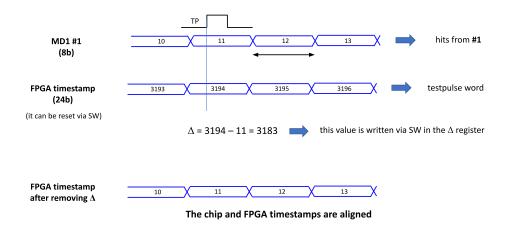

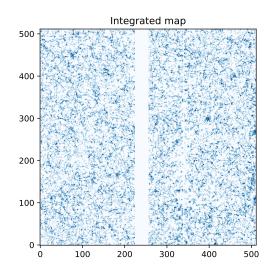

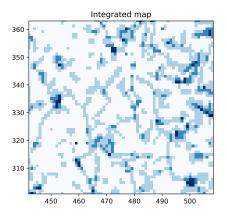

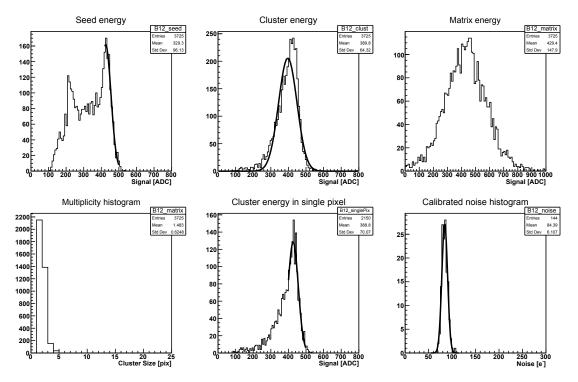

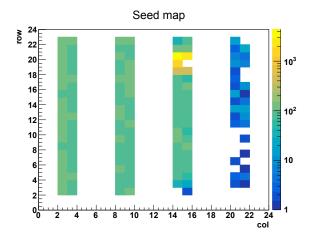

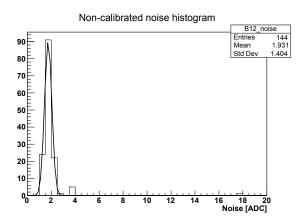

Chapter 3 presents the commissioning work of the ARCADIA sensor, a fully depleted MAPS, in particular in its first version ARCADIA-MD1. This work is a concrete example of the steps necessary to test such devices. Section 3.1 gives an overview of the ARCADIA project, showing why it is interesting for the tracking community and briefly presenting the work done to implement it; Section 3.2 presents the development of the data acquisition system of ARCADIA, together with some experimental plots; Section 3.3 presents the results of a neutron irradiation campaign to test the resistance to bulk damage of the 110 nm modified CIS [30] technology node.

Chapter 4 finally introduces the hash architecture, framing it among other digital readout architectures. Section 4.1.1 shows how to rate CMOS circuits in terms of power consumption and time delays, focusing in particular on the binary readout architectures that are the subject of this thesis; Section 4.2 presents three architectures: an abstract clockless column readout architecture, the ALPIDE readout architecture, and the hash architecture, rating them using simple algebraic parameters; Section 4.3 presents a mathematical framework created to rate the several connections (called projections) depending on how well they perform for hash purposes.

Chapter 5 discusses the implementation of the hash architecture and estimates its performance. Section 5.1 presents the physical implementation developed for this work; Section 5.2 shows the analytical calculations performed studying the technological libraries to estimate both the power and the timing performance of the device; Section 5.3 presents the set of Monte Carlo simulations performed to assess the correct functioning of the architecture and the maximum particle flux; Section 5.4 presents some alternative hash architectures that may further improve the performances.

Appendix A gives a theoretical presentation of the issue of radiation damaging for silicon sensors; Appendix B shows the smart coincidences seeker routine used to spot signals in more than one ARCADIA sensor; Apprendix C shows an example of a single hit propagating through the Monte Carlo software developed to evaluate the performance of the hash readout architecture.

# Chapter 2

## Charged particle tracking

Whenever a charged particle traverses matter, it deposits energy by interacting with it. Particle trackers are devices capable of intercepting these various energy depositions in order to reconstruct the particle trajectories. Generally, tracking refers to a non-invasive operation: the purpose is quite often to understand where the particle is going without disturbing the trajectory itself, as tracking is in many cases only a component of a more complex measurement. This is not completely achievable, as the particle must interact with matter in order to be spot, and such an interaction leads to changes in its kinematics, but this effect can be minimized. In the last century, the tracking of charged particles has been one of the most demanding challenges in the field of particle physics. In this introductory chapter, first an overview on the tracking mechanisms and a historical roundup is given in Section 2.1; next sections focus with more details on tracking by using silicon pixel sensors, the subject of this thesis. In Section 2.2 the common readout paradigms used for tracking is silicon pixels are listed, and the development approach generally followed is described in Section 2.3. Finally, Section 2.4 lists some experiments where silicon trackers are used and review what their characteristics are.

## 2.1 Tracking principles and history

#### The physics of charged particles tracking

The equation that describes the energy loss of a charged particle in matter is the Bethe-Bloch equation, known since the 1930s [32]. Bethe-Bloch is a formula describing what is referred to as **ionising energy loss**; i.e., the energy that is continuously lost by the charged particle as it progresses through the material due to its interactions with the electrons in the material. These electrons, which receive energy, are excited and easily detached from the atom with which they are bound. This leads to the production of a free electron and a quasi-particle called hole; i.e., a missing electron in matter. In most cases, a free electron jumps back into the hole right after its creation in a process called **recombination**, in which

case there is no evidence of the passage of the particle. But in some cases the effect of the particle is persistent, as some freed electrons do not immediately recombine; in this situation the electron-hole pairs may ultimately be detected and used for particle tracking. Ionising energy loss is not the only process that can lead to energy loss in matter for a charged particle; nevertheless, it is the most probable and easy to use.

Neutral particles like photons and neutrons can be detected as well, but this can happen only if these particles create a charged counterpart that interacts with matter. Photons interact via the photoelectric effect, Compton scattering, or pair production; in all these three processes, charge is generated inside the material (positrons and/or electrons); however, the original photon is destroyed. Neutrons interact via strong nuclear interactions and can create ionising nuclear recoils, fragments, and other neutrons. Here too, the original neutron is often destroyed, or its kinematics deeply modified. The focus of this thesis is the study of trackers for charged particles; nevertheless, they can be successfully employed to also detect these neutral particles.

#### The first particle trackers

The first devices that could track single particles were used to detect radiation in the natural environment, natural radioactivity, and especially cosmic rays. Trackers development started from nuclear emulsions first developed around 1910 [33], [34], and evolved to bubble chambers (1952 [35]), spark chambers (1954 [36]), multi-wire proportional chambers (1968 [37]), drift chambers (1971 [38]), and time projection chambers (1974 [39]).

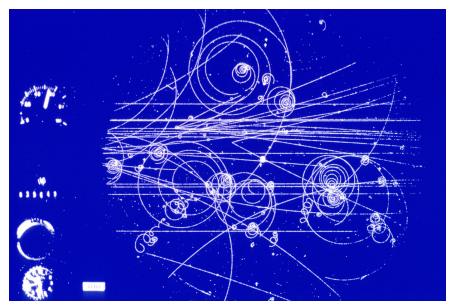

**Figure 2.1:** A 1960 image from the CERN liquid hydrogen bubble chamber of a lambda decay. Taken from [40].

As a reference, the working principle of bubble chambers is presented (see Figure 2.1): the tracker is a device containing an unstable liquid heated above its evaporation temperature.

If the liquid container is clean enough, there are no suitable places for the bubble enucleation needed for the liquid to begin the transition to the gas phase. However the energy deposition by ionising radiation leads to the generation of free electrons and holes that create regions where the liquid begins to locally boil; this gives rise to the formation of longer-lasting visible bubbles along the particle trajectory. By taking photos from different directions of the bubble chamber right after the passage of the ionising particle (few milliseconds later), it is possible to actually track the charged particle in three dimensions.

#### Tracking in silicon

A big boost to tracking techniques arrived thanks to the modern photolithography processes developed by the semiconductor industry, which led to the development of the first silicon trackers in the 1980s. These devices rapidly became the focus of the tracking communities in various fields, such as **H**igh Energy Physics (HEP), astro-particle physics, nuclear physics, and medical physics. Silicon is by far the most widely used semiconductor today because of many features: it is very abundant, relatively easy and inexpensive to manufacture, stable at room temperature, and its oxide is a really good insulating material. Historically [41], the very first silicon detectors were used in Berkeley [41], Dubna [42], and CERN [43], [44]. The complete treatment of the working principles of silicon as a charged particle detector can be found in several academic textbooks that thoroughly discuss this matter [45], [46]. Silicon is a semiconductor: i.e., it has a finite gap (about  $1.1 \,\mathrm{eV}$ ) between the valence band (a band full of electrons when the device is at absolute zero temperature) and the conduction band (where the electrons can move through the crystal). By adding some dopants, new possible states can be placed within the gap, and the silicon behaviour can be engineered. There are two different types of dopants used: a p-type silicon contains some atoms of an element of the third chemical group (such as boron or gallium), while a *n*-type silicon contains some atoms of an element of the fifth chemical group (such as arsenic or phosphorus).

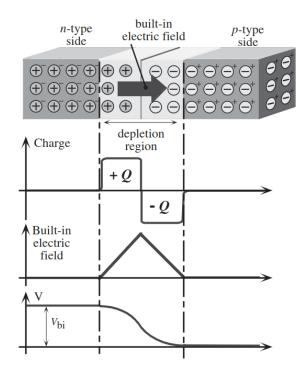

When a p-type silicon is joined to an n-type silicon, a so-called pn-junction is formed; there is a step in the electron density curve, hence charges (electrons and holes) start diffusing through the junction until there is dynamic equilibrium between the diffusion pressure and the electrical pressure due to the charge accumulation. Around the junction, a **depleted region** is created: a portion of silicon where all mobile charges have been removed; i.e. there are no free charges (see Figure 2.2) but only naked ionised dopants. The application of an external voltage called *reverse bias* can further extend this depleted region. When the ionising particles travel through such a depleted region, the generated charges do not recombine as both the electrons and the holes follow the local electric field and are promptly pushed away from each other. Thanks to this effect, a pn-junction (also known as a diode) can be successfully used as the basis for a tracker of charged particles.

The charges generated inside a depleted region are collected and integrated on a proper capacitance that can be read out; the particle passage is pinned down and can be measured. The equation defining the voltage produced by charges in a capacitor is the following:

$$V = \frac{Q}{C} \tag{2.1}$$

Figure 2.2: A scheme representing a pn-junction. Plots for charge, electric field and potential distributions are shown as well. Taken from [46].

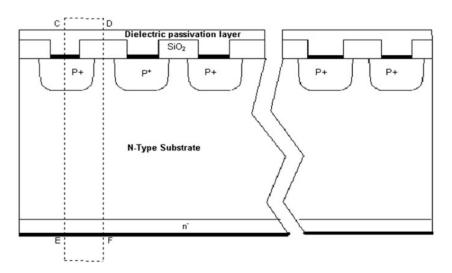

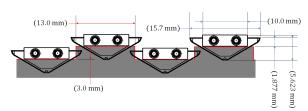

This equation shows how, for a fixed number of charges generated by the impinging particle, the smaller the capacitance, the higher the voltage to be read out; thus, the signal read will be higher and the device will be better-performing<sup>1</sup>. A smaller capacitance can be achieved by reducing the size of the electrode that collects the charges; exactly for this reason the first silicon detectors were **microstrips**: long diodes (strips) are created along a direction and then charges are read through a long electrode (see Figure 2.3). Because of this segmentation, the capacitance is lower compared to a single, large device, and the signals can be easily retrieved by accessing the electrodes at one of their ends. The first microstrip devices were not used as trackers according to modern interpretation, but were instead active targets: the impinging particle reacted with the silicon, and the signal was read out on the electrode that was closest to the interaction point. The first use of silicon for tracking dates to 1981, with the experiments NA11/NA32 [47], where six planes of silicon microstrip devices were mounted to measure the vertex position.

The use of a tracker that generates an electric signal requires a **readout** system, an aspect that is discussed throughout the main chapters of this thesis (Chapter 4 and Chapter 5). To read out a microstrip sensor, it is necessary to access the charges stored on the long capacitors. It is possible to connect individually to each one of them via a wire bonding and use a separate device to perform the necessary operations to make this voltage signal readable; i.e., the amplification, shaping, and digitisation of the signal.

<sup>&</sup>lt;sup>1</sup>This is an over-simplification. A lower capacitance improves both the signal-to-noise ratio and the timing resolution, while a higher capacitance improves the charge collection efficiency and the spatial resolution.

Microstrips provide several advantages over the other tracking techniques listed before, in particular:

- fast response (of the order of the ns);

- high segmentation, hence good spatial resolution (of the order of tens of μm);

- good linearity and energy resolution (at room temperature of the order of the keV);

- simplicity in operation.

For these reasons, microstrips have been widely used since their invention and are still commonly found today.

Figure 2.3: The cross-section of a silicon microstrip detector. Single long diodes are created in silicon, each one with its own electrode. The strips, in this image, are oriented as perpendicular to the page. By reading the voltage on the electrode it is possible to measure the energy deposited in the sensor. Taken from [48].

#### Silicon pixel trackers

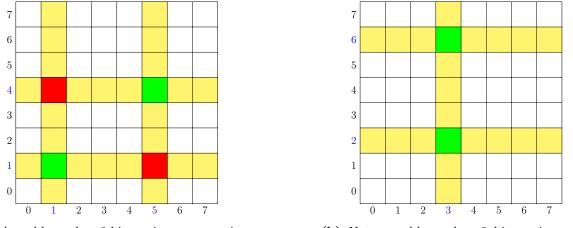

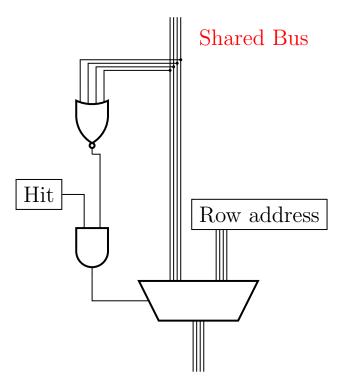

One of the main limitations of the microstrip approach lies in the fact that they can measure only one direction of the particle position; a second one can be inferred by the tracking plane position, considering that the sensor is usually very thin  $\mathcal{O}(10 - 100 \,\mu\text{m})$ ; the third coordinate cannot be accessed. For this reason, pairs of microstrip detectors are often used: one sensor is placed to have the strips aligned along the x-axis, and shortly after (often in the same silicon die), a second sensor has the strips aligned along the y-axis. By reading both sensors, it is possible to obtain the three-dimensional coordinates of the point where the ionising particle passed. This approach fails for cases with many particle tracks (high multiplicities), that are called in this thesis data collisions. If there are two charged particles crossing the detector almost at the same time, two data concerning the x position and two data concerning the y position would be obtained, and it would not be possible to pair these data obtaining the two 3D points: there will be both two correct reconstructions and two wrong ones (in most cases, see Figure 2.4). This issue can be tackled by changing the approach: instead of having long electrodes, it is possible to construct small square-like electrodes, and read both the x and the y at the same time. These devices are called **pixel sensors**. Formally, the definition of a silicon pixel sensor used in this work is: "a silicon tracking sensor using a pn-junction to detect ionising particles and divided into small rectangular or square regions, usually with a size of the order of tens of  $\mu$ m".

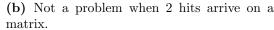

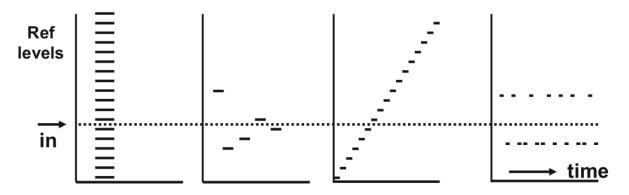

(a) A problem when 2 hits arrive on a matrix.

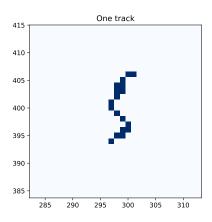

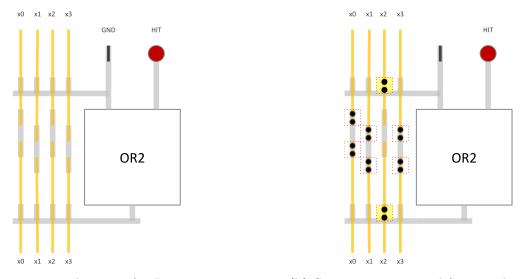

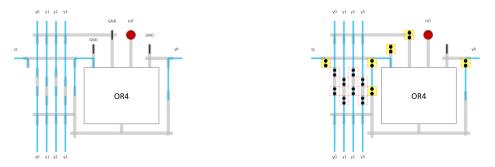

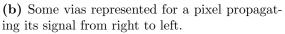

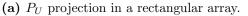

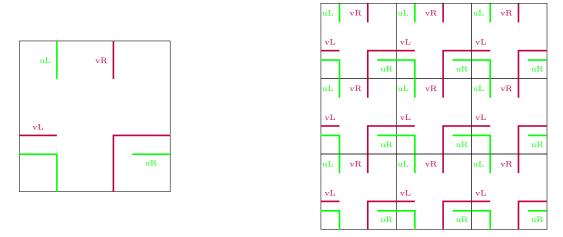

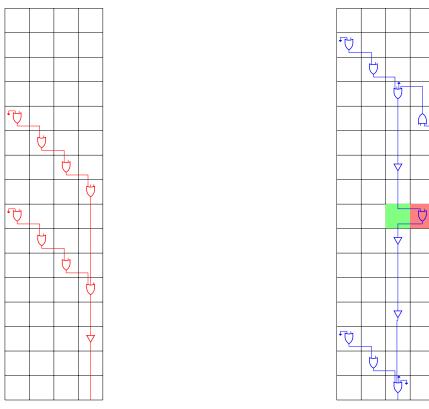

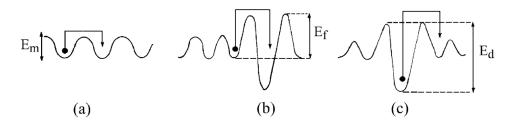

Figure 2.4: Two possible situations where there are two hits in a matrix when there are two projections: one along x and one along y. In Figure 2.4a four addresses are reconstructed, but whereas two of them are right (green ones) two are wrong (red ones). In Figure 2.4b only right addresses are reconstructed. In yellow, the pixels that would generate one of the signals actually seen.

The main issue when using pixel sensors, in comparison with microstrips, lies in their readout: It is relatively easy to access to charges on a long electrode by connecting to one of its ends, but in pixel sensors there are far more electrodes, and they are smaller and distributed throughout the array, hence difficult to reach. There are three approaches pursued to readout a pixel sensor, as is discussed in the next sections: Charge-Coupled Devices (CCDs), hybrid devices, and Monolithic Active Pixel Sensors (MAPS). Historically, in 1982, a Rutherford Laboratory Group showed that a CCD can be used to successfully measure the position of minimum ionising particles [41]: the first pixel silicon tracker.

#### Silicon pixel performances

When comparing the performances of different silicon pixel sensors, the following parameters are important to take into account:

• Efficiency: an ideal tracker can detect any particle that crosses it; a physical tracker will miss some of them. Efficiency depends both on the sensitive fraction of the sensor and on the noise level: the higher the noise, the harder it is to recognise the true signal generated by an impinging particle;

- Minimum energy: the more energy is deposited in the silicon lattice, the more likely it is for the sensor to actually detect the particle passage. The ideal tracker in most HEP experiments is meant to detect Minimum Ionising Particles (MIPs): charged particles with a high enough energies to deposit the minimum quantity according to the Bethe-Bloch equation<sup>2</sup>. This minimum energy threshold is usually dependent on electronic noise of the readout chain and the pixel capacitance;

- Energy deposit resolution: some pixel trackers also provide information regarding the energy deposited by the ionising particle along its passage through the sensor. This information has its own resolution, depending on many factors, such as the linearity of the sensor collection capacity (as a reference number, ATLASPix has an energy resolution of 7% at 30 keV [51]);

- Spatial resolution: the main purpose of the tracker is to measure the position of the impinging particle. In the case of silicon pixels, this information is bi-dimensional (and the third dimension can be inferred by the sensor positioning). The precision over the axes defines the spatial resolution. This number must match the one required by the experiment<sup>3</sup>. The main contribution to the spatial resolution of a pixel tracker is the size of the pixels, also called **pitch**. A good pixel sensor for charged particles can reach a spatial resolution of about 1.5 µm [52];

- **Timing resolution**: whenever a signal is generated in the sensor, a time label is also associated with the spatial variable. Depending on various conditions, such as the signal shaping circuitry and the free charges collection speed, the timing resolution varies. The most precise silicon pixels now approach what is called 4-dimensional tracking, i.e., a really good precision also on the timing dimension, reaching resolutions of the order of 30 ps [53];

- Power consumption: the sensor functioning consumes energy. The lower the power consumption, the better it is for all the applications. Some experiments have very strict constraints: this is the case of space, where the available power is limited and the heat dissipation in vacuum is very challenging, and the case of HEP, where the power consumption translates into potentially thick dissipation systems. ALPIDE is one of the best performing sensors from this point of view, and has a power consumption around 35 mW cm<sup>-2</sup> [54];

- Rate capability: a pixel sensor is able to correctly identify and distinguish particles up to a certain flux, beyond which the pileup can lead to incorrect or incomplete hits readout. The maximum rate a device is expected to withstand is important in choosing a suitable detection technique. One of the highest-whithstanding silicon pixel tracker is CMS inner tracker, able to disentangle up to  $6 \times 10^8$  particles per second per square centimeter [55];

- Material budget: in several applications, tracking is but a part of the overall measurement to perform on the particle; hence, the tracker must be nondestructive. Nev-

<sup>&</sup>lt;sup>2</sup>For silicon, a MIP deposits  $388 \text{ eV } \mu\text{m}^{-1}$  [49], hence it creates on average about 108 electrons per  $\mu\text{m}$  but, most of the times, a value closer to 75 per  $\mu\text{m}$ , as the distribution is Landau-shaped [50].

<sup>&</sup>lt;sup>3</sup>In some applications, e.g., spectroscopy, information on the particle energy is retrieved through a position measurement, therefore in these cases the spatial resolution of the detector strongly affects the energy resolution of the experiment.

ertheless, the passage of the impinging particle inside the tracking system inevitably perturbs and degrades the particle kinematics, as the physical process of detection requires some energy deposition in silicon. As a rule of thumb, the thinner the tracking system, the less the kinematic degradation (as a reference, ALPIDE innermost layers have a material budget of 0.3%, meaning that the detector depth equivalent thickness is 0.3% of the radiation length  $X_0$ );

• Radiation hardness: the detector is subject to radiation during its operation; over time, the radiation to be detected also damages the sensor, worsening its performance. Damage to the device can be measured in terms of total ionisation dose effects and bulk damage effects. Some devices are more radiation resistant than others. As a reference, for HL-LHC [48] CMS tracker is expecting a Non-Ionising Energy Loss (NIEL) up to  $2 \times 10^{16}$  1 MeV  $n_{eq}/cm^2[56]$ ; the collaboration is already addressing such an issue studying radiation-resistant possibilites [57].

In actual silicon pixel sensor implementations, there is a trade-off between these characteristics. The numbers reported here as references show some of the best performances of silicon pixel sensors for a given quantity, but many refer to different sensors. This is because it is highly unlikely for a sensor developed for extremely good timing resolution to be also low power-consuming, or to have a great radiation hardness; and similar correlations exist between all the quantities introduced. Sensor development must be fine-tuned with the target application.

### 2.2 Pixel sensors types

To address the issue of accessing the electrodes on the pixels, various approaches have been developed. In this section, the three most widely-used methods are introduced: CCDs, hybrid devices, and MAPS.

Before discussing how to move the information on the array, it is necessary to clarify what the information actually is. There are two different types of silicon pixel trackers: **analogue** and **digital** ones. In the analogue case, the information is the height of a voltage signal proportional to the energy deposited in the sensitive region of the silicon; in the digital case, on the other hand, this height is compared to a set of thresholds, and a digital word represents the highest threshold that is lower than the signal itself. This work focuses on digital pixel trackers, in particular with a **binary readout**: only one threshold is present for every pixel; therefore, the information is just whether an ionsing particle passed through a given pixel or not; this is called **binary hit/no-hit fashion**.

#### CCD

CCD stands for Charge-Coupled Device and represents a way to move data along a physical space. CCDs were invented in the 1970s [58] and were actually developed for memories, but later their most famous application was found in imaging (and tracking).

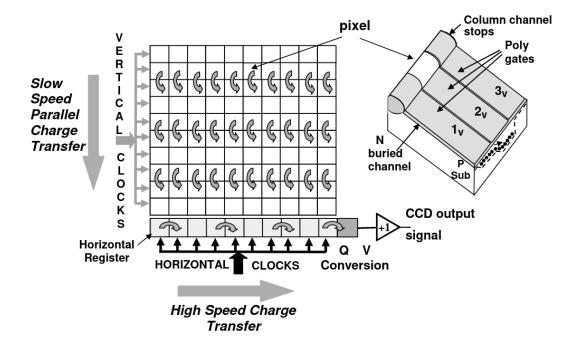

Once the charge is collected in the pixel, it is momentarily saved in a built-in capacitance and stored only when created within a specific time window, named the integration time. When the device is not sensible anymore, a voltage difference is produced row by row to start the flowing of electrons toward the higher voltage. If the voltage is set correctly, the electrons move from one pixel to the one below until they reach a readout node at the end of the array, where this charge signal is converted to a voltage signal and digitised. A scheme of the CCD working principle is reported in Figure 2.5: electrons are slowly moved toward the bottom row where a high speed charge transfer brings them to the bottom right of the device, where their voltage signal is finally read. For CCDs, as in microstrips, the front end is external. The signal read from the single pixel is a charge signal, and is later processed properly before the connection to the computer.

Figure 2.5: A schematic of CCD readout principle. In this scheme, information is transported vertically up to the bottom lane, where is transported from left to right to the readout pixel. Taken from [59].

#### Hybrid devices

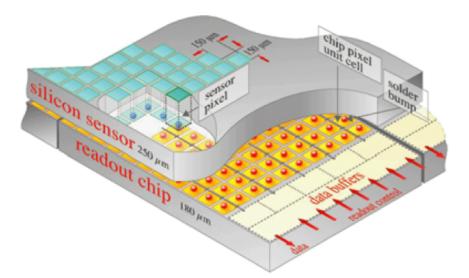

An alternative approach to moving the charge towards the edge of the array is to read each pixel directly, similarly to what is done for microstrip sensors. This pushes the need for a structure, separated from the sensor itself, that connects to it pixel-by-pixel.

This is exactly the approach of hybrid devices: an ASIC (Application-Specific Integrated Circuit) is developed with the same size of the device, the same pitch, and the proper pads to connect to the sensor. Then, this ASIC is aligned with the pixel sensor, and metal-bump bonds are created to connect independently every pixel of the device. This approach was

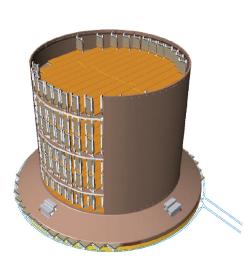

made possible by several advances in the field of assembly; the most recent technologies allow microbumps as wide as  $2.5 \,\mu\text{m}$  that are only  $5 \,\mu\text{m}$  apart [60]. In Figure 2.6 a representation of a hybrid pixel detector is shown.

Figure 2.6: A schematic of a hybrid pixel detector. The silicon section is bonded with the readout chip (at least) once for every pixel. Taken from [55].

#### MAPS

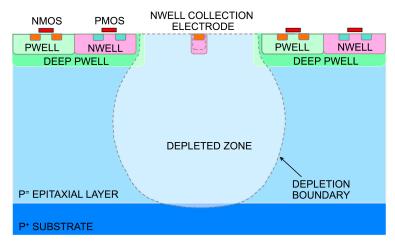

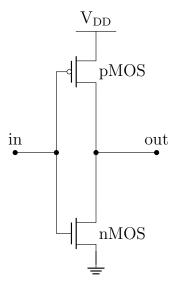

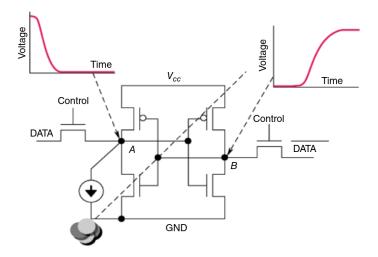

Another possibility to create a silicon pixel tracker is to take advantage of the peculiar properties of silicon as a material. Silicon implanted with pn-junctions, good for the detection of charged particles when depleted, can also host transistors capable of creating both analogue and digital circuits; i.e. both detectors and nMOS/pMOS structures are created on the same die of silicon. This is commonly referred to as CMOS (Complementary Metal-Oxide-Silicon) imaging technology. More details on CMOS circuits are given in Section 4.1.1.

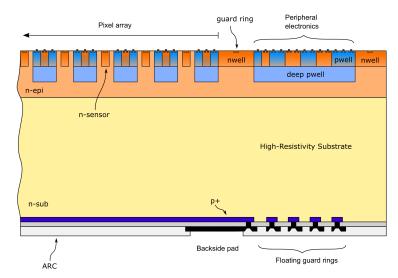

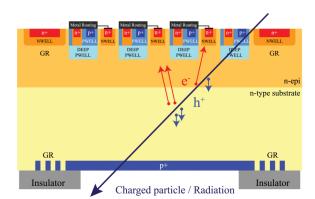

This technology is capitalised to create MAPS: Monolithic Active Pixel Sensors (also called CMOS sensors): there is no external ASIC as in hybrid implementations, but the very same silicon device that performs the detection of the particle also implements the logic necessary to amplify, transport, and interpret the charge signal correctly. A MAPS actually works as a standalone object: when it is operated correctly, it performs all the operations needed for tracking from the charge creation up to the digitisation of the signal. An example of a MAPS cross section can be seen in Figure 2.7, where transistors can be seen on top of the sensitive region. These transistors are used to implement all the operations needed for tracking hybrid is an example of **readout integration**: the readout does not require an external device, but the signal is already read from the sensor as pre-processed and ready for analysis.

**Figure 2.7:** Cross section of TowerJazz 0.18 µm CMOS process for imaging. Taken from [61].

#### Pros and cons

Over the years, all three different flavours have been used, but as of yet there is no one technique that clearly prevails over the others. The CCD approach dominated the market until  $\sim 20$  years ago, and is currently used mainly for X-rays tracking; at the moment of writing, most nuclear and HEP applications use hybrid detectors or MAPS, while many astroparticle experiments continue to use CCDs.

The main differences are the following:

- in a CCD all pixels are usually read, while with hybrid devices or MAPS it is possible to take advantage the **sparsification** of data: the fact that a passing particle usually creates signals on a relatively small number of pixels, much lower than the total number of pixels of the device; MAPS and hybrids enable optimised transmission of data;

- CCD and hybrid quantum efficiency is usually better, as the CMOS technique needs to occupy part of the sensitive area with the transistors;

- Hybrid devices have the worst material budget as the material of the sensor plane is then followed by the additional material of the readout ASIC. In the other two cases, the impinging particle only passes through the one sensor plane;

- MAPS and hybrid devices have the lowest power consumption, as only useful information is transported to the outside of the sensor and there is no need to swap often voltages like in CCDs;

- Hybrid devices have the worst pixel pitch: whereas it is possible to exploit industrial processes to create very small pixels into CCDs and MAPS, it is quite hard to create such small pixels in hybrid devices, due to the technological limits of the bonding process (some very recent developments implemented bonds with a pitch as small as 3 µm, partly solving these limitations for hybrid solutions [62]);

- MAPS are considered the cheapest options, as their production is cheaper than CCDs [63]–[65] and, compared to hybrid solutions, there is no need to develop an ASIC and then bond it;

- CCDs are usually slower than MAPS or hybrid devices, as the information must travel queued through the whole sensor.

- Hybrid design allows for a great level of versatility, as the same readout ASIC can be used in multiple experiments simply swapping the sensor plane; on the other hand, they usually suffer from a higher electrical noise, due to the parasitic capacitance introduced by the bump bonds connecting the sensor to the electronics.

- Hybrid designs usually show good radiation tolerance, MAPS show intermediate behaviour, and CCDs are very sensitive to radiation degradation. This is mostly due to to the fact that the architecture in a CMOS circuit (implemented either in the sensor itself in a MAPS or in an external ASIC) is designed to be radiation-resistant, while in CCDs this degree of freedom is not possible.

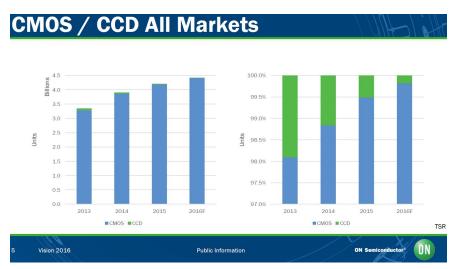

Looking at the consumer applications in Figure 2.8, dominated by the sensors in the visible range used for cameras, almost all recent imaging applications employ CMOS, mainly for power and price reasons.

Figure 2.8: Comparison between CCD and CMOS (MAPS) market in industry few years ago. Taken from Vision Show – Stuttgart, 2016, public information [66].

## 2.3 Silicon pixels development

In this section, the three fields that must be studied in order to design, from scratch, a new silicon pixel tracker are listed: silicon design, analogue architecture design, and digital design. Usually, in many scientific collaborations developing a silicon pixel tracker, there is a team of several researchers responsible for each of these design tasks.

#### Sensor Design

The term sensor design, in this work, refers to the operation of defining the physical structures implementing the actual sensing process in the device; i.e., the creation of the silicon diode that implements the depleted region. When designing a silicon tracker, there are few parameters that must be taken into account. The main ones are the following:

- Thickness: The thicker the device, the more charge carriers a charged particle creates during its passage. A thicker sensor translates into better efficiency but worse material budget;

- Depletion or diffusion: the free charges can reach the collection electrode either by diffusion or can be forced to do so using a guiding electric field. In the latter case, the time resolution greatly improves, but it is harder to obtain larger sensitive regions;

- Doping: by changing the doping levels of the various layers, as well as their size and shape, it is possible to mould the electric field and engineer the detector performance parameters (efficiency, rate capability, timing and spatial resolution, radiation resistance, etc...);

- Amplification: some sensors provide in-pixel charge amplification to improve the efficiency and the timing performances.

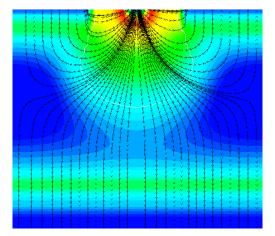

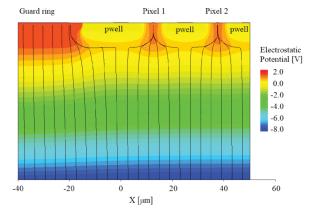

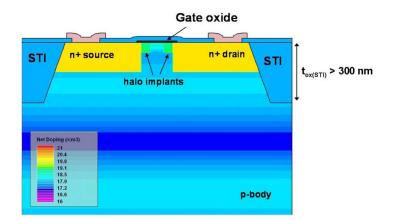

There are a great number of researchers and collaborations developing new ideas and alternatives to well-known paradigms in order to optimise all these parameters and improve the overall performance of silicon pixel sensors. Sensor designers usually make use of complex **T**ecnhological Computer-Aided Design (TCAD) software and shape the electric field to maximise the charge collection while minimising interference with the downstream circuitry. In Figure 2.9 a simulation of the cross section of an imaging sensor, in this case ALPIDE one. The structure of the field lines is optimised to grant fast charge collection.

Figure 2.9: A TCAD simulation of ALPIDE pixel. Taken from [67].

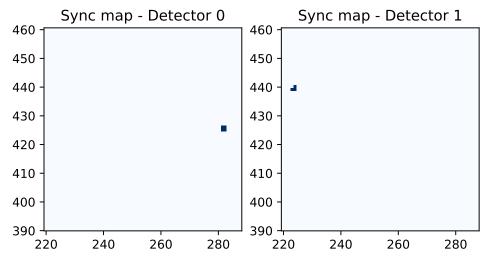

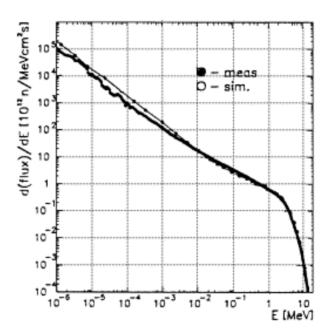

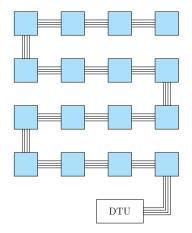

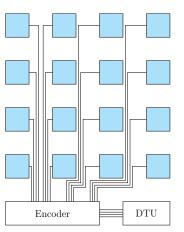

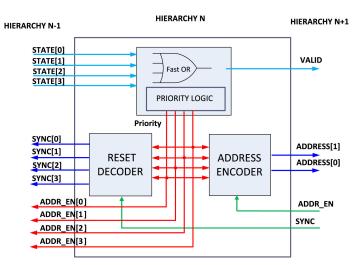

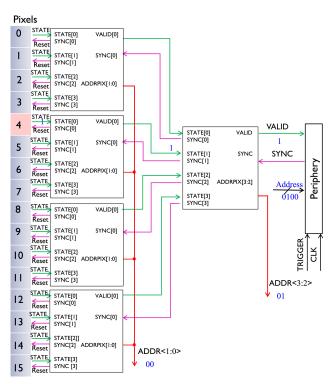

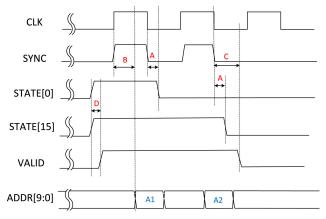

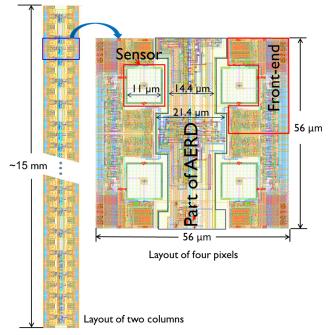

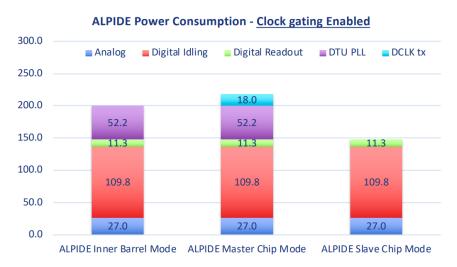

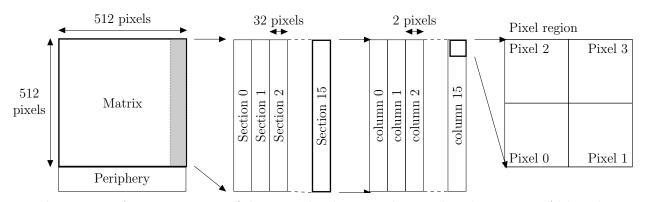

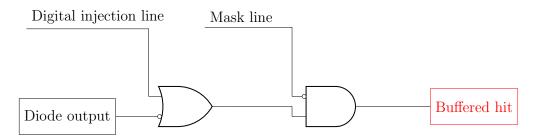

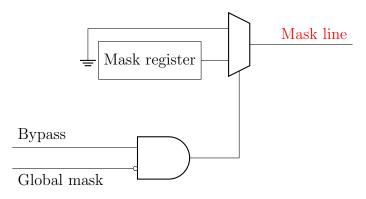

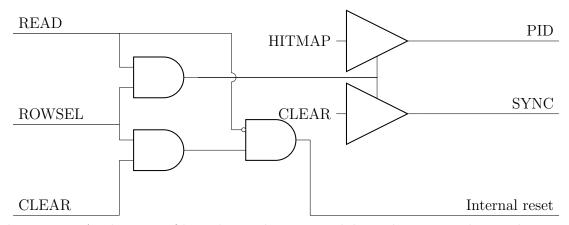

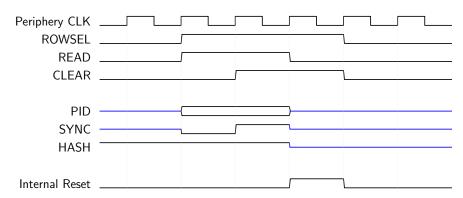

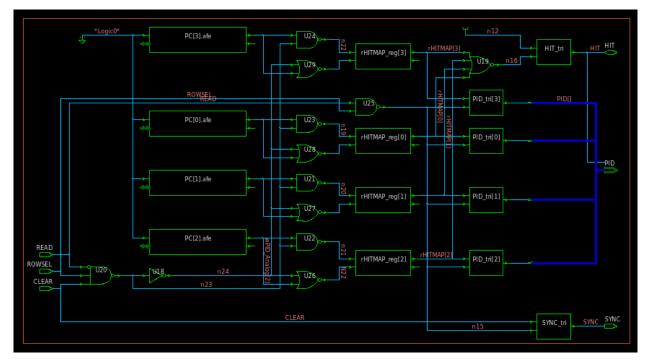

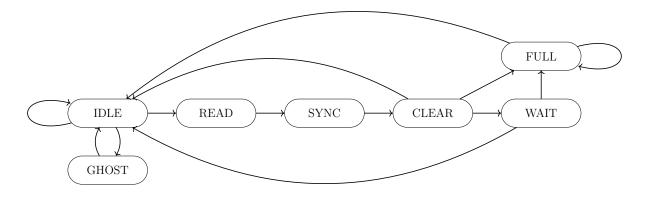

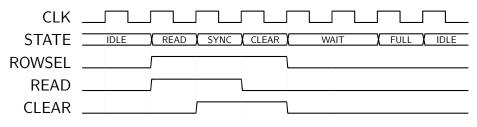

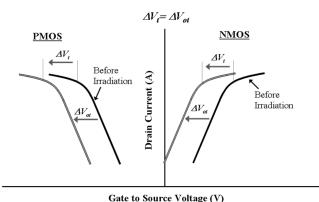

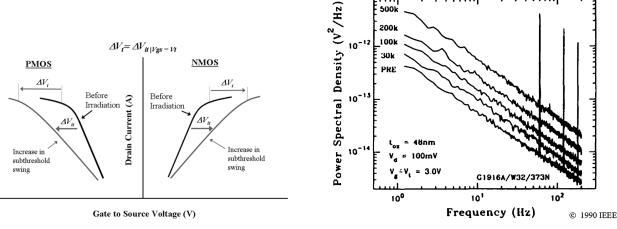

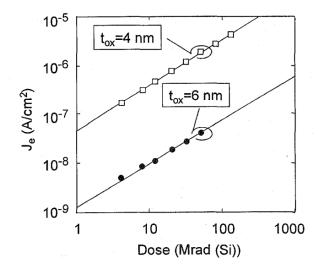

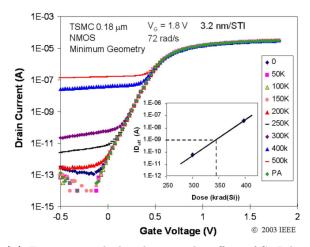

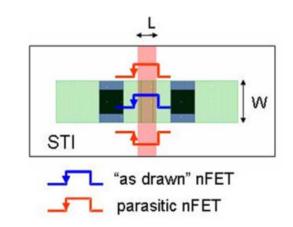

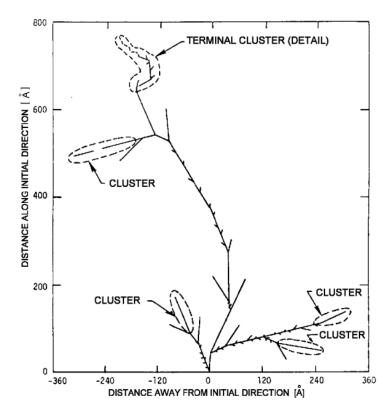

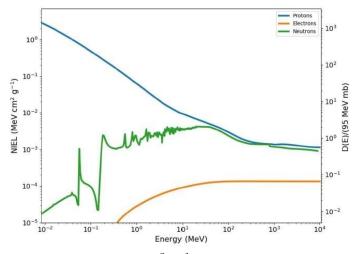

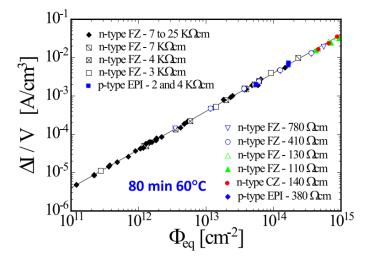

#### Analogue Design