## **LETTER • OPEN ACCESS**

## Analysis of threshold voltage instabilities in semi-vertical GaN-on-Si FETs

To cite this article: Kalparupa Mukherjee et al 2020 Appl. Phys. Express 13 024004

View the <u>article online</u> for updates and enhancements.

https://doi.org/10.35848/1882-0786/ab6ddd

## Analysis of threshold voltage instabilities in semi-vertical GaN-on-Si FETs

Kalparupa Mukherjee<sup>1\*</sup>, Matteo Borga<sup>1</sup>, Maria Ruzzarin<sup>1</sup>, Carlo De Santi<sup>1</sup>, Steve Stoffels<sup>2</sup>, Shuzhen You<sup>2</sup>, Karen Geens<sup>2</sup>, Hu Liang<sup>2</sup>, Stefaan Decoutere<sup>2</sup>, Gaudenzio Meneghesso<sup>1</sup>, Enrico Zanoni<sup>1</sup>, and Matteo Meneghini<sup>1</sup>

<sup>1</sup>University of Padova, Department of Information Engineering, Via Gradenigo 6/B, 35131 Padova, Italy

Received December 20, 2019; revised January 10, 2020; accepted January 19, 2020; published online January 30, 2020

We present a first study of threshold voltage instabilities of semi-vertical GaN-on-Si trench-MOSFETs, based on double pulsed, threshold voltage transient, and UV-assisted C-V analysis. Under positive gate stress, small negative  $V_{th}$  shifts (low stress) and a positive  $V_{th}$  shifts (high stress) are observed, ascribed to trapping within the insulator and at the metal/insulator interface. Trapping effects are eliminated through exposure to UV light; wavelength-dependent analysis extracts the threshold de-trapping energy  $\approx$ 2.95 eV. UV-assisted CV measurements describe the distribution of states at the GaN/Al<sub>2</sub>O<sub>3</sub> interface. The described methodology provides an understanding and assessment of trapping mechanisms in vertical GaN transistors. © 2020 The Japan Society of Applied Physics

ertical GaN technology  $^{1-15)}$  is developing rapidly and, in particular, trench-MOSFETs  $^{8-13)}$  are attracting an ever increasing attention owing to their potential applications in the power conversion field. 16) For continued growth of this technology, the study and minimization of threshold instabilities is a fundamental step. Al<sub>2</sub>O<sub>3</sub> dielectrics have emerged as a dominant choice for developing vertical MOS technologies.<sup>17,18)</sup> Recent works<sup>19,20)</sup> indicate three prevalent trapping locations within the Al<sub>2</sub>O<sub>3</sub>/GaN MOS devices, responsible for  $V_{\rm th}$  shift: (i) states within the bulk dielectric, (ii) near-interface or border sites, and (iii) states along the oxide/ GaN interface. While the presence of the former two are oxidedependent, the interface state density  $(D_{it})$  reflects the quality of the dielectric/semiconductor boundary, and of the process. Despite the importance of these trapping processes, these aspects have been studied only preliminarily by previous reports, 17,21,22) and a comprehensive description still needs to be published.

The aim of this paper is to contribute to an improved understanding of  $V_{\rm th}$  shift in semi-vertical GaN devices, and to provide in-depth perspectives on the physical origin of the trapping processes. To this aim, we integrated several analytical techniques to investigate the trapping processes and the associated recovery dynamics: pulsed measurements, transient investigation, light-assisted de-trapping, capacitance–voltage measurements.

The original results obtained within this paper demonstrate that positive gate voltage stress can trigger multiple trapping mechanisms contributing to strong positive and weak negative  $V_{\rm th}$  shifts due to trap states across the metal/Al<sub>2</sub>O<sub>3</sub>/GaN layers. Light energies above 2.9 eV ( $\approx$ 0.8 eV from  $E_{\rm C}$ ) are found to assist in faster recovery from semi-permanent trapping states in the bulk oxide and/or interface. Photo assisted CV measurements yield the interface trapped charge distribution ( $D_{\rm it}$ ) for the gate stress of 5 V which indicates prevalence of shallow traps, located mostly at  $\leq$ 0.3 eV from the conduction band ( $E_{\rm C}$ ).

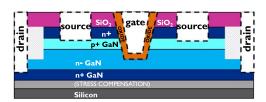

The devices are normally-off GaN trench MOSFETs grown on a silicon substrate by MOCVD,  $^{23)}$  with a 35 nm Al<sub>2</sub>O<sub>3</sub> dielectric. The epitaxial GaN layers include a stress compensation layer, a thick and lightly doped drift layer and a doped p-body (see. Fig. 1).

Fig. 1. (Color online) Structural schematic of the GaN-on-Si semi-vertical FET technology.

The device has a semi-vertical configuration. This term refers to the fact that the flow of current in the experimental structure is not fully vertical, since the drain current is collected laterally through a n+layer, and not vertically through the silicon substrate. The n+top layer (250 nm) sources the electrons which then flow vertically through the channel in the p+ GaN layer (400 nm) along the gate trench sidewalls to reach the n- GaN drift layer (750 nm). A highly doped drain n+ region is integrated in the epitaxial stack such that the current flows laterally through this layer, before being routed back to the surface through the drain metallization.

To preliminarily evaluate device dynamic behavior and stability of  $V_{\rm th}$  under positive gate stress, we performed double pulsed measurements<sup>24)</sup> that evaluate threshold instabilities within a short time scale ( $\mu$ s), thus capturing relatively fast trapping processes. The setup switches between quiescent ( $V_{\rm G,Stress}$ : 0–5 V for  $t_{\rm Q}$  = 100  $\mu$ s and  $V_{\rm D,Stress}$  = 0 V) and measurement ( $V_{\rm GS}$  = -1 to 7 V at  $V_{\rm DS}$  = 8 V,  $t_{\rm meas}$  = 1  $\mu$ s) conditions.

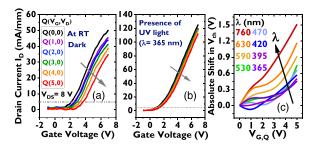

Figure 2 displays the corresponding  $I_{\rm D}$ – $V_{\rm G}$  behavior for the cumulative stress procedure on a typical device. The threshold voltage is defined as the voltage intercept at  $I_{\rm D}=5~{\rm mA~mm^{-1}}$  which reflects a clear trend with change in  $V_{\rm G,Q}$ . The results emphasize a monotonic increase in  $V_{\rm th}$  with higher quiescent  $V_{\rm G}$ , with a maximum positive  $\Delta V_{\rm th} > 1.2~{\rm V}$  for  $V_{\rm G,Q}=5~{\rm V}$  in Fig. 2(a). This high  $\Delta V_{\rm th}$  arises from (i) the fast pulsed measurement configuration and (ii) the absence of recovery intervals between increments in quiescent stress  $V_{\rm G,Q}$ . The shifts are semi-permanent with only 10%–20% recovery after several minutes following  $V_{\rm G,Q}=5~{\rm V}$ .

<sup>&</sup>lt;sup>2</sup>Imec, Kapeldreef 75, Heverlee 3001, Belgium

<sup>\*</sup>E-mail: mukherjee@dei.unipd.it

Fig. 2. (Color online) (a) Double pulsed  $I_D$ – $V_G$  curves for various quiescent voltages at room temperature under dark conditions (b) with UV light. (c) Extracted  $\Delta V_{\text{th}}$  under light of different wavelengths.

Typically, it could take from several hours to days to achieve 80%–90% recovery in  $V_{\rm th}$ .

When the experiment was repeated under exposure to high energy photons, as presented in Figs. 2(b) and 2(c),  $\Delta V_{\rm th}$  is found to be smaller with a distinct wavelength dependence [see. Fig. 2(c)]. Under UV light,  $I_{\rm D}$ – $V_{\rm G}$  drifts are reduced, and  $\Delta V_{\rm th}$  falls to a substantially smaller value,  $\approx$ 0.45 V for  $V_{\rm G,Q}=5$  V. [see. Fig. 2(b)]. These observations strongly suggest the presence of slow-emitting trap states (de-trapping times >300 s) which could be either (1) bulk states spatially located deeper within the oxide or (2) interface states energetically located deeper within the bandgap. Quick detrapping from such states would only be possible only through external illumination.

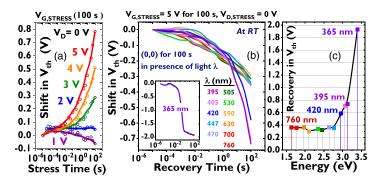

To better investigate the semi-permanent nature of the positive  $V_{\rm th}$  shift under high fields, we employed a versatile setup capable of accurately evaluating threshold transients in the  $10~\mu s$ –100~s range,  $^{18,25,26)}$  and re-evaluated  $V_{\rm th}$  transients under monochromatic light excitation. Here, a typical measurement is composed of a stress and a recovery phase of 100~s each, during which  $V_{\rm th}$  evolution is extracted from 22 fast  $I_{\rm D}$ – $V_{\rm G}$  measurements ( $t_{\rm meas}=10~\mu s$ ). Figure 3(a) presents the stress phase  $V_{\rm th}$  transients obtained for  $V_{\rm G,Stress} \le 5~V$ , where stress phases are separated by recovery intervals at ( $V_{\rm G},V_{\rm D}=0~V,~0~V$ ). To describe the energetic distribution of slow-emitting traps responsible for the positive  $\Delta V_{\rm th}$ , Fig. 3(b) illustrates recovery phase  $V_{\rm th}$  transients at ( $V_{\rm G},V_{\rm D}=0~V,~0~V$ ) for measurements under light of  $\lambda=365$ – $760~{\rm nm}$ , following equivalent stress phases ( $100~{\rm s}$  at  $V_{\rm G,Stress}=5~V$ ).

From Fig. 3(a), we discern a negative  $V_{\rm th}$  shift trend ( $\approx 0.07~{\rm V}$  at 100 s) induced during the low gate stress of  $V_{\rm G,Stress}=1~{\rm V}$ , and also weakly observed for  $V_{\rm G,Stress}=2~{\rm V}$ . Similar small negative  $V_{\rm th}$  shifts were noticed for several

devices, for stress times >10 s, under  $V_{\rm G,Stress} \le 2$  V conditions. This negative shift is not observable in the previous double pulsed measurements because other mechanisms (contributing to positive  $\Delta V_{\rm th}$ ) probably dominate for the relatively fast stress/measurement intervals chosen [total  $t_{\rm Stress}$  at a given  $V_{\rm G}$ , Q builds up to only  $40 \times 100~\mu \rm s = 4$  ms for the 40 point  $I_{\rm D}V_{\rm G}$  curves in Fig. 2(a)]. The negative  $\Delta V_{\rm th}$  trend at low stress biases can be ascribed to de-trapping of electrons from pre-existing states in the dielectric towards the metal.  $^{17,27)}$

$V_{\rm G,Stress}=3~{\rm V}$  and higher induce positive  $V_{\rm th}$  shifts, proportional to the stress bias and time. In the full timerange between  $10~\mu{\rm s}$  and  $100~{\rm s}$  of a single  $V_{\rm G,Stress}=5~{\rm V}$  phase, a strong positive  $\Delta V_{\rm th}\sim 0.75~{\rm V}$  [Fig. 3(a)] is induced. Under dark conditions, this shift is only partially recoverable (calculated from negative shifts in  $V_{\rm th}$  during the recovery phase, absolute recovery  $\sim 0.35~{\rm V}$ ) within the  $100~{\rm s}$  recovery window following the stress (not shown). A potential mechanism has been reported in other work, where the recoverable degradation component has been attributed to electron injection from GaN into border traps close to the  ${\rm Al_2O_3/GaN}$  interface, aligned near  $E_{\rm C}$ . On the removal of stress and restoration of the Fermi level, these traps would reemit to the GaN layer.

However, especially for high  $V_{G,Stress}$ , recovery is dependent on a dominantly slow detrapping process. It can be hypothesized that under high stress fields, in addition to the contribution of border and interface traps, injected electrons from the GaN channel can travel further into the oxide or occupy energetically deeper trap states. Recovery from such traps could take days or weeks to complete, since electrons are semi-permanently stored in the insulator. To better capture this behavior, de-trapping during the recovery phase is accelerated through exposure to high energy photons, as presented in Fig. 3(b). The recovery phases for each wavelength in Fig. 3(b) are preceded by equivalent 100 s stress phases at  $V_{G,Stress} = 5 \text{ V}$ . Thus, the recovery behavior at each  $\lambda$  describes the device response after an induced positive  $\Delta V_{\rm th} \approx 0.75 \, \text{V}$ . The threshold energy for enhanced de-trapping, corresponding to the lowest energetic position of deep bulk states, appears to be 2.95 eV [420 nm, Fig. 3(c)]. A complete  $\Delta V_{\rm th}$  recovery i.e. negative  $V_{\rm th}$  shift  $\approx 0.75 \, {\rm V}$  is achieved within 100 s with 395 nm [3.1 eV, Fig. 3(b)]. Thus, the presence of trap states between these energies: 2.9–3.1 eV  $(\approx 0.8-1.0 \text{ eV from } E_{\text{C}}, \text{ considering a Al}_2\text{O}_3/\text{GaN } E_{\text{C}} \text{ offset}$  $=2.16 \,\mathrm{eV}^{29}$ ) can be recognized (see Fig. 4).

Fig. 3. (Color online) (a) Time transients  $V_{\rm th}$  method. (a) Shift in  $V_{\rm th}$  ( $V_{\rm th}-V_{\rm th@10}$   $_{\mu\rm s}$  during stress phase) during (100 s) stress and varying  $V_{\rm G.Stress.}$  (b)  $V_{\rm th}$  evolution ( $V_{\rm th}-V_{\rm th@10}$   $_{\mu\rm s}$  during recovery phase of 100 s), following a stress phase: 5 V for 100 s, correlation with de-trapping energies during light-assisted recovery with  $\lambda=365$ –760 nm. (c) absolute  $V_{\rm th}$  shift during recovery ( $V_{\rm th@100s}-V_{\rm th@10\mu s}$  during recovery) under different monochromatic light.

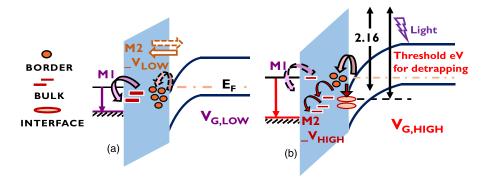

Fig. 4. (Color online) Energy band diagrams illustrating trapping locations in the Metal/Al<sub>2</sub>O<sub>3</sub>/GaN system (a) mechanisms activated at low  $V_{\rm G}$  stress. M1: negative  $\Delta V_{\rm th}$  due to detrapped electrons from oxide towards metal. M2\_ $V_{\rm LOW}$ : moderate and recoverable positive  $\Delta V_{\rm th}$  due to injection of electrons from GaN accumulation into the border oxide traps. (b) Mechanisms strengthened at high gate stress, M2\_ $V_{\rm HIGH}$ : strong positive  $\Delta V_{\rm th}$  due to electrons injection into energetically deeper interface traps or bulk states in the dielectric. M2\_ $V_{\rm HIGH}$  causes semi-permanent trapping which requires external light energy (induce detrapping) for achieving fast recovery of  $V_{\rm th}$ .

UV light (3.39 eV) has sufficiently high energy to remove the trapped electrons and create free carriers. It is worth noticing that the negative  $V_{\rm th}$  shift measured with UV light [1.93 V, inset in Fig. 3(b)] overcompensates stress-induced positive drifts, indicating the de-trapping of states that—under rest conditions—are located under the Fermi level. Once dark conditions are restored, such states would gradually re-trap, corresponding to the stable device  $V_{\rm th}$ .

Thus, from the measurements in Figs. 2–3, the mechanisms contributing to  $V_{\rm th}$  shifts in these devices can be summarized as illustrated in Fig. 4.

- (i) For low voltage ( $V_G \le 2 \text{ V}$ ), a small negative  $V_{\text{th}}$  shift (<0.1 V) is attributed to the de-trapping of electrons from gate insulator towards the metal [Mechanism M1 in Fig. 4(a)].

- (ii) For medium to high stress voltages (2 V <  $V_{\rm G}$  < 4 V), in addition to M1, positive  $\Delta V_{\rm th}$  ( $\approx$ 0.2–0.3 V) due to electron trapping from the semiconductor towards border states in the dielectric [Mechanism M2\_ $V_{\rm LOW}$  in Fig. 4(a)] becomes relevant. This process is reversible on removal of the stress.

- (iii) For high stress voltage ( $V_{\rm G} > 4$  V), strong positive  $V_{\rm th}$  shifts (>0.5 V) are dominant, and recovery becomes significantly slow (several hours to days). This is attributed to the aggravation of M2 [M2\_V<sub>HIGH</sub> in Fig. 4(b)] under high fields, involving electron transport from the GaN channel towards the metal, inducing trapping into deep states, along the interface or in the bulk of the dielectric. Even when stress is removed, deeper trap levels remain occupied. Exposure to light with energy higher than  $\approx$ 2.9 eV is essential to enable accelerated recovery.

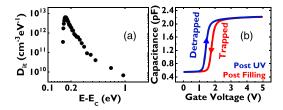

Finally, we employ the photo-assisted capacitance–voltage or UV-CV<sup>30)</sup> method that evaluates the distribution of interface states,  $D_{\rm it}$ , as illustrated in Fig. 5.

Devices are exposed to UV light for  $50 \, \mathrm{s}$  in depletion in order to empty all electron traps, followed by  $500 \, \mathrm{s}$  in the dark to allow excess carriers to leave the system. Then, the de-trapped CV curve is measured [see. Fig. 5(b)] from 0 to 5 V. Bias at  $V_{\rm G} = 5 \, \mathrm{V}$  is maintained for a moderate stress time of  $80 \, \mathrm{s}$ , so as to induce charge trapping at insulator and interface but without significant alteration of the capacitance level. Finally, the C-V curve of the trapped device is measured. The  $D_{it}$  profile reported in Fig. 5(a) can be

Fig. 5. (Color online) UV-CV method for  $D_{\rm it}$  extraction. (a) Electron  $D_{\rm it}$  versus  $E_{\rm G}$  (b) C–V comparison between detrapped (after UV light) and trapped state.

computed from the experimental data in Fig. 5(b) by using the procedure and the equations described in Ref. 30. The major parameters important for accurate calculation of  $D_{it}$  are the displacement between the detrapped and trapped C-Vcurves, oxide area, and the effective doping of the semiconductor channel. The difference in slope allows the extraction of  $D_{it}$  for trap energies across the entire GaN bandgap, whereas the rigid shift in the curves is proportional to the amount of charge trapped in the bulk of the oxide and/ or in border traps. This paper presents a detailed investigation into the threshold voltage instability of GaN-on-Si semivertical FETs. Based on combined electrical and optical measurements, we identify different mechanisms as responsible for  $V_{\rm th}$  shift: (i) at low stress voltages, a negative  $V_{\rm th}$ shift (M1 in Fig. 4) is observed, possibly related to detrapping of electrons from oxide states; (ii) at intermediate voltages, a moderate positive  $V_{\text{th}}$  shift (M2\_ $V_{\text{LOW}}$  in Fig. 4), which is fully recoverable, has been associated to electron injection from the channel to near interface or border traps; (iii) at higher voltages, trapping might extend to deeper energy states or further into the dielectric bulk, which would yield greater V<sub>th</sub> shifts (M2\_V<sub>HIGH</sub> in Fig. 4) with substantially longer de-trapping constants. Tests under different wavelengths were used to identify the threshold energy for de-trapping: the results identify the presence of deep-trap states within the insulator (threshold energy between 2.95 and 3.1 eV), that can be responsible for the semi-permanent trapping seen at high stress voltages. The results presented within this paper describe the dominant trapping processes for GaN-on-Si semi-vertical FETs, and general guidelines for the analysis of the related mechanisms, thus complementing the current knowledge on GaN vertical stability and reliability.<sup>31)</sup>

Acknowledgments This project has received funding from the ECSEL Joint Undertaking (JU) under grant agreement No. 826392. The JU receives support from the European Union's Horizon 2020 research and innovation programme and Austria, Belgium, Germany, Italy, Norway, Slovakia, Spain, Sweden, Switzerland. This research activity was partly funded by project "Novel vertical GaN-devices for next generation power conversion", NoveGaN (University of Padova), through the STARS CoG Grants call.

ORCID iDs Kalparupa Mukherjee https://orcid.org/0000-0003-1387-3321 Matteo Borga https://orcid.org/0000-0003-3087-6612 Carlo De Santi https://orcid.org/0000-0001-6064-077X

- K. J. Chen, O. Haberlen, A. Lidow, C. L. Tsai, T. Ueda, Y. Uemoto, and Y. Wu, "GaN-on-Si power technology: devices and applications," IEEE Trans. Electron Devices 64, 779 (2017).

- Y. Zhang, M. Sun, D. Piedra, J. Hu, Z. Liu, Y. Lin, X. Gao, K. Shepard, and T. Palacios, "1200 V GaN vertical fin power field-effect transistors," 2017 IEEE Int. Electron Devices Meeting (IEDM), 2017, pp. 9.2.1–9.2.4.

- J. Ma and E. Matioli, "High performance Tri-Gate GaN power MOSHEMTs on silicon substrate," IEEE Electron Device Lett. 38, 367 (2017).

- 4) X. Li, M. Van Hove, M. Zhao, K. Geens, V.-P. Lempinen, J. Sormunen, G. Groeseneken, and S. Decoutere, "200 V Enhancement-Mode p-GaN HEMTs fabricated on 200 mm GaN-on-SOI with trench isolation for monolithic integration," IEEE Electron Device Lett. 38, 918 (2017).

- M. Sun, Y. Zhang, X. Gao, and T. Palacios, "High-Performance GaN vertical fin power transistors on bulk GaN substrates," IEEE Electron Device Lett. 38, 509 (2017).

- 6) T. Oka, Y. Ueno, T. Ina, and K. Hasegawa, "Vertical GaN-based trench metal oxide semiconductor field-effect transistors on a freestanding GaN substrate with blocking voltage of 1.6 kV," Appl. Phys. Express 7, 021002 (2014).

- 7) D. Shibata, R. Kajitani, M. Ogawa, K. Tanaka, S. Tamura, T. Hatsuda, M. Ishida, and T. Ueda, "1.7 kV/1.0 mΩ cm² normallyoff vertical GaN transistor on GaN substrate with regrown pGaN/AlGaN/GaN semipolar gate structure," 2016 IEEE Int. Electron Devices Meeting (IEDM), 2016, pp. 10.1.1–10.1.4.

- 8) W. Li, K. Nomoto, K. Lee, S. M. Islam, Z. Hu, M. Zhu, X. Gao, M. Pilla, D. Jena, and H. G. Xing, IEEE Trans. Electron Devices 65, 2558 (2018).

- J. Hu, Y. Zhang, M. Sun, D. Piedra, N. Chowdhury, and T. Palacios, Mater. Sci. Semicond. Process. 78, 75 (2018).

- 10) C. Liu, R. A. Khadar, and E. Matioli, IEEE Electron Device Lett. 39, 71 (2017).

- R. A. Khadar, C. Liu, R. Soleimanzadeh, and E. Matioli, IEEE Electron Device Lett. 40, 443 (2019).

- 12) H. Otake, K. Chikamatsu, A. Yamaguchi, T. Fujishima, and H. Ohta, "Vertical GaN-based trench gate metal oxide semiconductor field-effect transistors on GaN bulk substrates," Appl. Phys. Express 1, 011105 (2008).

- 13) C. Gupta, S. H. Chan, C. Lund, A. Agarwal, O. S. Koksaldi, J. Liu, Y. Enatsu, S. Keller, and U. K. Mishra, "Comparing electrical performance of GaN trench-gate MOSFETs with a-plane (1120) and m-plane (1100) sidewall channels," Appl. Phys. Express 9, 121001 (2016).

- 14) R. A. Khadar, C. Liu, L. Zhang, P. Xiang, K. Cheng, and E. Matioli, IEEE Electron Device Lett. 39, 401 (2018).

- 15) C. Liu, R. A. Khadar, and E. Matioli, IEEE Electron Device Lett. 39, 1034 (2018).

- T. J. Flack, B. N. Pushpakaran, and S. B. Bayne, "GaN technology for power electronic applications: a review," J. Electron. Mater. 45, 2673 (2016).

- 17) M. Ruzzarin, M. Meneghini, D. Bisi, M. Sun, T. Palacios, G. Meneghesso, and E. Zanoni, Appl. Phys. Lett. 64, 3126 (2017).

- M. Ruzzarin et al., IEEE Int. Reliability Physics Symp. Proc., 2019 (Monterey, CA, USA).

- 19) B. Ren, M. Sumiya, M. Liao, Y. Koide, X. Liu, Y. Shen, and L. Sang, J. Alloys Compd. 767, 600 (2018).

- 20) S. Kaneki, J. Ohira, S. Toiya, Z. Yatabe, J. T. Asubar, and T. Hashizume, Appl. Phys. Lett. 109, 162104 (2016).

- 21) D. Bisi, S. H. Chan, X. Liu, R. Yeluri, S. Keller, M. Meneghini, G. Meneghesso, E. Zanoni, and U. K. Mishra, Appl. Phys. Lett. 108, 112104 (2016).

- 22) P. Lagger et al., Appl. Phys. Lett. 105, 033512 (2014).

- 23) P. B. Klein, J. Appl. Phys. 92, 5498 (2002).

- 24) D. Bisi, A. Stocco, M. Meneghini, F. Rampazzo, A. Cester, G. Meneghesso, and E. Zanoni, IEEE Int. Reliability Physics Symp. Proc., 2014CD.11.1.

- 25) P. Lagger, M. Reiner, D. Pogany, and C. Ostermaier, IEEE Trans. Electron Devices 61, 1022 (2014).

- 26) E. Canato, F. Masin, M. Borga, E. Zanoni, M. Meneghini, and G. Meneghesso, IEEE Int. Reliability Physics Symp. Proc., 2019 (Monterey, CA, USA).

- 27) M. Sato, S. Kamiyama, T. Matsuki, D. Ishikawa, T. Ono, T. Morooka, J. Yugami, K. Ikeda, and Y. Ohji, Jpn. J. Appl. Phys. 49, 04DC24 (2010).

- 28) M. Choi, A. Janotti, and C. G. Van de Walle, J. Appl. Phys. 113, 044501 (2013).

- 29) J. Robertson and B. Falabretti, J. Appl. Phys. **100**, 014111 (2006).

- 30) B. L. Swenson and U. K. Mishra, J. Appl. Phys. 106, 064902 (2009).

- M. Meneghini et al., "Degradation mechanisms of GaN-based vertical devices a review," Phys. Status Solidi A (2020).