Università degli Studi di Padova

#### UNIVERSITY OF PADOVA DEPARTMENT OF INFORMATION ENGINEERING

Ph.D. School on Information Engineering – XXV Cycle Information and Communication Science and Technologies

# PERFORMANCE OPTIMIZATION OF GPU ELF-CODES

School Director Prof. MATTEO BERTOCCO

Section Coordinator Prof. CARLO FERRARI

Supervisor Prof. GIANFRANCO BILARDI

> **PhD Candidate** FAUSTO ARTICO

# Abstract

#### Abstract in English

GPUs (Graphic Processing Units) are of interest for their favorable ratio  $\frac{GF/s}{price}$ . Compared to the beginning - early 1980's - nowadays GPU architectures are more similar to general purpose architectures but with (much) larger numbers of cores - the GF100 architecture released by NVIDIA in 2009-2010, for example, has a true hardware cache hierarchy, a unified memory address space, double precision performance and has a maximum of 512 cores.

Exploiting the computational power of GPUs for non-graphics applications - past or present - has, however, always been hard. Initially, in the early 2000's, the way to program GPUs was by using graphic libraries API's (exclusively), which made writing non-graphics codes non-trivial and tedious at best, and virtually impossible in the worst case. In 2003, the Brook compiler and runtime system was introduced, giving users the ability to generate GPU code from a high level programming language. In 2006 NVIDIA introduced CUDA (Compute Unified Device Architecture). CUDA, a parallel computing platform and programming model specifically developed by NVIDIA for its GPUs, attempts to further facilitate general purpose programming of GPUs. Code edited using CUDA is portable between different NVIDIA GPU architectures and this is one of the reasons because NVIDIA claims that the user's productivity is much higher than previous solutions, however optimizing GPU code for utmost performance remains very hard, especially for NVIDIA GPUs using the GF100 architecture - e.g., Fermi GPUs and some Tesla GPUs - because a) the real instruction set architecture (ISA) is not publicly available, b) the code of the NVIDIA compiler - nvcc - is not open and c) users can not edit code using the real assembly - ELF in NVIDIA parlance.

Compilers, while enabling immense increases in programmer productivity, by eliminating the need to code at the (tedious) assembly level, are incapable of achieving, to date, performance similar to that of an expert assembly programmer with good knowledge of the underlying architecture. In fact, it is widely accepted that high-level language programming and compiling even with a state-of-the-art compilers loose, on average, a factor of 3 in performance - and sometimes much more - over what a good assembly programmer could achieve, and that even on a conventional, simple, single-core machine. Compilers for more complex machines, such as NVIDIA GPUs, are likely to do much worse because among other things, they face (even more) complex trade-offs between often undecidable and NP-hard problems. However, because NVIDIA a) makes it virtually impossible to gain access to the actual assembly language used by its GF100 architecture, b) does not publicly explain many of the internal mechanisms implemented in its compiler - nvcc - and c) makes it virtually impossible to learn the details of its very complex GF100 architecture in sufficient detail to be able to exploit them, obtaining an estimate of the performance difference between CUDA programming and machine-level programming for NVIDIA GPUs using the GF100 architecture - let alone achieving some *a priori* performance guarantees of shortest execution time - has been,

prior to this current work, impossible.

To optimize GPU code, users have to use CUDA or PTX (Parallel Thread Execution) - a virtual instruction set architecture. The CUDA or PTX files are given in input to nvcc that produces as output fatbin files. The fatbin files are produced considering the target GPU architecture selected by the user - this is done setting a flag used by nvcc. In a fatbin file, zero or more parts of the fatbin file will be executed by the CPU - think of these parts as the C/C++ parts - while the remaining parts of the fatbin file - think of these parts as the ELF parts - will be executed by the specific model of the GPU for which the CUDA or PTX file has been compiled. The fatbin files are usually very different from the corresponding CUDA or PTX files and this lack of control can completely ruin any effort made at CUDA or PTX level to optimize the ELF part/parts of the fatbin file that will be executed by the target GPU for which the fatbin file has been compiled.

We therefore reverse engineer the real ISA used by the GF100 architecture and generate a set of editing guidelines to force nvcc to generate fatbin files with at least the minimum number of resources later necessary to modify them to get the wanted ELF algorithmic implementations this gives control on the ELF code that is executed by any GPU using the GF100 architecture. During the process of reverse engineering we also discover all the correspondences between PTX instructions and ELF instructions - a single PTX instruction can be transformed in one or more ELF instructions - and the correspondences between PTX registers and ELF registers. Our procedure is completely repeatable for any NVIDIA Kepler GPU - we do not need to rewrite our code.

Being able to get the wanted ELF algorithmic implementations is not enough to optimize the ELF code of a fatbin file, we need in fact also to discover, understand, and quantify some not disclosed GPU behaviors that could slow down the execution of ELF code. This is necessary to understand how to execute the optimization process and while we can not report here all the results we have got, we can however say that we will explain to the reader a) how to force even distributions of the GPU thread blocks to the streaming multiprocessors, b) how we have discovered and quantified several warp scheduling phenomenons, c) how to avoid phenomenons of warp scheduling load unbalancing, that it is not possible to control, in the streaming multiprocessors, d) how we have determined, for each ELF instruction, the minimum quantity of time that it is necessary to wait before a warp scheduler can schedule again a warp - yes, the quantity of time can be different for different ELF instructions - e) how we have determined the time that it is necessary to wait before to be able to read again the data in a register previously read or written - this too can be different for different ELF instructions and different whether the data has been previously read or written - and f) how we have discovered the presence of an overhead time for the management of the warps that does not grow linearly to a liner increase of the number of residents warps in a streaming multiprocessor.

Next we explain a) the procedures of transformation that it is necessary to apply to the ELF code of a fatbin file to optimize the ELF code and so making its execution time as short as possible, b) why we need to classify the fatbin files generated from the original fatbin file during the process of optimization and how we do this using several criteria that as final result allow us to determine the positions, occupied by each one of the fatbin files generated, in a taxonomy that we have created, c) how using the position of a fatbin file in the taxonomy we determine whether the fatbin file is eligible for an empirical analysis - that we explain - a theoretical analysis or both, and d) how - if the fatbin file is eligible for a theoretical analysis - we execute the theoretical analysis that we have devised and give an *a priori* - without any previous execution of the fatbin file - shortest ELF code execution time guarantee - this if the fatbin file satisfies all the requirements of the theoretical

analysis - for the ELF code of the fatbin file that will be executed by the target GPU for which the fatbin file has been compiled.

#### Abstract in Italian

GPUs (Graphic Processing Units) sono di interesse per il loro favorevole rapporto  $\frac{GF/s}{price}$ . Rispetto all'inizio - primi anni 70 - oggigiorno le architectture GPU sono più simili ad architectture general purpose ma hanno un numero (molto) più grande di cores - la architecttura GF100 rilasciata da NVIDIA durante il 2009-2010, per esempio, ha una vera gerarchia di memoria cache, uno spazio unificato per l'indirizzamento in memoria, è in grado di eseguire calcoli in doppia precisione ed ha un massimo 512 core.

Sfruttare la potenza computazionale delle GPU per applicazioni non grafiche - passate o presenti - è, comunque, sempre stato difficile. Inizialmente, nei primi anni 2000, la programmazione su GPU avveniva (esclusivamente) attraverso l'uso librerie grafiche, le quali rendevano la scrittura di codici non grafici non triviale e tediosa al meglio, e virtualmente impossibile al peggio. Nel 2003, furono introdotti il compilatore e il sistema runtime Brook che diedero agli utenti l'abilità di generare codice GPU da un linguaggio di programmazione ad alto livello. Nel 2006 NVIDIA introdusse CUDA (Compute Unified Device Architecture). CUDA, un modello di programmazione e computazione parallela specificamente sviluppato da NVIDIA per le sue GPUs, tenta di facilitare ulteriormente la programmazione general purpose di GPU. Codice scritto in CUDA è portabile tra differenti architectture GPU della NVIDIA e questa è una delle ragioni perché NVIDIA afferma che la produttività degli utenti è molto più alta di precedenti soluzioni, tuttavia ottimizare codice GPU con l'obbiettivo di ottenere le massime prestazioni rimane molto difficile, specialmente per NVIDIA GPUs che usano l'architecttura GF100 - per esempio, Fermi GPUs e delle Tesla GPUs perché a) il vero instruction set architecture (ISA) è non pubblicamente disponibile, b) il codice del compilatore NVIDIA - nvcc - è non aperto e c) gli utenti non possono scrivere codice usando il vero assembly - ELF nel gergo della NVIDIA.

I compilatori, mentre permettono un immenso incremento della produttività di un programmatore, eliminando la necessità di codificare al (tedioso) livello assembly, sono incapaci di ottenere, a questa data, prestazioni simili a quelle di un programmatore che è esperto in assembly ed ha una buona conoscenza dell'architettura sottostante. Infatti, è largamente accettato che programmazione ad alto livello e compilazione perfino con compilatori che sono considerati allo stato dell'arte perdono, in media, un fattore 3 in prestazione - e a volte molto di più - nei confronti di cosa un buon programmatore assembly potrebbe ottenere, e questo perfino su una macchina convenzionale, semplice, a singolo core. Compilatori per macchine più complesse, come le GPU NVIDIA, sono propensi a fare molto peggio perché tra le altre cose, essi devono determinare (persino più) complessi trade-offs durante la ricerca di soluzioni a problemi spesso indecidibili e NP-hard. Peraltro, perché NVIDIA a) rende virtualmente impossibile guadagnare accesso all'attuale linguaggio assembly usato dalla architettura GF100, b) non spiega pubblicamente molti dei meccanismi interni implementati nel suo compilatore - nvcc - e c) rende virtualmente impossible imparare i dettagli della molto complessa architecttura GF100 ad un sufficiente livello di dettaglio che permetta di sfruttarli, ottenere una stima delle differenze prestazionali tra programmazione in CUDA e programmazione a livello macchina per GPU NVIDIA che usano la architecttura GF100 - per non parlare dell'ottenimento a priori di garanzie di tempo di esecuzione più breve - è stato, prima di questo corrente lavoro, impossbile.

Per ottimizare codice GPU, gli utenti devono usare CUDA or PTX (Parallel Thread Execution) - un instruction set architecture virtuale. I file CUDA or PTX sono dati in input a nvcc che produce come output fatbin file. I fatbin file sono prodotti considerando l'architecttura GPU selezionata dall'utente - questo è fatto settando un flag usato da nvcc. In un fatbin file, zero o più parti del fatbin file saranno eseguite dalla CPU - pensa a queste parti come le parti C/C++ - mentre le rimanenti parti del fatbin file - pensa a queste parti come le parti ELF - saranno eseguite dallo specifico modello GPU per il quale i file CUDA or PTX sono stati compilati. I fatbin file sono normalmente molto differenti dai corrispodenti file CUDA o PTX e questa assenza di controllo può completamente rovinare qualsiasi sforzo fatto a livello CUDA o PTX per otimizzare la parte o le parti ELF del fatbin file che sarà eseguita / saranno eseguite dalla GPU per la quale il fatbin file è stato compilato.

Noi quindi scopriamo quale è il vero ISA usato dalla architettura GF100 e generiamo un insieme di linea guida per scrivere codice in modo tale da forzare nvcc a generare fatbin file con almeno il minimo numero di risorse successivamente necessario per modificare i fatbin file per ottenere le volute implementazioni algoritmiche in ELF - questo da controllo sul codice ELF che è eseguito da qualsiasi GPU che usa l'architettura GF100. Durante il processo di scoperata del vero ISA scopriamo anche le corrispondenze tra istruzioni PTX e istruzioni ELF - una singola istructione PTX può essere transformata in one o più istruzioni ELF - e le corrispondenze tra registri PTX e registri ELF. La nostra procedura è completamente ripetibile per ogni NVIDIA Kepler GPU - non occorre che riscrivamo il nostro codice.

Essere in grado di ottenere le volute implementazioni algoritmiche in ELF non è abbastanza per ottimizzare il codice ELF di un fatbin file, ci occorre infatti anche scoprire, comprendere e quantificare dei comportamenti GPU che non sono divulgati e che potrebbero rallentare l'esecuzione di codice ELF. Questo è necessario per comprendere come eseguire il processo di ottimizzazione e mentre noi non possiamo riportare qui tutti i risultati che abbiamo ottenuto, noi possiamo comunque dire che spiegheremo al lettore a) come forzare una distribuzione uniforme dei GPU thread blocks agli streaming multiprocessors, b) come abbiamo scoperto e quantificato diversi fenomeni riguardanti il warp scheduling, c) come evitare fenomeni di warp scheduling load unblanacing, che è non possible controllare, negli streaming multiprocessors, d) come abbiamo determinato, per ogni istruzione ELF, la minima quantità di tempo che è necessario attendere prima che un warp scheduler possa schedulare ancora un warp - si, la quantità di tempo può essere differente per differenti istruzioni ELF - e) come abbiamo determinato il tempo che è necessario attendere prima di essere in grado di leggere ancora un dato in un registro precedentemente letto o scritto - questo pure può essere differente per differnti istruzioni ELF e differente se il dato è stato precedentemente letto o scritto - e f) come abbiamo scoperto la presenza di un tempo di overhead per la gestione dei warp che non cresce linearmente ad un incremento lineare del numero di warp residenti in uno streaming multiprocessor.

Successivamente, noi spiegamo a) le procedure di trasformazione che è necessario applicare al codice ELF di un fatbin file per ottimizzare il codice ELF e così rendere il suo tempo di esecuzione il più corto possibile, b) perché occorre classificare i fatbin file generati dal fatbin file originale durante il processo di ottimizzazione e come noi facciamo questo usando diversi criteri che come risultato finale permettono a noi di determinare le posizioni, occupate da ogni fatbin file generato, in una tassonomia che noi abbiamo creato, c) come usando la posizione di un fatbin file nella tassonomia noi determiniamo se il fatbin file è qualificato per una analisi empirica - che noi spieghiamo - una analisi teorica o entrambe and d) come - supponendo il fatbin file sia qualificato per una

analisi teorica - noi eseguiamo l'analisi teorica che abbiamo ideato e diamo *a priori* - senza alcuna precedente esecuzione del fatbin file - la garanzia - questo supponendo il fatbin file soddisfi tutti i requisiti dell'analisi teorica - che l'esecuzione del codice ELF del fatbin file, quando il fatbin file sarà eseguito sulla architettura GPU per cui è stato generato, sarà la più breve possibile.

# Contents

| 1:                                                |     | Structure of the Thesis                                                           | 13        |

|---------------------------------------------------|-----|-----------------------------------------------------------------------------------|-----------|

| 2:                                                |     | Introduction to GPUs                                                              | 17        |

|                                                   | 2.1 | Introduction                                                                      | 17        |

|                                                   | 2.2 | Parallel Thread Execution                                                         | 17        |

|                                                   | 2.3 | NVIDIA CUDA Compiler                                                              | 18        |

|                                                   | 2.4 | GPU Threads - Executions                                                          | 19        |

|                                                   |     | Launch Configuration - Definition                                                 | 20        |

| 2.6 Instruction Configuration                     |     |                                                                                   | 20        |

|                                                   |     | 2.6.1 Definition                                                                  | 21        |

|                                                   |     | 2.6.2 Dependence Distance                                                         | 21        |

|                                                   |     | 2.6.3 Execution Time                                                              | 21        |

|                                                   |     | 2.6.4 Useless Dependence Types                                                    | 21        |

|                                                   |     | 2.6.5 Examples                                                                    | 21        |

|                                                   | 2.7 | Summary                                                                           | 23        |

| 3:                                                |     | The GF100 Architecture                                                            | <b>25</b> |

|                                                   | 3.1 | Introduction                                                                      | 25        |

|                                                   | 3.2 | Main Components of the GF100 Architecture                                         | 25        |

| 3.3 Main Components of a Streaming Multiprocessor |     | Main Components of a Streaming Multiprocessor                                     | 27        |

|                                                   | 3.4 | Theoretical Tesla C2070 Peak Performances per Second                              | 29        |

|                                                   | 3.5 | Summary of the Tesla C2070 Architectural Features                                 | 30        |

| 4:                                                |     | Types of Performance                                                              | 31        |

|                                                   | 4.1 | Introduction                                                                      | 31        |

|                                                   | 4.2 | Theoretical Streaming Multiprocessor Peak Performance Achievable in a Clock Cycle | 31        |

|                                                   | 4.3 | Theoretical Streaming Multiprocessor Best Average Performance per Clock Cycle     | 32        |

|                                                   | 4.4 | Theoretical Instruction Configuration Streaming Multiprocessor Peak Performance   |           |

|                                                   |     | Achievable in a Clock Cycle                                                       | 32        |

|                                                   | 4.5 | Real Instruction Configuration Streaming Multiprocessor Peak Performance Achiev-  |           |

|                                                   |     | able in a Clock Cycle                                                             | 33        |

|                                                   | 4.6 | Real ELF Code Streaming Multiprocessor Average Performance per Clock Cycle        | 33        |

|                                                   | 4.7 | Theoretical ELF Code Streaming Multiprocessor Best Average Performance per        |           |

|                                                   |     | Clock Cycle                                                                       | 34        |

|                                                   | 4.8 | Real ELF Code Streaming Multiprocessor Best Average Performance per Clock Cycle   | 35        |

|                                                   | 4.9 | Summary                                                                           | 35        |

| 5: | Lower Bound on the Real ELF Code Efficiency |                                                                                   |           |

|----|---------------------------------------------|-----------------------------------------------------------------------------------|-----------|

|    | 5.1                                         | Introduction                                                                      | 37        |

|    | 5.2                                         | Calculations to Determine the Lower Bound                                         | 37        |

|    | 5.3                                         | Warp Scheduling on the Not Disclosed Shared Hardware Resources                    | 39        |

|    | 5.4                                         | Warp Scheduling Influence on the ELF Code Execution Time                          | 39        |

|    | 5.5                                         | Elimination of the Warp Scheduler Variability                                     | 40        |

|    | 5.6                                         | Warp Management Mechanism                                                         | 40        |

|    | 5.7                                         | How much Tight Is the Lower Bound?                                                | 44        |

|    | 5.8                                         | Generality of the Solution Found for the Lower Bound                              | 45        |

|    | 5.9                                         | Summary                                                                           | 45        |

| 6: |                                             | Reverse Engineering of the ISA and Modification of ELF Codes                      | <b>47</b> |

|    | 6.1                                         | Introduction                                                                      | 47        |

|    | 6.2                                         | Localization in Fatbin Files of the ELF Instructions Necessary to Execute the PTX |           |

|    |                                             | Instructions of PTX Codes                                                         | 48        |

|    | 6.3                                         | PTX - ELF Correspondence Transformations                                          | 50        |

|    |                                             | 6.3.1 Editing Guidelines To Edit PTX Files                                        | 50        |

|    |                                             | 6.3.2 Analysis and Comparison of the PTX and Fatbin File Structures               | 52        |

|    |                                             | 6.3.3 Number, Type and Matching among PTX and ELF Registers                       | 53        |

|    | 6.4                                         | Database of the Human Readable Text Form Representations                          | 54        |

|    | 6.5                                         | Database of the Binary Codes of the ELF Instructions                              | 56        |

|    | 6.6                                         | Fatbin File Generation Satisfying Resource Constraints                            | 58        |

|    | 6.7                                         | Wanted ELF Algorithmic Implementations                                            | 60        |

|    | 6.8                                         | Summary                                                                           | 61        |

| 7: |                                             | Discovery, Understanding and Quantification of Not Disclosed GPU                  |           |

|    |                                             | Behaviors                                                                         | 65        |

|    | 7.1                                         | Introduction                                                                      | 65        |

|    | 7.2                                         | Not Disclosed GPU Behavior Categories                                             | 66        |

|    | 7.3                                         | GPU Architectural Features                                                        |           |

|    |                                             | 7.3.1 Global GPU Assignment and Scheduling Architectural Features                 | 67        |

|    |                                             | 7.3.2 Local Streaming Multiprocessor PTX and ELF Architectural Features           | 67        |

|    | 7.4                                         | PTX and ELF Codes                                                                 | 71        |

|    |                                             | 7.4.1 <i>A Priori</i> Bandwidth and Latency GPU Memories Free Guarantee           | 71        |

|    |                                             | 7.4.2 Structure of the PTX and ELF Codes                                          | 72        |

|    |                                             | 7.4.3 Construction of the PTX and ELF Codes                                       | 74        |

|    | 7.5                                         | Launch Configurations                                                             | 74        |

|    |                                             | 7.5.1 Global GPU Assignment and Scheduling Architectural Features                 | 75        |

|    |                                             | 7.5.2 Local Streaming Multiprocessor PTX and ELF Architectural Features           | 75        |

|    | 7.6                                         | GPU Architectural Feature Quantifications                                         | 76        |

|    |                                             | 7.6.1 Global GPU Assignment and Scheduling Architectural Features                 | 76        |

|    |                                             | 7.6.2 Local Streaming Multiprocessor PTX and ELF Architectural Features           | 79        |

|    | 7.7                                         | Summary                                                                           | 90        |

| 8: |                                             | Modifications, Launch Configurations and Transformations                          | 93        |

|    | 8.1                                         | Introduction                                                                      | 93        |

|    | Procedures to Modify Single Fatbin Files | )3                                                                                      |          |

|----|------------------------------------------|-----------------------------------------------------------------------------------------|----------|

|    |                                          | 8.2.1 Logically Correct Permutations of the ELF Instructions                            | )3       |

|    |                                          | 8.2.2 Even Distribution of the GPU Thread Blocks to the Streaming Multiprocessors 9     | 4        |

|    |                                          | 8.2.3 Modification of the Reading and/or Writing Mechanisms                             | 4        |

|    | 8.3                                      | Selection of the Launch Configurations                                                  | 0        |

|    | 8.4                                      | Transformation of the Fatbin File to Analyze                                            | )6       |

|    | 8.5                                      | Summary                                                                                 | 9        |

| 9: |                                          | Warp Scheduling Policies 11                                                             | .3       |

|    | 9.1                                      | Introduction                                                                            | 3        |

|    | 9.2                                      | What is Reasonable to Assume being True                                                 | 4        |

|    |                                          | 9.2.1 Very Simple Fatbin Files                                                          | 4        |

|    |                                          | 9.2.2 Executions with Load Balancing                                                    | 4        |

|    |                                          | 9.2.3 Probably True Things about the Warp Scheduling                                    | 4        |

|    |                                          | 9.2.4 Because Other Possibilities are Unlikely                                          | 5        |

|    | 9.3                                      | Impossibility of Knowing the Truth                                                      | 6        |

|    | 9.4                                      | Cycling Policy - The Probable Warp Scheduling Policy                                    | 6        |

|    |                                          | 9.4.1 Mechanisms and Dynamics of the Warp Scheduling Cycling Policy                     | 7        |

|    |                                          | 9.4.2 Change of the Order of Execution of the Mechanisms                                | 8        |

|    |                                          | 9.4.3 Possibility of a Time Difference Between Warp Schedulers                          | 8        |

|    |                                          | 9.4.4 Supporting Reasons for the Warp Scheduling Cycling Policy                         | 9        |

|    |                                          | 9.4.5 Justifying the Starting Time Differences                                          | 0        |

|    | 9.5                                      | The Possibility that Other Policies are Executed                                        | 2        |

|    |                                          | 9.5.1 Generalization of Results about the Starting Time Differences                     | 2        |

|    |                                          | 9.5.2 Difficulty to Generalize the Results about the Ending Time Differences $\dots$ 12 | 3        |

|    |                                          | 9.5.3 Consequences of the Reader's Choice                                               | 3        |

|    |                                          | 9.5.4 Impossibility to Determine and Understand any Other Policy                        | 4        |

|    |                                          | 9.5.5 Why a Policy Different from the Cycling Policy is Unlikely                        | 4        |

|    | 9.6                                      | Advantages and Disadvantages of the Cycling Policy                                      | 6        |

|    | 9.7                                      | Summary                                                                                 | 7        |

| 10 | :                                        | Taxonomy for Fatbin Files 12                                                            | 29       |

|    | 10.1                                     | Introduction                                                                            | 9        |

|    | 10.2                                     | Warp Scheduling Policy                                                                  | 0        |

|    | 10.3                                     | Branches                                                                                | 0        |

|    | 10.4                                     | Eviction Policies Used for the L2 Cache and the L1 Caches                               | 2        |

|    | 10.5                                     | Reading and Writing - Which and Where                                                   | 3        |

|    | 10.6                                     | ELF Instructions of Synchronization                                                     | <b>4</b> |

|    | 10.7                                     | Fatbin Files Generated for the Optimizations                                            | 5        |

|    | 10.8                                     | Summary                                                                                 | 5        |

| 11 | :                                        | Analysis/Analyses Selection 13                                                          | ;9       |

|    | 11.1                                     | Introduction                                                                            | 9        |

|    | 11.2                                     | Analysis/Analyses Selection                                                             | 9        |

|    | 11.3                                     | Summary                                                                                 | .3       |

| 12:  | Guaranteeing A Priori ELF Code Shortest Execution Times                              |     |

|------|--------------------------------------------------------------------------------------|-----|

| 12.1 | Introduction                                                                         | 145 |

| 12.2 | Bandwidths and Latencies of the GPU Memories                                         | 145 |

|      | 12.2.1 Reading and Writing - Positions and Locations                                 | 146 |

|      | 12.2.2 Difficulties in the Determination of the Cache Lines to Transfer              | 146 |

|      | 12.2.3 Supposing the GF100 Architecture Without the L2 Cache                         | 147 |

|      | 12.2.4 Maximum Distance in Number of Warp ELF Instructions                           | 148 |

|      | 12.2.5 Introduction of ELF Instructions of Synchronization                           | 149 |

|      | 12.2.6 Constancy, of the Distances, in Number of Warp ELF Instructions               | 151 |

|      | 12.2.7 Warp ELF Instructions Implying Off-Chip $\leftrightarrow$ On-Chip Transfers   | 155 |

|      | 12.2.8 Slowdowns due to the Bandwidths and the Latencies                             | 161 |

| 12.3 | Number of Resident Warps in Each Streaming Multiprocessor                            | 169 |

| 12.4 | Summary                                                                              | 171 |

| 13:  | Contributions of the Thesis                                                          | 175 |

| 13.1 | Introduction                                                                         | 175 |

| 13.2 | Real ISA and ELF Codes                                                               | 176 |

|      | 13.2.1 Localization in Fatbin Files of the ELF Instructions Necessary to Execute the |     |

|      | PTX Instructions of PTX Codes                                                        | 177 |

|      | 13.2.2 Editing Rules to Force Nvcc                                                   | 177 |

|      | 13.2.3 PTX-ELF Correspondences                                                       | 179 |

|      | 13.2.4 Reverse Engineering of the Real Instruction Set Architecture                  | 181 |

|      | 13.2.5 Getting the Wanted ELF Algorithmic Implementations                            | 181 |

| 13.3 | Not Disclosed GPU Behaviors                                                          | 182 |

|      | 13.3.1 Advancement of the Resident Warps in a Streaming Multiprocessor               | 183 |

|      | 13.3.2 Even Distribution of the GPU Thread Blocks                                    | 183 |

|      | 13.3.3 Warp Scheduling Load Unbalancing                                              | 184 |

|      | 13.3.4 Local Streaming Multiprocessor PTX and ELF Architectural Features             | 184 |

| 13.4 | Transformations and Launch Configurations                                            | 186 |

|      | 13.4.1 Transformation of the Original Fatbin File to Be Optimized                    | 187 |

|      | 13.4.2 Selection of the Launch Configurations                                        | 187 |

| 13.5 | Analysis of the Equivalent Fatbin Files Generated                                    | 187 |

|      | 13.5.1 Taxonomy for Fatbin Files                                                     | 188 |

|      | 13.5.2 Analysis/Analyses Selection                                                   | 188 |

|      | 13.5.3 Guaranteeing A Priori ELF Code Shortest Execution Times                       | 188 |

| 13.6 | Summary                                                                              | 189 |

| 14:  | Previous Work and its Problems                                                       | 191 |

| 14.1 | Introduction                                                                         | 191 |

| 14.2 | Previous Work                                                                        | 191 |

|      | Problems with the Previous Work                                                      |     |

| 14.4 | Summary                                                                              | 196 |

| 15:  | Conclusions and Future Research Directions                                           | 197 |

|      | Introduction                                                                         |     |

| 15.2 | Conclusions                                                                          | 197 |

| 5.3 Future Research Directions |  | 8 |

|--------------------------------|--|---|

|--------------------------------|--|---|

## Chapter 1

# Structure of the Thesis

To get a very synthetic summary of the main contributions of this thesis the reader can read 15, for a more detailed description of the main contributions the reader can read 13, while to get an idea of the problems a) that afflict the papers in literature and b) that we have instead addressed and solved, the read can read 14. After this, to get a further level of detail, this time about all the contributions of the thesis, the reader can read the summary section of each chapter - to facilitate his/her research job in the thesis we describe in this chapter the structure of the thesis. Finally, for the greatest level of detail and to understand the procedures used to get each one of the results, the reader can read in detail each single chapter. The structure of the thesis is the following:

- In chapter 2 we introduce the reader to the GPU world. In 2.1 we describe the structure of 2 while in 2.2 we talk of PTX, the parallel thread execution virtual machine and instruction set architecture of the GF100 architecture the GPU architecture used. In 2.3 we describe what is disclosed of the GPU compiler, nvcc, and its behaviors when it takes in input CUDA or PTX codes and produces as output fatbin files containing the ELF codes that the GF100 architecture has to execute. In section 2.4 we explain what happens each time a fatbin file is launched and the role of each GPU thread used to execute the fatbin file while in section 2.5 we define what is a launch configuration. In section 2.6 we instead define what are the instruction configurations, explain because they are important, explain how we will time their executions, explain the type of dependences we can consider in each instruction configuration, explain which types of dependences are important and which not and give some examples of instruction configurations;

- In chapter 3 we describe the GF100 architecture. In 3.1 we describe the structure of 3 while in 3.2 we describe the main components of the GF100 architecture. In 3.3 we analyze what is disclosed about the many parts composing some of the main components - the streaming multiprocessors - of the GF100 architecture. In section 3.4 we calculate the theoretical peak performances per second of the Tesla C2070 - the GPU that we use. In section 5 we summarize, from the quantitative point of view, the disclosed architectural features of the Tesla C2070;

- In chapter 4 we introduce several type of performances. In 4.1 we describe the structure of 4 while in each one of the remaining sections of the chapter we consider a different type of performance, give its definition, explain because it is important or not and put in evidence which of them we consider when we want to optimize the ELF code in a fatbin file;

- In chapter 5 we explain that when we calculate the efficiency of an ELF code in a fatbin file in reality we are calculating a lower bound on the real ELF code efficiency. In 5.1 we describe the structure of 5 while in 5.2 we explain more in detail why we need to calculate a lower bound on the real ELF code efficiency and underline the challenge about the quantification of the tightness of this lower bound. In 5.3 we describe the problem of the warp scheduling on the not disclosed shared hardware resources and in 5.4 we stress its influence on the ELF execution time. In 5.5 we explain that also if we eliminate the problem given by the variability, due to the warp scheduling, of the ELF code execution time, it is not yet possible to quantify the tightness of the lower bound on the real ELF code efficiency. In 5.6 we describe the warp scheduling mechanism. In 5.7 we explain that, also whether it is evident that it is not possible to quantify how much tight is the lower bound, the lower bound is always the more tight that it is possible. In 5.8 we explain that the results we get in 5.7 are valid in all the possible cases;

- In chapter 6 we reverse engineer the real instruction set architecture and so not the PTX but the ELF - to be able to get the wanted ELF algorithmic implementations when we write code -PTX is the lowest way to write code so we need to write code in PTX, give it in input to nvcc, get as output a fatbin file and modify in the fatbin file the ELF code corresponding to the PTX code. In 6.1 we describe the structure of 6 while in 6.2 we explain the procedure necessary to localize in a fatbin file the ELF instructions corresponding to the PTX instructions of a PTX file given in input to nvcc for the generation of the fatbin file. In 6.3 we explain that to be able to modify ELF code is necessary to understand the correspondences between single PTX instructions and ELF instructions used in the fatbin files to execute the single PTX instructions and we explain how we accomplish this - using specific editing rules to edit the PTX files, checking the structures of the PTX files and their corresponding ELF codes in the fatbin files, understanding the number, type and matches between the PTX registers used in each single PTX instruction and their counterparts in the ELF code. In 6.4 we therefore build a database storing all the correspondences a) between single PTX instructions and ELF instructions necessary to execute each single PTX instruction and b) between PTX registers used in the single PTX instructions and the ELF registers used in the ELF instructions necessary to execute each single PTX instruction. In 6.5 we reverse engineer the binary codes of each single ELF instruction of interest. In 6.6 we explain how we produce fatbin files satisfying the resource constraints we need - this to be able later to modify ELF codes in fatbin files. In 6.7 we describe all the steps of the procedure necessary to generate the wanted ELF algorithmic implementations;

- In chapter 7 we discover, understand and quantify some not disclosed GPU behaviors In 7.1 we describe the structure of 7 while in 7.2 we subdivide the not disclosed GPU behavior we want to discover, understand and quantify in two categories global and local. In 7.3 we describe the global GPU assignment and scheduling architectural features necessary to discover, understand and quantify the global GPU behaviors and the local streaming multiprocessor PTX and ELF architectural features necessary to discover, understand and quantify the importance of having a priori guarantees that the PTX and the ELF codes, that we use to quantify the GPU architectural features, can not be slowed down in their executions by the bandwidths and the latencies of the GPU memories and we explain a) how we get these a priori guarantees giving to the PTX and to the ELF codes specific structures and b) how we construct such PTX and ELF codes. In 7.5 we specify the

launch configurations that we use for the quantification of the GPU architectural features distinguishing between launch configurations used for the quantification of the global GPU assignment and scheduling architectural features and the local streaming multiprocessor PTX and ELF architectural features. In 7.6 we quantify the global GPU assignment and scheduling architectural features and the local streaming multiprocessor PTX and ELF architectural features and the local streaming multiprocessor PTX and ELF architectural features and the local streaming multiprocessor PTX and ELF architectural features;

- In chapter 8 we explain how to transform a fatbin file to increase the probability to get a greater lower bound on its real ELF code efficiency. In 8.1 we describe the structure of 8 while in 8.2 a description of the procedures we use to modify a fatbin file. In 8.3 we describe the procedure to generate the set of launch configurations that is used when we analyze a fatbin file. In 8.4 we explain the procedure that takes in input the fatbin file that is necessary to optimize and that produces as output a) a set of fatbin files that is used to analyze the original fatbin file in input and b) a set of launch configurations for each one of the fatbin files generated;

- In chapter 9 we talk about the possible warp scheduling policy that could be executed by the warp schedulers in the streaming multiprocessors of the GF100 architecture. In 9.1 we describe the structure of 9 while in 9.2 with explain what is reasonable to assume being true about the warp scheduling policy this considering the results of 7. In 9.3 we talk however of the impossibility of knowing whether what said in 9.2 is the truth in the real world. In 9.4 we therefore introduce the warp scheduling policy that we believe is the warp scheduling policy that the warp schedulers in the streaming multiprocessors of the GF100 architecture execute, this at least in the case when the bandwidths and the latencies of the GPU memories can not slow down the execution of a fatbin file. In 9.5 we talk instead about the possibility that other warp scheduling policies are executed by the warp schedulers in the streaming multiprocessors of the GF100 architecture execute warp schedulers in the streaming multiprocessors of the GF100 architecture execute warp schedulers in the streaming multiprocessors of the GF100 architecture execute warp schedulers in the streaming multiprocessors of the GF100 architecture execute warp schedulers in the streaming multiprocessors of the GF100 architecture execute warp scheduling policies different from the warp scheduling cycling policy. In 9.6 we conclude the chapter describing the advantages of the warp scheduling policy and its only disadvantage;

- In chapter 10 we introduce a taxonomy for fatbin files. In 10.1 we describe the structure of 10 while in 10.2 a summary of the consequences of what said in the previous chapter about the first of the five factors necessary to classify a fatbin file, the warp scheduling policy executed by the warp schedulers in the streaming multiprocessors. In 10.3 we talk of the second of the five factors, the presence or not of branches in the ELF code of the fatbin file and of its consequences. In 10.4 we talk of the third of the five factors, the eviction policies used for the l2 and l1 caches of the GF100 architecture. In 10.5 we talk of the fourth of the five factors, the reads and writes of the GPU threads used to execute the fatbin file. In 9.4.5 we talk of the last of the five factors, the presence of ELF instructions of synchronization in the fatbin file. Finally, in 10.7, we talk of the consequences of the possible combinations, generated by these 5 factors, on the fatbin files generated, using the procedures described in 8, for the optimizations;

- In chapter 11 we list the possible combinations given by a) the position, of the fatbin files, generated using the procedures described in 8, in the taxonomy for fatbin files introduced in the 10, and b) the reader's goals, and we explain the process necessary to select the analysis

or the analyses that can be executed on the fatbin files and we describe one of the two possible analyses - the empirical one;

- In chapter 12 we explain how we guarantee a priori ELF code shortest execution times using the other of the two possible analyses the theoretical one. In 12.1 we describe the structure of 12 while in 12.2 we describe the theoretical proof that it is necessary to prove that the execution of the ELF code of a fatbin file can not be slowed down by the bandwidths and the latencies of the GPU memories. In 12.3, supposing the execution of an ELF code of a fatbin file can not be slowed down by the bandwidths and the latencies of the GPU memories, we instead describe how to determine the minimum number of resident warps that it is necessary in each streaming multiprocessor to avoid pipeline stalls.

- In chapter 13 we summarize our contributes. At the introduction in 13.1 follows the four sections of the chapter. In section 13.2 we summarize our contributions about the reverse engineering of the real ISA and the modification of ELF code. In 13.3 we summarize our contributions about the discovery, understanding and quantification of not disclosed GPU behaviors. In 13.4 we summarize our contributions about the transformation of the ELF code of the original fatbin file to optimize and the selection of the launch configurations to use during the analysis/analyses. In 13.5 we summarize our contributions about the procedures of analysis developed to analyze the fatbin files generated for the optimization of the original fatbin file.

- In chapter 14 we describe in 14.2 the previous work and highlight in 14.3 the problems a) that afflict all the results of all the papers that we were able to find but b) do not afflict our work and the results got in this thesis.

- In chapter 15 we write the conclusions and explain the future research directions that could be followed to continue to develop the four main topics of this thesis and so a) the reverse engineering of the real ISA and the modification of ELF code to be able to have complete control on the ELF codes executed by GPUs, b) the discovery, understanding and quantification of not disclosed GPU behaviors to get data to use to understand how to optimize ELF code, c) the processes of transformation that can be applied to a fatbin file for its optimization and d) the analysis of ELF codes 1) with the development of methods of classification for ELF codes to understand the analysis/analyses that it is possible to execute on ELF codes, 2) with the development of empirical analyses and 3) with the development of theoretical analyses able to give a priori guarantees on the execution times of ELF codes.

## Chapter 2

# Introduction to GPUs

#### 2.1 Introduction

In this chapter we introduce the reader to GPUs. The discussions are valid for all the GPUs using the GF100 or later architecture - see 3 for a description of the GF100 architecture and its main hardware components.

We start talking of PTX, one of the possible "tools" to edit GPU code. We use PTX because it "facilitates" the reverse engineering of the real instruction set architecture - 6.5. Understanding the real instruction set architecture is necessary to be able to modify - if necessary - the parts of the codes the GPU is going to execute. Next we talk of the NVIDIA compiler - nvcc. We describe what nvcc takes in input, compiles and what produces as output - fatbin files. We explain the many parts composing a fatbin file and later - 6.2 - we explain how we localize the several parts in each fatbin file, this to be able - if necessary - to modify the parts, containing the ELF code - 2.3 - that correspond to the PTX code that we edit.

Follow a discussion on what the GPU threads execute when we launch a fatbin file - a subset of instructions of the real instruction set architecture. The subset is in ELF and is one of the parts of the fatbin file executed by the GPU - 6.2.

We therefore explain how we need logically configure the GPU threads, that we want to execute a fatbin file, before each execution of the fatbin file. This is important because different launch configurations imply different parameters to use in the analysis process of each fatbin file and so it could be that when some launch configurations are used to execute a fatbin file, the couple (fatbin file, launch configuration) has a greater probability to satisfy all the requirements of the analysis process if some launch configurations are used instead of others.

Finally we define what is an instruction configuration and describe the instruction configuration features that we use in 7 to discover, understand and quantify the GPU behaviours - the GPU behaviors are used for the analysis or the analyses and the modification of the ELF codes in the fatbin files.

#### 2.2 Parallel Thread Execution

GPU codes can be written in several ways, one of the possible ways is using PTX. As reported in the NVIDIA PTX manual - [52] - PTX is however much more than only one of the possible

ways to edit GPU code because PTX at its core is a parallel thread execution virtual machine and instruction set architecture (isa).

As reported in [52] the main aims of PTX are the following: 1) provide a stable is that spans multiple GPU generations, 2) achieve performance in compiled applications comparable to native GPU performance, 3) provide a machine-independent is a for C/C++ and other compilers to target, 4) provide a code distribution is a for application and middleware developers, 5) provide a common source-level is a for optimizing code generators and translators, which map PTX to specific target machines, 6) facilitate hand-coding of libraries, performance kernels, and architecture tests, 7) provide a scalable programming model that spans GPU sizes from a single unit to many parallel units.

PTX is the lowest of the "high" level "programming languages" that we can use to edit GPU code. We use PTX to reverse engineer the real instruction set architecture of the Tesla C2070 - the GPU we use in this thesis - because using PTX to edit GPU code we can skip several phases of the compiling chain used by nvcc. Skipping several phases we get a compiled code gone under a minor number of transformation phases of all the other possible cases where any of the other available programming languages is used to edit GPU code.

We can not have the guarantee that the compiled codes achieved given in input PTX code to nvcc are more near to mirror the original PTX codes of all the other possible cases where the GPU code is written using any of the other available programming languages but PTX "facilitates" the job of understanding a) as each single PTX instruction is transformed by nvcc and b) which and how many ELF instructions in the fatbin file produced as output by nvcc are used to execute each single PTX instruction.

We always need to give in input to the NVIDIA CUDA compiler - nvcc - each one of the PTX codes we edit. In the next section we therefore describe the nvcc job when it get in input PTX code and later the nvcc job when it get in input GPU codes written not using PTX.

#### 2.3 NVIDIA CUDA Compiler

We now know that one of the possible ways to edit GPU code is using PTX. PTX code can not however to be executed, in its original form, by the GPU. Before the GPU is able to execute PTX code or any other code that can be written using any NVIDIA tool or programming language it is necessary to compile the code using nvcc, the NVIDIA CUDA compiler.

The nvcc source code is not open so the things we know of nvcc are written in the NVIDIA nvcc manual. Nvcc can take in input two types of different files. Both the types of files contain code we want to be executed by the GPU but the code we want to be executed by the GPU has to be completely written using a) only PTX or b) using only one or more of the others programming languages allowed by NVIDIA. The two different type of files nvcc can take in input are the following:

• The .PTX or parallel thread execution files. The PTX files contain only GPU code and the GPU code in them can be only PTX code. When the nvcc compiler takes in input a PTX file it produces as output a fatbin - fat binary - file. The fatbin file contain the PTX code transformed in GPU assembly - let us call the GPU assembly ELF, this considering that when we use cuobjdump, 6.2, it returns as output an interpretation text file of what it defines being a fatbin ELF code.

Our analysis of the ELF code - 6 - shows that is possible that one or more ELF instructions

corresponds to a single PTX instruction but that there are also ELF instructions that do not correspond to any PTX instruction. More, the dimension of an fatbin file is bigger of the dimension of each ELF instruction - 8 bytes - times the number of ELF instructions used to execute the PTX code - 6.2.

• The .cu or CUDA files. The CUDA files contain CPU and GPU code. The GPU code in the CUDA files can not be PTX and is written using one of the several programming languages made available by NVIDIA.

When a CUDA file is given in input to nvcc, nvcc splits the CUDA file in one or more CPU parts and in one or more GPU parts. The GPU parts are first transformed by nvcc in PTX codes and next the PTX codes are transformed by nvcc in ELF codes - this is done considering the particular target GPU architecture where the PTX codes have to be executed. The ELF codes so obtained are one of the parts of the fatbin files generated by nvcc during the compiling phase - 6.2. After the CPU parts have been compiled using the C/C++ compiler of the CPU host machine nvcc, merges together the C/C++ compiled parts destined to be executed by the CPU and the GPU parts destined to be executed by the GPU. The final result is a fatbin file.

The merge between the CPU parts and the GPU parts is necessary a) because when a fatbin file is executed its execution starts on the CPU side and b) because some CPU-GPU synchronizations could be necessary.

Each time a fatbin file is launched, its GPU parts are executed by GPU threads - 2.4. In the case the fatbin file is produced starting by a PTX file then the fatbin file has to be called by inside a CUDA file - the CUDA file has to be processed too to produce another fatbin file as output because the processing has always to start on the CPU side but a fatbin file produced starting by a PTX file do not have any C/C++ code.

Now we know that only some parts of each fatbin file are executed by the GPU, the GPU parts, while the other parts of a fatbin file are executed by the CPU. The GPU parts are executed by GPU threads. In the next section what each GPU thread executes of the GPU parts.

#### 2.4 GPU Threads - Executions

We edit code we want executed by the GPU using PTX or one of the other available programming languages. Next we given the code in input to nvcc and we get as output a fatbin file that we later launch. When we launch a fatbin file the fatbin file starts to be executed by the CPU and later one or more of its parts are executed by the GPU.

In the parts executed by the GPU there are some subparts - 6.2 - completely composed of ELF code instructions  $s_p$ . The subparts  $s_p$  - created by nvcc during the compiling process - correspond to the code that a) we wanted executed by the GPU and b) we wrote using PTX or one of the other available programming languages. Each time we launch a fatbin file the subparts  $s_p$  are always executed by all the GPU threads we decide - at the moment of the fatbin launch - we want to execute the fatbin file. This does not mean that different threads executes different parts of the subparts  $s_p$ . Each GPU thread executes all the subparts  $s_p$  of a fatbin file or in other words each one of the subparts  $s_p$  of a fatbin file is always executed by each GPU thread.

Different fatbin files can be executed in parallel on the GPU but usually to execute a program only a fatbin file is running on the GPU at a given moment in time - this for GPU hardware synchronization problems that we face if we launch more different fatbin files in parallel.

All the GPU threads launched execute the same ELF code but the GPU threads can follow different paths - if possible - inside the same ELF code. If this happens for the GPU threads of a same warp - 3.2 - then we are in presence of a divergence phenomenon. Each divergence phenomenon implies a slow down, 10.3.

The GPU threads have however, in any case, to be logically organized before of each launch. In the next section we see what this logical organization is and the hardware limits that it has to satisfy to give a correct fatbin file execution.

#### 2.5 Launch Configuration - Definition

Each time we launch a fatbin file we need to decide a) the number of GPU thread blocks, b) a two dimensional space distribution of the GPU thread blocks - logic GPU thread block distribution - c) the number of GPU threads that is the number of GPU threads of each GPU thread block - GPU thread block composition - and d) a three dimensional space distribution of the GPU threads of each GPU thread block - logic GPU thread block form - that has be the same for all the GPU thread blocks. From here, let us define the choice of these parameters a launch configuration.

We can launch a maximum of  $2^{32}$  GPU thread blocks per launch, a maximum of GPU  $2^{16}$  thread blocks along the x dimension of the two dimensional space and a maximum of  $2^{16}$  GPU thread blocks along the y dimension of the two dimensional space. The GPU thread blocks have to be distributed starting from the origin (0,0) of the two dimensional space and to be contiguous along the x and y dimensions of the two dimensional space. Each GPU thread block can have a maximum of 1032 GPU threads. The GPU threads of each GPU thread block have to be distributed starting from the origin (0,0,0) of the three dimensional space and to be contiguous along the x, y and z dimensions of the three dimensional space.

Because at each fatbin file launch each GPU thread executes one or more instructions, in the next section we a) analyze how any instruction - PTX or ELF - can be executed and b) analyze the main instruction features used to discover, understand and quantify in 7 some not disclosed GPU behaviors.

#### 2.6 Instruction Configuration

The GPU executes ELF instructions. At each PTX instruction corresponds one or more ELF instructions - 6.3 - and there are ELF instructions that do not correspond to any PTX instruction - 6.6.

For each PTX instruction we do not know: 1) the type and number of ELF instructions used to execute the PTX instruction, 2) the type and number of ELF registers used in the ELF instructions used to execute the PTX instruction and 3) the type and number of dependences among the ELF registers used in the ELF instructions used to execute the PTX instruction. Because these things are important for the discussions in the next chapters we introduce here the concept of instructions configuration. The discussions in the next subsections are done considering the PTX instructions but analog discussions are valid for the ELF instructions.

#### 2.6.1 Definition

Any type of PTX instruction - add.s32, sub.u64, etc. - can be executed in two different modes: normal mode or conditional mode. The conditional mode can be executed if a guard is set at true or if a guard is set at false.

If the PTX instruction has some PTX registers then these PTX registers are usually used in previous PTX instructions and so they have - as result PTX register - a write-read dependence type to the last previous PTX instruction where they were written or - as the operand PTX registers - a read-read dependence type to the last previous PTX instruction where they were they were they were they were read.

The triplet (type of PTX instruction, mode of execution, type of dependence considered) is what we define being an instruction configuration.

#### 2.6.2 Dependence Distance

The dependence of each PTX register has a distance of zero or more PTX instructions - zero only if the PTX register a) is read more times as operand in the same PTX instruction because it is used more times as operand PTX register in the PTX instruction or b) is read and over written in the same PTX instruction because it is used as operand PTX register and result PTX register in the PTX instruction.

#### 2.6.3 Execution Time

An instruction configuration execution time is the time from the moment when, after its scheduling, the GPU hardware has to read the PTX registers used as operands in the instruction configuration to the moment when the result of the instruction configuration can be read or overwritten without waiting time caused by the writing due to the calculation of the result of the instruction configuration.

#### 2.6.4 Useless Dependence Types

If in an instruction configuration the same PTX register is read more times as operand and is written as result then we have a read-write dependence at distance zero for the PTX register.

The read-write dependences at distance zero are not considered because the execution times of each instruction configuration are by definition greater than the waiting times due to read-write dependences at distance zero.

The read-write dependences at distance greater than zero are not considered because, among all the possible read-write dependences, the read-write dependences at distance zero are the dependences requiring the minimum number of clock cycles for waiting times and their waiting times are contained in the execution times of each instruction configuration. The write-write dependence are instead not considered because between any two writes of the same PTX register used for the results of some instruction configurations we read the register at least one time and so for us the write-write dependences are without importance.

#### 2.6.5 Examples

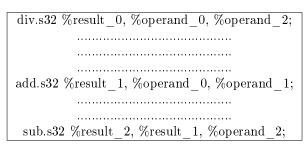

In example 1 the evidence is on the sub.s32 PTX instruction. The sub.s32 PTX instruction is executed in normal mode and the type of dependences are write-read for the PTX register %result\_1

Table 2.1: Example 1 of Instruction Configuration

and read-read for the PTX register %operand\_2. The sub.s32 PTX instruction can be seen as two instruction configurations. The first instruction configuration considers the write-read dependence of the PTX register %result\_1, this dependence has a distance in number of PTX instructions equal to 3. The second instruction configuration considers the the read-read dependence of the PTX register %operand\_2, this dependence has a distance in number of PTX instructions equal to 7.

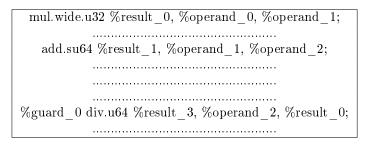

Table 2.2: Example 2 of Instruction Configuration

In example 2 the evidence is on the div.u64 PTX instruction. The div.u64 PTX instruction is executed in conditional mode - the guard has to be set at true - and the type of dependences are read-read for the PTX register %operand\_2 and write-read for the PTX register %result\_0. The div.u64 PTX instruction can be seen as two instruction configurations. The first instruction configuration considers the read-read dependence of the PTX register %operand\_2, this dependence has a distance in number of PTX instructions equal to 4. The second instruction configuration considers the the write-read dependence of the PTX register %result\_0, this dependence has a distance in number of PTX instructions equal to 6.

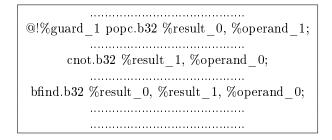

Table 2.3: Example 3 of Instruction Configuration

In example 3 the evidence is on the bfind.b32 PTX instruction. The bfind.b32 PTX instruction is executed in normal mode and the type of dependences are write-read for the PTX register

%result\_1 and read-read for the PTX register %operand\_0. The bfind.b32 PTX instruction can be seen as two instruction configurations. The first instruction configuration considers the writeread dependence of the PTX register %result\_1, this dependence has a distance in number of PTX instructions equal to 2. The second instruction configuration considers the the read-read dependence of the PTX register %operand\_0, this dependence has a distance in number of PTX instructions equal to 2.

#### 2.7 Summary

In this chapter we have introduced the reader to GPUs and in particular to all the GPUs using a GF100 or later architecture. The main points to remember from this chapter are the following:

- The PTX is a parallel thread execution virtual machine and instruction set architecture (isa) used to improve the portability of GPU code across several different GPU architectures. PTX is the lowest of the "high" level "programming languages" that we can use to edit GPU code we want executed by the GPU. The PTX code can not to be executed by the GPU in its original form, its has to be given in input to the NVIDIA compiler nvcc before of becoming GPU executable;

- Nvcc can take in input PTX or CUDA codes and always produce as output fatbin files. Inside each fatbin file there is the transformation in ELF code the GPU assembly of the code we want executed by the GPU. When a fatbin file is launched one or more parts of it are executed by the CPU and one or more parts of it are executed by the GPU using GPU threads. The GPU threads execute the ELF codes in the GPU parts;

- Each GPU thread used to execute a fatbin file has to execute all the ELF codes in the GPU parts of the fatbin file also whether, inside each one of the GPU parts, each GPU thread can follow different paths. The GPU threads executing a fatbin file has to be logically organized before of any fatbin file launch;

- The logical GPU thread organization has many degrees of freedom and these degrees are important because they determine the values of the some GPU behaviours used in the analysis/analyses of the ELF codes;

- Any PTX or ELF instruction can be executed in two different modes: a) normal or b) conditional with guard set at true or with guard set at false. For each PTX or ELF instruction different types of dependences for the PTX or ELF register used in the instruction can be considered. The type of PTX or ELF instruction, its execution mode and the type of dependence considered in each single case are important to discover, understand and quantify the GPU behaviors used in the analysis/analyses of the codes and so all together they are called instruction configuration.

In the next chapter we describe the GF100 architecture, the architecture of the GPU Tesla C2070 that we use in this thesis. We start describing the main components of the GF100 architecture and next we focus on the streaming multiprocessors, the parts of the GF100 architecture necessary to execute scientific computing. Follow a theoretical analysis about the peak performances achievable by the Tesla C2070 and a paragraph of summary about the architectural features of the Tesla C2070.

## Chapter 3

# The GF100 Architecture

#### 3.1 Introduction

In the previous chapter we have introduced the reader to the GPUs, in this we describe the GF100 architecture of the GPU Tesla C2070 that we use in the thesis.

The GF100 architecture is a modular architecture designed by NVIDIA and manufactured by TMC using a 40 nm productive process. The GF100 architecture has a die size of 529  $mm^2$  and a maximum of 3.2 billion of transistors.

Commercial GPUs using the GF100 architecture are the Fermi GTX 465, the Fermi GTX 470 and the Fermi GTX 480. Also whether gf means GPU Fermi two high end Tesla GPUs uses the GF100 architecture too. These Tesla GPUs are the Tesla C2050 and the Tesla C2070. What we know and explain in this chapter about the GF100 architecture is what NVIDIA discloses. We start describing the main components of the GF100 architecture and their features, later we move to describe particular parts of the GF100 architecture, the streaming multiprocessors - the streaming multiprocessors are the GPU parts where is executed the scientific computing. We analyze the main components of the streaming multiprocessors and get a first understanding of how such components interact one with the other. Next, considering the Tesla C2070 hardware limitations, we calculate its theoretical GPU peak performances and we conclude summarizing the disclosed architectural features of the Tesla C2070.

#### 3.2 Main Components of the GF100 Architecture

The GF100 has off chip some private gddr 5 ram, on chip a l2 cache, a constant cache, a gigathread scheduler, 4 graphics processing cluster and a maximum of 6 memory controllers. Let see what is known about each one of these components:

• *Gddr 5 Ram:* Fermi GTX cards have 256MB attached to each of the enabled gddr5 memory controllers for a total of 1.00, 1.25 or 1.50 GB. The Tesla C2050 and C2070 have 6 controllers. The Tesla C2050 has 512 MB on each of the controllers for a total of 3 GB while the Tesla C2070 has 1024 MB on each of the controllers for a total of 6 GB. The Fermi GTX 465 has a bandwidth of 102.6 GB/s for its gddr 5 ram, the Fermi GTX 470 of 133.9 GB/s, the Fermi GTX 480 of 177.4 GB/s, the Tesla C2050 and the Tesla C2070 of 144 GB/s;

- L2 Cache: The l2 cache is on chip and is at maximum of 768 KB 672 KB for GPUs like the Fermi GTX 470 and the Tesla C2070 with 14 streaming multiprocessors. The l2 cache is semi coherent because it has to keep the data present in the l1 caches but it is not necessary it keeps the data present in the shared memories and in the hardware registers.

- Constant Cache: The constant cache has a dimension of 64 KB and can be written only by the CPU. The GPU executes warps and each warp is always composed by 32 GPU threads. If all the 32 GPU threads of a warp read the same constant memory cell then all the accesses are satisfied in only one clock cycle and the data is broadcasted to all the 32 GPU threads. If instead the 32 GPU threads of a warp read 32 different constant memory cells, one for each GPU thread of the warp, at least 32 clock cycles are necessary to satisfy all the 32 different requests.

- *Gigathread Scheduler:* Each time a fatbin file is executed using a launch configuration 2.5 the gigathread scheduler has to assign the GPU thread blocks to the streaming multiprocessors and later to schedule the warps of each GPU thread block resident in a streaming multiprocessor during the whole execution of the fatbin file. The assignments and the schedulings are executed by the two gigathread scheduler levels:

- Chip Level: The gigathread scheduler assigns the GPU thread blocks to the streaming multiprocessors. After that a GPU thread block is assigned to a streaming multiprocessor the GPU thread block can not migrate. The gigathread scheduler can manage on fly a maximum of 21504 GPU threads. The assignment of the GPU thread blocks is executed considering: 1) the hardware resources available per streaming multiprocessor, 2) the hardware resources required by each GPU thread block and 3) a series of concurrent hardware design limits which a) the maximum number of resident GPU thread blocks in a streaming multiprocessor 8 b) the maximum number of GPU threads a streaming multiprocessor can manage on fly 1536 and c) the total quantity of shared memory required by the potential set of GPU thread blocks resident in a streaming multiprocessor this total quantity has to be smaller than 16 or 48 KB, 16 or 48 KB depends on how we set the GPU before the execution of the fatbin file, 3.3.

- Streaming Multiprocessor Level: The gigathread scheduler in each streaming multiprocessor is represented by 2 warp schedulers. The 2 warps schedulers concurrently schedule warps on the hardware resources of the streaming multiprocessor. The 2 warp schedulers in each streaming multiprocessor can manage on fly at maximum 48 warps 1536 GPU threads.

The assignments and the schedulings are executed at a not disclosed clock frequency but it is reasonable to assume that the schedulings are executed at a clock frequency than is half the clock frequency of the function units - the CUDA cores, the load and store units and the special function units, 3.3 - in a streaming multiprocessor.