## Università degli Studi di Padova Dipartimento di Ingegneria dell'Informazione

Scuola di Dottorato di Ricerca in Ingegneria dell'Informazione Indirizzo: Scienza e Tecnologia dell'Informazione XXVI Ciclo

# Time Lower Bounds for Parallel Network Computations

Direttore della Scuola

Ch.mo Prof. MATTEO BERTOCCO

Coordinatore d'indirizzo

Ch.mo Prof. Carlo Ferrari

Supervisore

Ch.mo Prof. GIANFRANCO BILARDI

Dottorando NICOLA ZAGO

Ai miei genitori e a Francesca

## Abstract

Direct Acyclic Graphs (DAGs) are a suitable way to describe computations, expressing precedence constraints among operations. Beyond the representation of the execution of an algorithm, a DAG can effectively represent the execution of a parallel network. This last kind of DAG has a regular structure, consisting in the repetition over time of the original network; these common representations suggest a possible uniform approach in the study of execution of algorithms and emulation of networks.

Both in parallel computing and computational complexity, DAGs have been extensively employed in the study of algorithmic features, as lower bounds for the execution/emulation time of algorithms/networks, the minimum quantity of memory needed for computing an algorithm or the minimum I/O complexity of an algorithm given a certain amount of fast memory cells. Developed techniques are quite different in their assumptions; one of the more fundamental differences is that some of them allow recomputation of intermediate results, while others disallow it, requiring the storage in memory of intermediate results for their further usages.

In nowadays computations the trade-off between data recomputation and data storing is important both in parallel and in local elaborations, since in the former we can increase the bandwidth and reduce the latency with whom data can be accessed (by computing the same data in several points of the network), while in the latter we can avoid to pay the latency of the access in memory to reload data, by recomputing them possibly loading fewer data or using data already present in memory.

So far it does not exist an universal technique able to foresee the strict lower bound for each execution of algorithm or emulation of network in each network and the known results derive from several theorems. On the contrary there are a lot of cases for which it neither exists a tight result; among these there are also emulations of extensively studied networks, such as multidimensional arrays.

The first part of our thesis starts from this state-of-the-art: we propose a survey of several known lower bound techniques involving DAGs, followed by original theorems which clarify or solve open problems. In particular, in our survey we consider lower bound techniques for execution of algorithms and emulation of networks in parallel networks, showing their principles and their limits. In the discussion we show relationships among theorems, proving that no one of them is better of the others in general terms: there are counter-examples in which each theorem gives better bounds than others. We also exhibit examples where no bound among the considered techniques is tight. Moreover we generalize some theorems originally suited for network emulations, adapting them to execution of general DAGs in parallel networks, showing examples of their application. We also consider theorems for determining minimum I/O complexity, presenting similarities and differences with emulation theorems.

One of the main results of the thesis is a new general technique which provides lower bounds almost tight (except for a logarithmic factor) in a class of network emulations including multidimensional arrays. We improve previously better known results which have a polynomial gap between lower bound and actual emulation time. Our theorem considers emulations with recomputation, giving results valid in the most general context.

Finally we consider the role of recomputation in performance, trying to understand when it gives a real advantage respect to storing intermediate results in memory. In particular we introduce the problem in simple networks, showing a class of them in which recomputation can not improve I/O performance, ending in butterfly DAGs where recomputation can save a number of I/O accesses at least as big as the fast memory available during the computation. The approach used highlights the difficulty of exploit recomputation in executions of algorithms when their DAG representation exhibits an high bisection bandwidth.

## Sommario

I Direct Acyclic Graphs (DAG, grafi orientati e aciclici) sono dei grafi che descrivono in modo semplice ed efficace le esecuzioni di algoritmi, e permettono di rappresentare graficamente le relazioni di precedenza tra le operazioni. Al di là dell'esecuzione di algoritmi, un DAG può anche rappresentare l'esecuzione di una rete parallela. Quest'ultimo tipo di DAG ha una struttura molto regolare, corrispondente alla ripetizione nel tempo della rete stessa; il fatto che l'esecuzione di algoritmi e di reti parallele abbiano questa rappresentazione comune ci suggerisce un possibile approccio unificato nel loro studio.

I DAG sono stati molto usati nello studio di caratteristiche di algoritmi, in calcolo parallelo e nello studio della complessità computazionale. Ad esempio sono stati impiegati per ottenere lower bound per il tempo di esecuzione di algoritmi e di emulazione tra reti, per la quantità minima di memoria necessaria al calcolo di un algoritmo e il numero minimo di accessi in memoria lenta durante l'esecuzione di un algoritmo con una quantità di memoria veloce predeterminata. Le tecniche sviluppate in questi studi partono da ipotesi diverse, una delle più importanti è la possibilità o meno di ricalcolare i risultati intermedi: se ciò non è possibile infatti è necessario salvarli in memoria per poterli usare in momenti successivi del calcolo.

Il trade-off tra ricalcolo e salvataggio in memoria dei dati è importante sia in ambito parallelo che nelle elaborazioni locali; infatti nel primo caso il ricalcolo può ridurre la latenza ed aumentare la banda con cui possiamo accedere ai dati in una rete di processori, calcolando gli stessi risultati in più punti della rete, mentre nel caso di elaborazioni locali il ricalcolo può evitare i problemi di latenza e banda nel recupero dei dati dalla memoria.

Ad oggi non esiste una tecnica universale in grado di fornire lower bound stretti per ogni algoritmo od emulazione di rete eseguiti in reti parallele, e i risultati conosciuti derivano da diversi teoremi. Al contrario, ci sono molti casi in cui mancano risultati stretti, anche per reti molto studiate e relativamente semplici com gli array multidimensionali.

La tesi inizia da questo stato dell'arte: la prima parte propone una panoramica delle tecniche di lower bound per DAG note, e termina con la presentazione dei teoremi originali sviluppati con la tesi, che migliorano o risolvono alcuni dei problemi aperti noti. In particolare, nella panoramica consideriamo tecniche di lower bound per l'esecuzione di algoritmi e emulazione di reti da parte di reti parallele, mostrando le idee su cui si basano e i loro limiti. Nello svolgimento vengono messe in evidenza le relazioni tra i teoremi, mostrando che attualmente nessuno di essi dà in assoluto risultati migliori: è possibile infatti presentare controesempi in cui ciascun teorema fornisce risultati più stretti degli altri. È anche possibile mostrare esempi di coppie di reti dove il miglior bound tra le tecniche considerate non è stretto. Inoltre generalizziamo alcuni teoremi originariamente pensati per emulazioni di reti e che noi adattiamo all'esecuzione di DAG generici in reti parallele, mostrandone alcune applicazioni. Consideriamo anche teoremi per determinare la complessità minima di accessi alla memoria per il calcolo di un algoritmo, mostrandone similarità e differenze con i teoremi per le emulazioni.

Uno dei risultati più interessanti della tesi è una nuova tecnica generale che fornisce lower bound quasi stretti – eccetto per un fattore moltiplicativo logaritmico – in una classe di emulazione di reti che include gli array multidimensionali. Precedentemente il miglior risultato noto differiva di un fattore polinomiale dal miglior tempo di emulazione noto. Il nostro teorema ammette il ricalcolo durante l'emulazione, ponendosi nel contesto più generale possibile.

Infine consideriamo il ruolo del ricalcolo nelle performance, cercando di capire quando esso possa dare un reale vantaggio rispetto alla memorizzazione di risultati intermedi. Introduciamo il problema partendo da reti semplici, mostrando una classe di esse in cui il ricalcolo non migliora la complessità di accessi in memoria, terminando con i DAG a butterfly, dove il ricalcolo riesce a migliorare questa complessità di un termine almeno pari alla memoria usata durante il calcolo. L'approccio usato mette in luce la difficoltà di usare proficuamente il ricalcolo durante l'esecuzione di algoritmi che presentano un'elevata connettività.

# Ringraziamenti

Dopo tanti anni e tanta fatica per completare la tesi, i ringraziamenti sono la parte più emozionante da comporre. Vorrei innanzitutto ringraziare Gianfranco per avermi seguito durante questo dottorato, trasmettendomi spunti e tecniche metodologiche che difficilmente i libri possono fornire. Assieme a lui vorrei ringraziare tutti i componenti dell'ACG, con cui ho trascorso tre anni di lavoro e di vita di cui conserverò senza dubbio un carissimo ricordo.

Oltre all'ambiente universitario, vorrei ringraziare anche tutti quelli che mi hanno supportato (e sopportato) durante il dottorato, per primi i miei genitori Umberto e Giuseppina, seguiti dal gruppo Giavera, Mauro, il gruppo Seisnet e soprattutto Francesca, mia futura moglie. Grazie a tutte queste persone gli ultimi quattro anni sono stati importanti quanto e forse più dei precedenti cinque che mi avevano portato alla laurea: ho completato la mia maturazione sia dal punto di vista professionale che come persona, partendo da studente universitario e arrivando all'inizio della mia età adulta. Arrivato a questo punto del mio percorso, con il bagaglio di esperienze maturate e accumulate negli ultimi anni, sono certo che le prossime pagine della mia vita che scriverò saranno le più importanti e le migliori.

Acknowledgements The last part of the acknowledgements is in English. In fact I would like to thank Markus for the hospitality and the interesting topics suggested during the three months that I spent at the ETH Zurich in the summer 2013. It has been an important experience in my professional and personal path, which gave me the opportunity to know the attitude of another nation. I would like to thank all the guys I knew in that period, expecially Daniele, Victoria, Georg, François, Alen, Marcela and Luca. Vielen Dank an Sie alle!

# Contents

| 1 | Intr | ntroduction |                                               |    |  |  |

|---|------|-------------|-----------------------------------------------|----|--|--|

|   | 1.1  | Gener       | al introduction                               | 1  |  |  |

|   | 1.2  | State-      | of-the-art and purpose of the thesis          | 7  |  |  |

| 2 | Low  | ver bo      | unds for generic emulations                   | 13 |  |  |

|   | 2.1  | Background  |                                               |    |  |  |

|   | 2.2  | Distar      | ace-based lower bound                         | 16 |  |  |

|   |      | 2.2.1       | State of the art                              | 16 |  |  |

|   |      | 2.2.2       | Analysis and Critique                         | 19 |  |  |

|   |      | 2.2.3       | Generalization of Theorem 1                   | 22 |  |  |

|   | 2.3  | Conge       | estion-based lower bound                      | 27 |  |  |

|   |      | 2.3.1       | State of the art                              | 27 |  |  |

|   |      | 2.3.2       | Analysis and Critique                         | 30 |  |  |

|   | 2.4  | Bandy       | width-based lower bound                       | 34 |  |  |

|   |      | 2.4.1       | State of the art                              | 34 |  |  |

|   |      | 2.4.2       | Analysis and Critique                         | 36 |  |  |

|   |      | 2.4.3       | Summary                                       | 37 |  |  |

|   | 2.5  | Parall      | el computing vs hierarchical memories         | 38 |  |  |

|   |      | 2.5.1       | State of the art                              | 40 |  |  |

|   |      | 2.5.2       | Relations with parallel computing             | 43 |  |  |

| 3 | Low  | ver bo      | unds for specific networks                    | 47 |  |  |

|   | 3.1  | Lower       | bounds for multidimensional arrays emulations | 47 |  |  |

|   | 3.2  | Mesh        | over linear array emulation                   | 52 |  |  |

|   | 3.3  | Gener       | alization to $k$ -arrays over $i$ -arrays     | 54 |  |  |

|    | 3.4   | Considerations                                 | 57         |

|----|-------|------------------------------------------------|------------|

| 4  | Sto   | ring-recomputation trade-offs                  | 59         |

|    | 4.1   | Basic facts                                    | 60         |

|    | 4.2   | Recomputation in tree DAGs                     | 61         |

|    | 4.3   | Recomputation in butterfly DAGs                | 62         |

|    |       | 4.3.1 Two general lower bounds                 | 62         |

|    |       | 4.3.2 Matching the lower bounds                | 65         |

|    | 4.4   | Recomputation in butterfly-like reduction DAGs | 71         |

| 5  | Con   | nclusions                                      | <b>7</b> 5 |

|    | 5.1   | Summary and contributions                      | 75         |

|    | 5.2   | Further research                               | 76         |

| Bi | bliog | graphy                                         | 77         |

# Chapter 1

## Introduction

#### 1.1 General introduction

Computer evolution is too slow! Since the introduction of integrated circuits in the production of computer chips at the end of 1950s, the density of transistors has doubled every 18 months, according to Moore's law [M65]. The increase rates of many other hardware systems, e.g. storage devices' capability and bandwidth, follow similar laws, allowing for the availability of cheap electronic devices, which pervade almost every aspect of current life. This exponential evolution leads a constant improvement of the performance of these devices, although modern demand of data analysis grows with a rate greater than technological achievements.

Consider for example massive data analysis, coming from scientific fields as Physics, Astronomy or Biology, as well as related to new information technology applications, as social networks or search engines. Just technological increases would not be sufficient to deal with all these data, and computer scientists have to compensate with new algorithms, often characterized by randomization, since exact computations on such large inputs would take too much time and resources.

Algorithmic contribution may be crucial also in all day applications; consider for example the Fast Fourier Transform (FFT) in signal processing or the Merge Sort algorithm in the sorting. Classical trivial algorithms would be unsuitable for modern computation requirements, unless using them on hardware much more performable, while the enhanced algorithms already are up to the situation with current hardware. The main difference between these two classes of algorithms consists in their computational complexity, which is the relation among the size of the problem and the number of operations required to solve it. Usually, enhanced algorithms has a lower asymptotic growth, so the bigger will be the problem the better these algorithms will perform respect to classical ones.

Study of computer performance To predict algorithms performance, computational complexity can be studied in theoretical computational models. These models abstract computers capabilities, maintaining the main features and hiding useless details which would complicate the analysis, allowing us to give general results, valid in a wide range of machines. Early machine models, e.g. the Turing Machine [T36], appeared in 1930s but their objective was to study what is algorithmically computable. Models whose intent was to study the complexity execution in real computer, appeared from the beginning of the 1970s.

The most prominent among these is the Random Access Machine (RAM) model [CR73]; it considers a computer as composed of a sequential processor (with fixed program) operating on a countable number of cells, which can be accessed in a time independent from their number. This model is very simple still effective in determining the operational complexity of algorithms. Unfortunately, the assumptions of infinite random access memory is unrealistic, since a bit needs a minimum volume to be stored and there is a maximum velocity at which a bit of information can travel (principles of maximum information density and of maximum information speed [BP95]), so the wider is the memory and the bigger is the latency to access a cell far from the processor respect to access a cell near to it.

To model this feature, which between the end of the 1970s and the beginning of the 1980s has been sharpened by the introduction of cache memories, several theoretical memory models have been proposed, in particular the Hierarchical Memory Model (HMM) [AACS87], the Block Transfer (BT) model [ACS87] and the two-level memory model [AV88]. These models are very useful to understand how the program execution is slowed by the interaction with memory and to promote the development of algorithms exhibiting temporal and spatial locality, strategies which try to hide or at least reduce the latency effects. Taking into

account the data movement introduces a metric different from the number of operations executed, in particular the metric which considers the number of accesses performed in the slow memories. Since actually the growth rate of speed of processors is greater than that of memory speed, for many problems this second metric is more important than that derived from the classical RAM model, since input and output operations (I/O operations) in slow memory often determine the bottleneck for the execution time. More recently, due to the large diffusion of mobile devices and in general to the increasing interest in the reduction of power consumption, also the energy aware computing has been extensively studied, both from architectural and programming points of view (e.g., [PSZ+02, PKK+04]).

In order to evaluate the performance of a given algorithm, it is useful to know which is the minimum number of operations or memory accesses required for the solution of the problem. This aspect of a computation is known as *computational lower bound*. The determination of a lower bound is usually an hard task and usually machine and memory models can not handle it, so we need to consider frameworks which explicitly target the study of lower bounds.

There are at least two kind of lower bounds: those involving a problem and those involving an algorithm, which is a particular way of solving a problem. The formers are very difficult to obtain, since we have to prove the bound for every possible strategy to solve the problem, and so far very few general and non-trivial results are known. Literature about lower bounds for algorithms is wider, also if there is not yet a general way to determine them. A typical example for this category is the lower bound of  $\Omega(n \log n)$  operations in sorting n distinct number [CLR01]. It is quite general, since it involves the class of comparison-based algorithms, but it is no more valid for example if we use numbers as indexes (as in the Counting Sort [CLR01]); moreover one could argue than having n distinct elements means having at least  $n \log n$  bits, and so the lower bound just matches the trivial one based on reading the whole input. Another example is algorithms for matrix multiplications using only scalar multiplication and addition, where a  $\Omega(n^3)$  operations lower bound is known [K70], while in general case only the trivial  $\Omega(n^2)$  lower bound is known.

As already noted above, nowadays it is fundamental to exploit the fast cache

memories, so we could be interested in lower bounds on the minimum number of accesses in the slow memory (I/O complexity) needed in order to solve a problem. One of the seminal works in this field is [HK81], followed by [S95, EPR+13], which provide extensions of the original game respectively in hierarchical memories and in a context without recomputation. Exactly this aspect of computation is currently one of the more elusive: it is clear that there is a trade-off between recomputation and I/O accesses, still it is not yet fully understood. During a computation, if an intermediate result is used more than once, we can decide if temporarily store it or recompute it. According to the particular algorithm could be more convenient the former or the latter strategy; the determination of the optimal strategy usually is a very difficult problem, also for algorithms as regular as the FFT. This topic will be examined in depth in Chapter 4. A similar problem is present also in parallel computing, as will be discussed in next paragraph.

Birth and evolution of Parallel Computing So far we considered computation only from the sequential point of view, but since the 70s also parallel computing has been extensively studied. This term can refer to several forms of parallelism: bit-level parallelism, which consists in augmenting the number of bit elaborated per instruction increasing the word-size of the processor, instruction-level parallelism, which consists in conveniently designing the processor to pipeline the execute of instructions, obtaining an higher throughput and task-level parallelism, which consists in exploiting more processors during the execution of a program. The first two kinds of parallelism have been part of the evolution of sequential cores, so they have been transparent to developers. If we take an old sequential program and make it run on a computer with higher bit-level or instruction-level parallelism it almost automatically will improve its performance. Since the limit of VLSI technology is going to be reached, over the last ten years evolution of sequential processors is getting harder and harder and it is more advantageous to explicitly design processors with more computational cores respect to further improve the power of a single core. This kind of evolution is no more transparent to developers: we have to produce programs which explicitly use more cores since an old sequential program will just use one of them.

This third kind of parallelism is whom we usually refer to when we talk about parallel computing: the exploitation of several processing units at once, in order to reduce the time needed for the solution of a certain problem respect to sequential computing. This task is not so trivial, in fact the various processors need for communication and synchronization during the execution. Note that this problem heavily relies on the network joining the processors (every processor could be able to communicate with every other processor, or only with a part of them). The usage of parallel machines has been largely relegated to the research environment until few years ago, since, as we said above, before improving sequential cores was more advantageous. This leads to the fact that nowadays parallel computing has less established technological and programming standards.

Due to the higher number of freedom degrees of this field, the study of parallel machines did not follow exactly in sequential computing footsteps. Initially performance were not only studied in ideal parallel machine models, but also in machines with specific network configurations. Among the formers, the main model is the Parallel Random Access Machine (PRAM) [FW78, G78], consisting in a collection of processors, sharing a certain amount of memory cells. This framework allows to understand intrinsic difficulties of problems, but it ignores the communication complexity in which algorithms incur once they are implemented in a real machine, which also in this field is nowadays the real bottleneck for computations. Parallel algorithms are usually described by very high level languages (as the Work-Time Framework [Jaja92]), which aim to express the maximum parallelism and the minimum number of parallel steps reachable in the PRAM, and leave the communication problem to the particular implementations. This description for algorithms is very useful since we can easily see how their main features scale in different machines thanks to Brent's theorem [B74]. Conversely to the PRAM case, analysis performed on specific networks of processors are not enough general to highlight features of problems without being influenced by the considered networks. This motivates in the nineties the study of several high level, still realistic, models like BSP [V90], LPRAM [ACS90], LogP [CKP+96], D-BSP [DK96]. In these models we can study the communication complexity of problems without being misled by a particular network.

In parallel computing, maybe more than in sequential field, we are very interested in performance: in fact we are explicitly trying to exploit a new intrinsic feature of problems: the parallelism. The Amdahl's law [A67] limits our action field only to the fraction of the algorithm which can be parallelized, so if great part of the problem is strictly sequential, the improvement will be small. Once determined the leeway, we would like to know which is the minimum time required for the execution of a problem or of an algorithm with the available hardware. There is a natural bound on parallel time obtained from the ratio between the best sequential execution time and the number of processors available. When the number of processors is high respect to the problem size, this bound gets weaker and weaker, in fact it does not catch the complexity of the precedence constraints among the operations executed for the solution of the problem.

If we suppose to use a machine with infinite processors, executing each operation as soon as all its predecessors have been computed, we can execute a specific algorithm in the minimum parallel time possible for it: this quantity is the depth of the algorithm. The best sequential algorithm not necessarily provides also the lower parallel depth, so than often sequential algorithms must be rearranged or totally redesigned to exhibit a lower depth. In parallel computing we are interested in algorithms with the lowest depth possible, using a reasonable number of processor. Another optional yet attractive quality for these algorithms is to be work optimal, that is to have a number of operations similar to the best sequential algorithm. The determination of the lowest depth for a problem is a difficult task, also if for some problems it is feasible reasoning on how much data can be analyzed with the available processors. Important results of this kind are the  $\Omega(\log n)$  time required for the computation of the OR function [CD82] and exact lower bounds for searching, merging and sorting [K83]. If we consider a specific network of processors, the task gets slightly easier, since we can point out lower bounds due to the data movement and possible communication bottlenecks. However this kind of lower bound is not general, since it is due to physical features of the networks, and it does not provide general information about the complexity of the problem.

As anticipated in previous paragraph, also in this field we should take into ac-

count the possibility of recompute intermediate results in order to avoid communication among distant processors and possibly obtain better algorithms. Given the generality of this approach, it is very difficult to obtain general lower bounds which can tightly catch the computational complexity when this strategy is allowed. This aspect will be extensively discussed in the rest of the thesis.

## 1.2 State-of-the-art and purpose of the thesis

This thesis makes a critical survey of the known lower bound techniques which target parallel computation of algorithms and completes some aspects which are still open.

Literature in this field can be divided according the considered network model, which can be an ideal PRAM, an high level but realistic model or a specific network, and according the consideration of recomputation, which can be allowed or not.

As for ideal PRAM, we can find the already mentioned [CD82], which proves a  $\Omega(\log N)$  time lower bound for the computation of the OR function in a CREW PRAM (while a trivial constant time algorithm exists for CRCW PRAM). [PU87] proposes a trade-off between time and communication required for the computation of the diamond DAG, showing that the product of optimal lower bounds for time and communication considered singularly is strictly smaller than lower bound obtained considering jointly time and communication; this means that in some DAGs the PRAM can not match both the minimum time and the minimum communication with the same strategy. Finally [K83] present several tight lower bound for searching, sorting and merging in the PRAM.

In [VW85] the PRAM(m) model is introduced, which consists in a PRAM with only m cells of global memory, modeling a bandwidth limit of m data per time unit. It has been studied both with exclusive read and concurrent read memory access policies, leading to lower and upper bounds where the execution time take into account the bandwidth (e.g. [ABK95] for sorting, which also shows how the technique can be adapted to [CKP+96, V90], cited in the following lines).

Starting from [PU87], [ACS90] considers the LPRAM, a variation of PRAM which captures also communication costs, providing time and communication

lower bounds for several problems as matrix—matrix multiplication, sorting, FFT. Beyond LPRAM, where we need to exhibit two distinct lower bounds for communication and time, among general realistic models there are the P-Log [CKP+96] and the Bulk Synchronous Parallel (BSP) [V90], theoretical machines which can describe a wide range of real networks thanks to their parametrized structure. Time lower bounds for these model contain in their formulas parameters for latency and bandwidth of the network which connects the processors, so that the time lower bound already expresses also the communication complexity. For relationships between the two models see [BHP+96]. BSP has been extensively studied and strict results are known in several fundamental problem [BSS12, SS14], It has been extended to take into account the locality in parallel computation in [DK96], where the Decomposable BSP is introduced. In this model bandwidth and latency are variable, and computations take less time for algorithms exhibiting communication among near processors. It is possible to prove which D-BSP can model processor networks more effectively than BSP, allowing emulations with only a constant factor slowdown for several networks, e.g. multidimensional arrays, see [BPP07] for a complete dissertation.

Note that there are several works, e.g. [CGG+95, LP93, FPP06, PPS06, MZ12], proposing cross-emulations or highlighting similarity among parallel and memory models, so that computational bounds in memory models are strictly related to the parallel ones. See section 2.5 for a deepened introduction to the argument.

Turning our attention on bounds for processor networks, we recall works on Universal Computer; an universal computer is a parallel machine with fixed communication network of bounded degree which aims to emulate as efficiently as possible any other bounded degree network. A N-nodes universal computer can emulate all N-nodes bounded-degree network with slowdown at least  $\Omega(\log N/\log\log N)$  [M83], while if the machine has  $N^{1+\epsilon}$  nodes it can emulate any N-nodes bounded-degree network with slowdown O(1) [M86].

Other works consider different hypothesis, e.g. in [BP99] networks of processors are integrated with a local hierarchical memory and in general it target emulations respecting realistic physical constraints. In this paper no recomputation is allowed.

A powerful emulation technique is the definition of an embedding of the guest network into the host network; in Section 2.1 basic results about embedding are recalled. Embeddings allow optimal emulation of trees in multidimensional arrays [HKMU91], and are involved as subpart of other optimal emulation techniques. For example a plain embedding can not provide a constant slowdown emulation between the mesh network and the butterfly network, since any embedding of the former in the latter as at least dilation  $\Omega(\log N)$ , but embedding of sub-meshes in sub-butterflies are exploited in the O(1)-slowdown emulation proposed in [KLM+97].

In this last paper work-preserving emulations are considered; an emulation of a guest by an host is work-preserving if work performed by the host is similar to work of the guest,  $W_H = O(W_G)$ . In particular authors prove two theorems to determine lower bounds of the time required from a network to emulate the computation of another network when recomputation is allowed. These theorems are used to investigate the maximum size of an host to obtain a work-preserving emulation of a guest. In the same paper there is a survey of known emulations among networks, used to prove the optimality or looseness of lower bounds provided by the previous theorems. On the same line [KR94] proposes a lower bound technique for network emulations considering bandwidth of networks, imposing at most a constant level of recomputation. Also in this case the theorem is used to investigate maximum size of hosts to perform a work-preserving emulation of a guest and results reached are the same of [KLM+97] in several cases, but with a more intuitive approach.

Note that especially when recomputation is allowed, lower bounds not always are strict. For this reason can be useful to recall the already mentioned work of Hong and Kung [HK81], which deals with minimum number of accesses in slow memory when executing an algorithm with finite amount of fast memory and recomputation enabled. Note that saving I/O accesses replacing it with recomputation is related to save communication replacing it with recomputation in parallel environment. Also this field lacks fundamental proofs of the role of recomputation in performance.

Finding significant lower bounds for problems could also solve important questions in Computational Complexity field. For example if we could prove a polynomial lower bound for a problem in  $\mathcal{P}$  (problems for which an algorithm polynomial in the size of the input is known), we could demonstrate that  $\mathcal{NC} \subsetneq \mathcal{P}$ , where  $\mathcal{NC}$  is the Nick Class, the class of problems solvable in polylogarithmic time when a number of processors polynomial in the size of the input is available. This would means that not all the problems which are efficiently solvable in sequential way are also highly-parallelizable. Even more important, if we could exhibit a super-polynomial lower bound for some problem in  $\mathcal{NP}$ , we would know that  $\mathcal{P} \subsetneq \mathcal{NP}$ , where  $\mathcal{NP}$  is the class of problems solvable in polynomial time with a non-deterministic Turing Machine. This would means that not every problem is tractable with actual computers, and that exist problems which are not computable in useful time also for small instances.

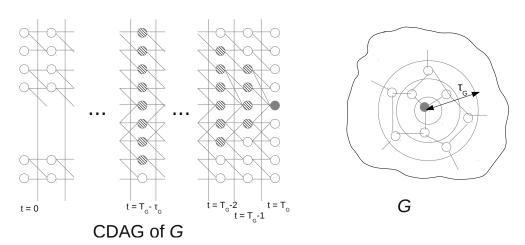

The rest of this thesis is divided in two parts: the first one includes Chapters 2 and 3 and it is about time lower bounds for emulations, while the second one includes Chapter 4 and is about trade-offs between recomputation and storing of intermediate results. In Chapter 2 we will consider lower bound techniques – allowing recomputation – valid for a wide gamma of networks from [KLM+97, KR94]. These techniques model an arbitrary pair of networks through some parameters which lead to a general formulation of lower bounds. Given a specific pair of networks we can determine the current value of the lower bound by just computing the parameters for the specific case. In the treatise, we show relationships among the techniques, highlighting their weaknesses and extending them to general DAGs. An important fact proved in the thesis is that among the considered techniques there is not one strictly more powerful than the others, in fact we can exhibit cases where each technique gives better bounds than the others. Moreover we highlight differences between theorems for lower bounds for I/O complexity and those for parallel computations.

Chapter 3 contains new results for lower bounds of specific emulations, in particular we consider emulations among multidimensional arrays: actually, the better known result has a polynomial gap with the better known emulation when arbitrary recomputation is allowed, while our theorem only suffers from a logarithmic gap. The proposed strategy can be extended to arbitrary networks but it is effective only for determinate classes of them.

Chapter 4 addresses the role of recomputation in the execution of algorithms

from the point of view of I/O complexity. When recomputation is not allowed, partial results which have to be used again, must be stored in memory, while with recomputation in some case it is possible to save memory accesses by recomputing those results. The main result of this section is the proof that recomputation gives only a small advantage in the butterfly but asymptotically it has the same complexity and the same constants of the case without recomputation.

Finally, Chapter 5 concludes the thesis summarizing the contribution and proposing possible further researches.

I would like to remember that great part of results contained in Chapter 4 have been obtained in the three months that I spent at ETH Zurich, with Markus Püschel as advisor.

# Chapter 2

# Lower bounds for generic emulations

Given two processor networks, which is the fastest possible emulation of the first network performed by the second one? Starting from this question, in this chapter we will present a survey of known techniques to obtain time lower bounds for network emulations, showing the main ideas beneath them, the reciprocal relations and extending them to more general cases. We will show that actually there is not a single technique all-comprehensive, but we must consider several techniques to obtain tight lower bounds in networks with different features. Moreover we analyze weaknesses of the discussed theorems, giving a starting point for a possible all-comprehensive technique.

Some of the points left open in this chapter will be solved in Chapter 3, as for example a lower bound for emulations among multidimensional arrays.

## 2.1 Background

Before proceeding with the exposition, we recall some concepts extensively used in the rest of the work.

**Definition 1.** A Parallel Random Access Machine (PRAM) [FW78, G78] is an abstract parallel machine model, that consisting in a collection of P synchronous processors and M shared memory locations.

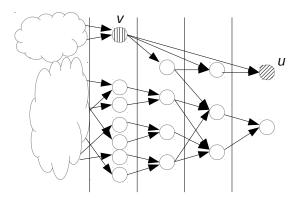

Beyond ideal machines, where every processor can communicate with each other in one step by the shared memory (shared memory model), we will consider machines with a given interconnection among their processors and where communication occurs by sending and receiving messages through edges of the interconnection network (similarly to the message passing model). In this second case, each processor has M local memory locations, accessible in one step only by processors which are joint to it by the network. A network is modeled by a undirected graph G = (V, E), where vertices in V (also called nodes) represent processors and edges in E represent connections among processors. We refer to [KLM+97] for definitions of the topology of butterfly, k-dimensional array and tree networks.

During the thesis we will consider emulations of a network G by another network H, which consist in the reproduction of all intermediate results of the computation of G with H. One possible way to specify an emulation is by means of an embedding.

**Definition 2.** Consider a guest network G = (V, E) and an host network H = (W, F). An *embedding* of G in H consists in two functions,  $\phi : V \to W$ , which maps every node of V in a node of W, and  $\psi : E \to \{\text{paths in } F\}$ , which maps edges of G in paths in H. An embedding is characterized by its *dilation* d, which is the maximum length of a path  $\psi(e)$ , its *congestion* c, which is the maximum number of paths  $\psi(e)$  passing on an edge of H and its *load* I, which is the the maximum number of nodes of G mapped to a node of H.

If there is an embedding of G in H with parameters c, d and l, then it exists an emulation of G by H with slowdown O(c+d+l) [LMR88].

We will represent a computation as a *directed acyclic graph* (DAG) where, informally, nodes represent operations and edges represent the dependences among operations. Following definition is a variation of that in [BP01].

**Definition 3.** A DAG or computation directed acyclic graph (CDAG) is 4-tuple C = (I, V, E, O) of finite sets such that:

- 1.  $I \cap V = \emptyset$ ;

- 2.  $E \subseteq (I + V) \times V$  is the set of arcs;

- 3. G = (I + V, E) is a directed acyclic graph with no isolated vertices;

- 4. *I* is called the *input set*;

- 5. V is called the operation set and all its vertices have incoming arcs;

- 6.  $O \subseteq I + V$  is called the *output set*.

Every node that can reach  $u \in V$  with a path is a *predecessor* of u, in particular if a predecessor of u is directly connected to u than we call it *parent* of u. Similarly, every node reached by a path from u is a *successor* of u, in particular a successor of u directly connected to u is a *son* of u. Usually in this work we will consider nodes without predecessors as *inputs*, while nodes without successors as *outputs*.

Note that a DAG is given by a particular execution of an algorithm. Different executions of the same algorithm can give different DAGs. DAGs are very useful in the analysis of an algorithm, e.g., they can be used to study the space complexity [HWV77] or the I/O complexity [HK81], in both cases by pebble games. Next definition recalls the general idea behind pebble games, but games in [HWV77, HK81] are quite different among them.

**Definition 4.** A pebble game on a DAG G is the following game. The player has a certain number of pebbles which he can use to mark (to pebble) nodes of G, one in any step of the game. As long as there are available pebbles, an input can always be pebbled. Other nodes can be pebbled only if all their predecessors are currently pebbled and there are pebbles available. If there are no more available pebbles, we can unpebble some nodes (one per step of the game), freeing the pebbles used in them. The game ends when every output has been marked at least once.

Pebbles in the games represent memory locations used during the computation. Note that pebble game in [HWV77] aims to determine the minimum amount of memory required for execute an algorithm, while the game in [HK81], performed with pebbles of two colors, has the purpose of determine the minimum number of accesses in slow memory required by an algorithm. We can also think pebbles as parallel processors occupied in the execution of the DAG; in

this game in the game we can perform as many moves per step as many pebbles are available.

A certain sequence for the creation of nodes of the DAG G is called *schedule*, in particular the *greedy schedule* assumes infinite pebbles and schedules nodes as soon as they are ready. The greedy schedule of G in the parallel case defines a partition  $p_0, p_1, \ldots, p_{D-1}$  of its nodes, where set  $p_0$  contains inputs and set  $p_i$  contains nodes created at step i. This schedule provides useful features of G, in particular its  $depth\ D$  – the minimum number of steps required by a PRAM to compute the DAG – and its maximum parallelism  $\max_i p_i$ . We also define the  $work\ W$  of G as  $W = |V_G| = \sum_{i=0}^{D-1} p_i$  and the  $average\ parallelism\ p = W/D$ . Note that if we limit the available processors to p, we can schedule G in  $\sum_{i=0}^{D-1} \lceil p_i/p \rceil \leq \sum_{i=0}^{D-1} p_i/p + \sum_{i=0}^{D-1} 1 = 2D$ .

### 2.2 Distance-based lower bound

#### 2.2.1 State of the art

#### Notation

First, we will analyze two techniques from [KLM+97], which consider the emulation of an  $N_G$ -nodes guest network G, executing for  $T_G$  time steps, by an  $N_H$ -nodes host network H, which requires  $T_H$  time steps to perform it. Note that both the techniques are very general, and they are valid also if recomputation is allowed. The aim of the paper is to investigate in which case a network H can perform an efficient emulation of G, where the efficiency is the ratio among works performed by G and H. In particular, authors give two general methods to determine lower bounds of the inefficiency, defined as  $I = \frac{T_H N_H}{T_G N_G}$ . In an efficient emulation  $\frac{T_H N_H}{T_G N_G} = O(1)$ , and it is called work preserving. In this thesis we are interested in a more general target: the tightness of the bounds.

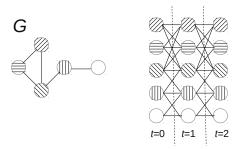

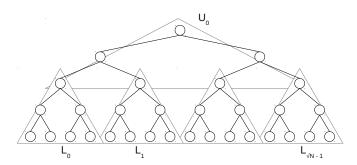

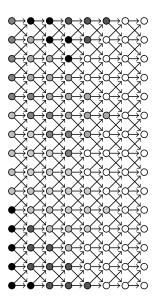

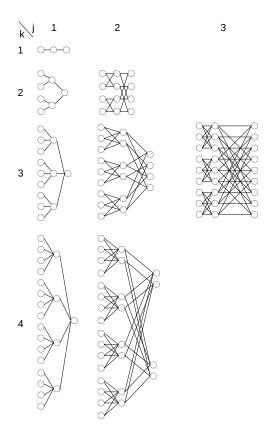

The computation of G is considered as a DAG, whom H has to pebble. In particular, nodes of G have a constant memory and in each step they can communicate their status to every neighbour. Note that the DAG considered, been produced by a network, has a very regular structure and its features are related to those of G. If G executes for T steps, the produced DAG has  $TN_G$  nodes and can be thought as T levels, each with  $N_G$  nodes, one per node of G (Fig. 2.1). Level  $\tau$  contains nodes of G at time step  $\tau$ , and the only edges in the DAG are those from level i to level i+1,  $i=0,1,\ldots,T-1$ . We refer with  $(u,\tau)$  to the

Figure 2.1: DAG produced by the execution of a network G in 3 time steps.

node of the DAG representing the status of node u of G in the time step  $\tau$ . Let  $\delta(u,v)$  be the length of the shortest path between u and v in a given undirected graph G; then  $B_G(u,i) = \{v \in V_G : \delta(u,v) \leq i\}$  and  $b_G(u,i) = |B_G(u,i)|$ . Node  $(u,\tau)$  receives as input  $(u,\tau-1)$  and  $\{(v,\tau-1) : v \in B_G(u,1)\}$ , while it is an input for  $(u,\tau+1)$  and for  $\{(v,\tau+1) : v \in B_G(u,1)\}$ .

#### The Theorem

**Theorem 1.** Let  $G = (V_G, E_G)$  be an  $N_G$ -nodes guest network and  $H = (V_H, E_H)$  be an  $N_H$ -nodes host network. Suppose that there are integers  $\tau_G$  and  $\tau_H$  such that

$$\max_{u \in V_H} \sum_{i=1}^{\tau_H} b_H(u, i) < \min_{v \in V_G} \sum_{j=1}^{\tau_G} b_G(v, j).$$

(2.1)

Then any emulation of  $T_G \ge \tau_G$  steps of G by H has slowdown

$$S > \frac{\tau_H + 1}{2\tau_G}.$$

Here we just sketch the main idea behind the theorem; see [KLM+97] for the complete proof. Given a node (v,t) of the DAG of G, it has  $b_G(v,1)$  predecessors at time step t-1,  $b_G(v,2)$  in time step t-2 and so on, until having  $b_G(v,\tau_G)$  predecessors at time step  $t-\tau_G$  (Fig. 2.2).

We are interested in the node v which has  $P = \min_{v \in V_G} \sum_{j=1}^{\tau_G} b_G(v, j)$  prede-

Figure 2.2: Quantity represented by  $\sum_{j=1}^{\tau_G} b_G(v,j)$ .

cessors, the minimum number of predecessors in the previous  $\tau_G$  time steps (the "weaker" node of G). Similarly we can find out the node u in H, which in the previous  $\tau_H$  steps has the maximum number of predecessors respect to nodes in H, but they are strictly less than P. This means that any node in G, in  $\tau_G$  time steps, can be influenced by P operations, while any node in H needs strictly more than  $\tau_H$  steps to be contacted by such a quantity of information.

Focus on first evaluation of  $(v, T_G)$  by a node u of H, at time  $T_H$  of the network H. There is at least one node v' in the region of the DAG of G influencing  $(v, T_G)$  during the time  $[T_G - \tau_G, T_G]$  computed by H before  $T_H - \tau_H$ . We can repeat such a construction for node v', obtaining another region of G with predecessors at most in time step  $T_G - 2\tau_G$  with a node v'' computed in H before time  $T_H - 2\tau_H$  in H. Repeating this reasoning, we obtain  $\Omega(T_G/\tau_G)$  regions of DAG of G, each requiring at least  $\Omega(\tau_H)$  disjoint steps in the emulation performed by H, so that  $T_H = \Omega(T_G\tau_H/\tau_G)$ , or  $S = \Omega(\tau_H/\tau_G)$ .

In [KLM+97], Theorem 1 is used to prove the following fact.

Corollary 1. For fixed k, any emulation of a complete binary tree G by a k-dimensional array H has slowdown at least  $\Omega((N_G/\log^k N_G)^{1/(k+1)})$ .

In [KLM+97], authors stress the fact that a N-nodes k-array can perform a work-preserving emulation of a  $(N^{(k+1)/k}/\log N)$ -leafs complete binary tree. One should also note that the known embeddings of a tree on a k-dimensional array are optimal for each value of  $N_H$ . In fact when the k-dimensional array

has diameter  $\Omega((N_G \log N_G)^{1/(k+1)})$ , it can match the lower bound in Corollary 1 with embeddings proposed in [HKMU91], while for smaller diameters, since an M-nodes k-dimensional array can emulate in work preserving fashion an N-nodes one (M < N), we can match the trivial load lower bound  $\Omega(N_G/N_H)$  also provided by the theorem.

#### 2.2.2 Analysis and Critique

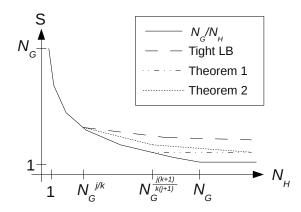

Now we will highlight the aspects of the computation catched by the theorem. We will use as working example the emulation of a k-dimensional array G with a j-dimensional array H, k > j. If  $N_H = O\left(N_G^{\frac{j}{k}}\right)$ , H can perform an emulation of G with slowdown  $O(N_G/N_H)$ , while for bigger values of  $N_H$ , H can not perform a work preserving emulation of G and there is an inefficiency more than constant [KLM+97].

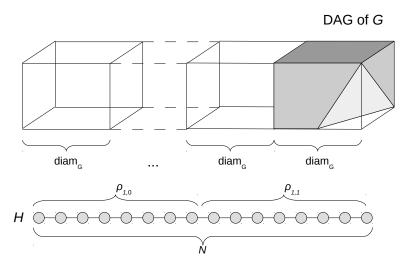

Given an N-nodes x-dimensional array A, we can prove that

$$\sum_{i=1}^{\tau} b_A(u,i) = \begin{cases} \Theta(\tau^{x+1}) & \text{if } \tau \le \text{diam}_A\\ \Theta(N^{\frac{x+1}{x}}) + N(\tau - \text{diam}_A) & \text{if } \tau > \text{diam}_A \end{cases} . \tag{2.2}$$

If the execution time  $\tau$  considered is smaller than the diameter of the network, the number of predecessors of u grows as  $\Theta(\tau^{x+1})$ , otherwise, if the execution time is long enough the growth is just linear respect to  $\tau$  (since the whole network has already been reached after first diam<sub>A</sub> steps).

If  $\tau_G = \operatorname{diam}_G = N_G^{\frac{1}{k}}$ , right term of Equation 2.1 is  $\Theta\left(N_G^{\frac{k+1}{k}}\right)$ , while for the left term, depending on the size of H, we distinguish two cases, which lead to two different values for  $\tau_H$ .

If diam<sub>H</sub> =

$$\Omega\left(N_G^{\frac{k+1}{k(j+1)}}\right)$$

:

$$\Theta\left(\tau_{H}^{j+1}\right) = \Omega\left(N_{G}^{\frac{k+1}{k}}\right) \Rightarrow \tau_{H} = \Omega\left(N_{G}^{\frac{k+1}{k(j+1)}}\right),\,$$

while if  $\operatorname{diam}_{H} = o\left(N_{G}^{\frac{k+1}{k(j+1)}}\right)$ :

$$N_H \left( \tau_H - \operatorname{diam}_H \right) = \Omega \left( N_G^{\frac{k+1}{k}} \right) \Rightarrow \tau_H = \Omega \left( \frac{N_G^{\frac{k+1}{k}}}{N_H} \right).$$

Figure 2.3: Comparison among tight lower bound, lower bound implied by load argumentation and lower bound due to Theorem 1 and 3. Tight lower bound is determined by ratio of bisection bandwidths for  $N_H > N_G^{\frac{j}{k}}$  (see Theorem 4 and Chapter 3).

These values give respectively slowdown  $S = \Omega\left(N_G^{\frac{k-j}{k(j+1)}}\right)$  and  $S = \Omega\left(N_G^{\frac{N_G}{N_H}}\right)$ . Note that the theorem considers a region of H with radius at most  $O\left(N_G^{\frac{k+1}{k(j+1)}}\right) < N_G^{\frac{1}{j}}$ . If H has more than  $\Theta\left(N_G^{\frac{j(k+1)}{k(j+1)}}\right) < N_G$  nodes, these will not affect the lower bound, since they are too far to communicate with other parts of the network without slowing down the computation. Viceversa, if H is small, we just obtain the trivial slowdown due to ratio among the number of nodes of G and those of G and those of G and those of G are considering the class of G and those of G are considered as a particular structure, in which the network G with diameter diam G is a sub-network of the network G with diameter diam G is a sub-network of the network G with diameter diam G is a sub-network in which lower bound due to average distance of nodes can be improved by an argumentation based on average load of a region.

Moreover, lower bound obtained by the theorem in this case is not tight (see Figure 2.3 and proof of Proposition 4 in next subsection). The main issue which determines this gap is the fact that the theorem takes into account only the number of operations which a certain subregion of H can perform, without considering further communication problems among its nodes. The involved subregion is considered as an ideal PRAM, so that possible congestion problems in its edges are ignored.

Note also that for small value of  $\tau_G$ , the lower bound could be not tight, since the theorem first considers the less connected part of G and the more connected part of H, which could lead to a weak bound. This fact is formalized in the following proposition.

**Proposition 1.** Lower bound obtained by the application of Theorem 1 to networks G and H is not necessarily tight if

$$\max_{v \in V_G} \sum_{j=1}^{\tau_G} b_G(v, j) = \omega \left( \min_{v \in V_G} \sum_{j=1}^{\tau_G} b_G(v, j) \right).$$

(2.3)

Proof. We will prove the theorem by counter-example. Consider the network G consisting in a N/2-nodes 3-dimensional array (a cube) joined with an N/2-nodes linear array by an edge from a vertex of the cube and a vertex of the array (it has diameter  $N/2 + O(N^{1/3})$ ), and H consisting in an N-nodes 2-dimensional array. Network H can not emulate the cubic part of G without a certain amount of slowdown (we know from Theorem 1 that  $S = \Omega(N^{1/9})$ ). Nevertheless, considering the whole G, the theorem does not highlight any slowdown:  $\min_{v \in V_G} \sum_{j=1}^{\tau_G} b_G(v,j) = \Theta(\tau_G^2)$  for  $\tau_G < O(N)$  and  $\max_{u \in V_H} \sum_{i=1}^{\tau_H} b_H(u,i) = \Theta(\tau_H^{3/2})$  for  $\tau_H < O(N^{1/2})$  give only pairs  $(\tau_G, \tau_H)$  such that  $S = \Omega(\tau_H/\tau_G) = \Omega(1)$ , since the theorem is biased by the weaker part of G.

**Proposition 2.** Lower bounds obtained by Theorem 1 are not necessarily tight.

*Proof.* This result follows by Proposition 1.

$$\Box$$

Lower bound in Corollary 1 is tight since binary tree is a loosely connected network and the optimal embedding in a k-dimensional array condenses the subtrees near the leaves in just one node of the array. In this case, increasing the

load of some nodes of H does not increase the congestion of the network (the sub-trees communicate with just one node with the rest of the network).

Informally, the theorem is likely to be tight as long as the load and dilation (features of the emulation caught by the theorem) are bigger than the congestion (feature not considered by the theorem). Theorem 3 of Section 2.3 tries to solve this lack.

#### 2.2.3 Generalization of Theorem 1

Theorem 1 considers the emulation of a network G by a network H modeling computation of G as a DAG. This subsection generalizes the theorem to target a general DAG F in place of the DAG obtained by the computation of a network.

As already noticed, DAG of computation of G for a certain time  $T_G$ , is very regular. Consider its greedy schedule: each level i has  $N_G$  nodes, corresponding to the evaluation of all nodes of G at time i; moreover level i has only edges to level i+1. Because of this regularity, once we identify  $m_G = \min_{v \in V_G} \sum_{j=1}^{\tau_G} b_G(v,j)$  in the network G, we know that any node in the DAG of G has at least  $m_G$  predecessors in previous  $\tau_G$  time step; in particular  $b_G(v,j)$  counts the number of predecessors of v exactly j time steps before v. The theorem, as recalled in Subsection 2.2, identifies k nodes and relative predecessors in the DAG of G which imply  $T_G < (k+1)\tau_G$ , while H needs  $T_H > k\tau_H$  time steps to emulate them.

Consider the greedy schedule of a general DAG F: it has  $T_F$  levels. In this case each level does not correspond to a time step of execution of a network, as well  $T_F$  is not the number of steps but simply the critical path of F. In analogy to Theorem 1, we can represent a node v of F as v = (u, t), where t is its level in the greedy schedule and u is a unique name in F. Each level t could have a different number  $p_t$  of nodes and its nodes could be input also for nodes of levels other than t + 1 (see Figure 2.4). Definitions of functions  $B_G$  and  $b_G$ , which in a network G counts neighbors of a node within a certain range, are valid also in a DAG F. Note that in this case F is the DAG, and nodes in the set  $B_F(v,i)$  are all in levels preceding level of v; moreover the meaning of  $\min_{v \in V_G} \sum_{j=1}^{\tau_G} b_G(v,j)$  in DAG of G in Theorem 1 is now assumed in DAG F

simply by  $b_F(v, \tau_H)$ . Let  $P_F(v, i) = \{u : \delta(u, v) = i\}$  and  $p_F(v, i) = |B_F(v, i)|$ , then  $b_F(v, \tau_H) = \sum_{i=1}^{\tau_H} p_F(v, i)$ , similar to the notation for a DAG of a network, also if nodes in  $p_F(v, i)$  are not necessarily in the same level. For example in Figure 2.4,  $v \in B_F(u, 1)$ , but v precedes u by three levels.

Figure 2.4: Greedy schedule of a general DAG: different levels can have different numbers of nodes and some node (e.g., v) can be used by several levels.

This invalidate the reasoning used in the original theorem to determine  $T_G < (k+1)\tau_G$ ; in fact if we consider the last node  $v = (u, T_F)$  of F compute by H, it is not true that it has  $m_F$  predecessors  $(u', t), t \geq T_F - \tau_F$ . In any case, if there is a limit  $\Delta$  to the maximum distance in level between a node u and an its parent, we can prove the following theorem.

**Theorem 2.** Let  $F = (V_F, E_F)$  be a  $N_F$ -nodes DAG and  $H = (V_H, E_H)$  be an  $N_H$ -nodes host network. Consider the greedy schedule of F; let  $T_F$  be the critical path and  $\Delta$  be the maximum distance in levels between a node u and the furthest parent of it. Suppose that there are integers  $\tau_F$  and  $\tau_H$  such that

$$\max_{u \in V_H} \sum_{i=1}^{\tau_H} b_H(u, i) < \min_{v \in V_F} b_F(v, \tau_F).$$

Then the number of time step of any computation of F by H is

$$T_H \ge \left(\frac{T_F}{\tau_F \Delta} - 1\right) (\tau_H + 1).$$

*Proof.* Proof follows that of Theorem 1. Consider the last node  $v_0 = (u_0, T_F)$  of F computed by H. Node  $v_0$  has  $b_F(v_0, \tau_F) \ge \min_{v \in V_F} b_F(v, \tau_F) = m_F$  predecessors

between levels  $T_F - \Delta \tau_F$  and  $T_F - 1$  (we are considering predecessors at distance at most  $\tau_F$  and each step could require up to  $\Delta$  levels). Consider the node u of H which computes  $v_0$  at host time  $T_H$ . A predecessor of  $v_0$  created by a node at distance i from u must be created before time  $T_H - i$  to influence the computation of u at time  $T_H$ , so from time  $T_H - \tau_F$  to  $T_H - 1$  at most  $\max_{u \in V_H} \sum_{i=1}^{\tau_H} b_H(u,i) < m_F$  operations can influence computation of u and there is at least one node  $v_1 = (u_1, t_1)$  computed by H at time  $T_H - (\tau_H + 1)$  which occurs at or after level  $t_1 \geq T_F - \Delta \tau_F$  in F.

We can repeat the reasoning on node  $v_1$ , pointing out a node  $v_2 = (u_2, t_2), t_2 \ge T_F - 2\Delta\tau_F$  computed by a node of H before time  $T_H - 2(\tau_H + 1)$ . After k repetitions, we obtain a certain  $t_k < \Delta\tau_F$ ,  $t_k \ge T_F - k\Delta\tau_F$  computed by H at or before host time  $T_H - k(\tau_H + 1) \ge 0$ . We can merge  $T_F < (k+1)\Delta\tau_F$  and  $T_H \ge k(\tau_H + 1)$  to obtain:

$$T_H \ge \left(\frac{T_F}{\tau_F \Delta} - 1\right) (\tau_H + 1).$$

(2.4)

Asymptotically, Equation 2.4 becomes  $T_H = \Omega(T_F \tau_H/(\Delta \tau_F))$ . Note that in some important DAGs (e.g, tree, butterfly, diamond)  $\Delta = 1$ .

**Application 1.** Consider the execution of an  $N_F$ -leaves tree DAG F on an  $N_{H}$ -nodes k-dimensional array H. As for tree, when  $\tau_F \leq \log N_F$ ,  $b_F(v, \tau_F) = 2^{\tau_F + 1} - 1$ , while in k-array when  $\tau_H = O(\operatorname{diam}_H)$ ,  $\max_{u \in V_H} \sum_{i=1}^{\tau_H} b_H(u, i) = \Theta(\tau_H^{k+1})$ , and  $\max_{u \in V_H} \sum_{i=1}^{\tau_H} b_H(u, i) = \Theta(N_H \tau_H)$  if  $\tau_H = \omega(\operatorname{diam}_H)$ .

Choosing  $\tau_F = \log N_F$ , if  $\operatorname{diam}_H = \Omega(\sqrt[k+1]{N_F})$  we can use  $\tau_H = \Theta(\sqrt[k+1]{N_F})$ , in fact  $\Theta(\tau_H^{k+1}) < 2N_F - 1$  which gives the lower bound  $T_H = \Omega(\sqrt[k+1]{N_F})$ . On the other hand, if  $\operatorname{diam}_H = o(\sqrt[k+1]{N_F})$  from the inequality  $\Theta(N_H(\tau_H - \operatorname{diam}_H)) < 2N_F - 1 \Rightarrow \tau_H = \Omega\left(\frac{N_F}{N_H}\right)$  which gives  $T_H = \Omega(N_F/N_H)$ . These lower bounds are strict, as we will show presenting a strategy with  $T_H = \Theta(\sqrt[k+1]{N_F})$  when the k-dimensional array has  $\operatorname{diam}_H \ge \sqrt[k+1]{N_F}$ ; when  $\operatorname{diam}_H < \sqrt[k+1]{N_F}$  we exploit the fact that a M-nodes k-dimensional array can emulate a N-nodes k-dimensional array (N > M) with O(N/M) slowdown.

Note that a k-array with diam<sub>G</sub> =  $\omega(N_F^{1/(k+1)})$  would not be useful since

communication among nodes further than  $O(N_F^{1/(k+1)})$  steps would slow down the computation.

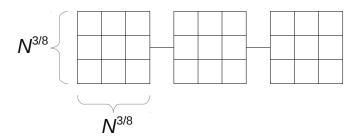

**Proposition 3.** A  $N^{k/(k+1)}$ -nodes k-dimensional array H can compute a N-leaves tree-DAG F in  $O(N^{1/(k+1)})$  steps.

*Proof.* First we show inductively Fact I:

a k-array of  $N^{k/(k+1)}$  nodes can compute a  $N^{k/(k+1)}$ -leaves tree in  $O(N^{1/(k+1)})$  steps,

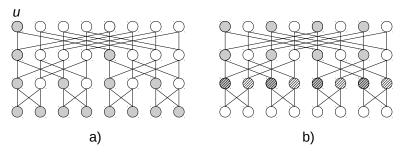

showing next how to extend the result to N-leaves trees. The **base case** for the induction is k = 1. This case considers a  $\sqrt{N}$ -nodes linear array H which compute a  $\sqrt{N}$ -leaves tree F in  $\sqrt{N}-1$  steps with the following strategy S. Node  $x_j$  of H has the jth node of level  $(\log N)/2$  of F. In the first step nodes  $x_{2i}$  and  $x_{2i+1}$  cooperate to produce in  $x_{2i+1}$  the result of the second level of H (they need one communication step); in the second step nodes  $x_{4i+1}$  and  $x_{4i+3}$  cooperate to produce a result of the third level of H (they need two communication step) and so on, until nodes  $i_{\sqrt{N}/2-1}$  and  $i_{\sqrt{N}-1}$  create the output of H in  $i_{\sqrt{N}-1}$ , requiring  $\sqrt{N}/2$  communication steps. The strategy requires  $\sqrt{N}-1$  parallel communication steps and  $(\log N)/2$  parallel computational step.

Note that we can use this strategy to compute a whole N-leaves tree with a  $\sqrt{N}$ -nodes linear array in  $O(\sqrt{N})$ , by assigning nodes  $\{i_{j\sqrt{N}}, \ldots, i_{(j+1)\sqrt{N}-1}\}$  of the  $(\log N)$ -th level of the tree to node  $x_j$  of H, so that it can compute sequentially a certain lower sub-tree  $L_j$  of F with height  $(\log N)/2$  in  $\Theta(\sqrt{N})$  steps (see Figure 2.5) and then applying strategy  $\mathcal{S}$  for the computation of the upper part  $U_0$  of the tree.

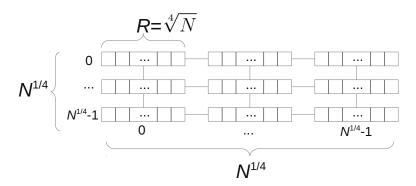

Now consider k > 1. The following **inductive hypothesis** holds: a (k-1)-array with  $N^{\frac{k-1}{k}}$  nodes can compute a  $(N^{\frac{k-1}{k}})$ -leaves tree-DAG in  $\Theta(N^{1/k})$ . Consider a  $N^{k/(k+1)}$ -nodes k-array H formed by nodes  $(i_1, \ldots, i_k), 0 \leq i_n \leq N^{1/(k+1)}$ ,  $\forall n$  computing a  $N^{k/(k+1)}$ -leaves tree. Each node u of H contains a node v of level  $k/(k+1)\log N$  of the tree, in particular node  $(i_1, \ldots, i_k)$  contains node in position  $\sum_{x=1}^k i_x N^{(x-1)/k+1}$ ). H computes F in  $O(N^{1/(k+1)})$  steps in this way: nodes  $(u, i_2, \ldots, i_k), 0 \leq u < N^{1/(k+1)}$  use strategy S to compute a node v of level  $\frac{k-1}{k+1}\log N$  in node  $(N^{1/(k+1)}-1, i_2, \ldots, i_k)$  in  $N^{1/(k+1)}-1$  steps. At this point

Figure 2.5: Division of tree DAG F in lower sub-trees  $L_0, \ldots, L_{\sqrt{N}-1}$  and upper sub-tree  $U_0$ .

sub-array of H composed by nodes  $(N^{1/(k+1)} - 1, i_2, \dots, i_k), 0 \le i_x < N^{1/(k+1)}$  is a k-1-dimensional which has to compute the remaining  $N^{(k-1)/(k+1)}$ -leaves tree. By inductive hypothesis this can be done in  $O(N^{1/(k+1)})$  steps, that jointly with  $(N^{1/(k+1)} - 1)$  steps of first part give a total of  $O(N^{1/(k+1)})$  steps, so that Fact I is proved.

Note that similarly to base case, we can extend this general case to a N-leaves tree by allocating  $N^{1/(k+1)}$  consecutive leaves of F per each node of H; each node computes sequentially a  $(\frac{1}{k+1}\log N)$ -levels sub-tree of F in  $O(N^{1/(k+1)})$  steps, completing the last part of the computation with strategy used to prove Fact I. In the following we will refer to the first part of the process, which reduces the number of leaves of the tree from N to  $N^{k/(k+1)}$  as reduction step of strategy S.

Note that this lower bound defers from Corollary 1, since it has a different meaning. In fact in Corollary 1 network H has to emulate the tree-shaped network G, while now network H is executing a tree-shaped DAG. Note also that executing  $\log N$  steps of the optimal embedding of a tree in a k-dimensional array give  $T_H = \Theta((N \log N)^{1/(k+1)})$ , which does not match the lower bound.

**Application 2.** Consider the execution of an  $N_F$ -input butterfly by a  $N_H$ -nodes k-dimensional array H. We obtain the same lower bound  $T_H = \Omega(\sqrt[k+1]{N_F})$  of the Application 1, since  $B_F(v,i) = 2^{i+1} - 1$ . In fact each output of F is the root of a complete binary tree with  $N_F$  leaves, corresponding to inputs.

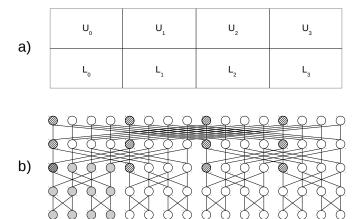

Despite the bigger complexity of the network, we can match the lower bound with a strategy similar to the previous one. Note that a  $N^{k/(k+1)}$ -nodes region

Figure 2.6: Every output of a butterfly is the root for a tree (gray nodes). Nodes of this tree in level  $(\log N)/2$  can be thought as inputs of a  $\sqrt{N}$ -inputs subbutterfly (the shaded nodes).

$\mathcal{R}$  of H, after the reduction step of strategy  $\mathcal{S}$  described in Application 1 (which lasts  $O(N^{1/(k+1)})$ ) has in its nodes inputs of a  $N^{k/(k+1)}$ -inputs butterfly (Figure 2.6 shows the case with  $N_F = 16$  and k = 1).  $\mathcal{R}$  can compute it in  $O(N^{1/(k+1)})$  time using the emulation of the descendant hypercube algorithm for butterfly-like algorithms.

If we consider  $N^{1/(k+1)}$  regions of  $N^{k/(k+1)}$  nodes of H, we can exploit  $N^{1/(k+1)}$  times the previous observation to compute all N outputs in  $O(N^{1/(k+1)})$  parallel steps. Note that this strategy use recomputation.

#### 2.3 Congestion-based lower bound

#### 2.3.1 State of the art

#### The theorem

The second theorem in [KLM+97], requires some more notation. Given an undirected graph  $G = (V_G, E_H)$ , we define the *i*-neighborhood of  $U \subseteq G$ ,  $\mathcal{N}_i(U) = (\bigcup_{u \in U} B_G(u, i)) \setminus U$ , the set of nodes not in U within a distance i from a node in U.

A (R, f(R))-decomposition of a network  $H = (G_H, E_H)$ , is a partition of H in sets  $\mathcal{R}_i$ , such that each  $\mathcal{R}_i$  (region) has [R, 2R] nodes and  $\mathcal{N}_1(\mathcal{R}_i) \leq f(R)$ . Informally, we can partition H in regions of approximatively the same size and with a given upper bound to their bandwidth with the rest of the network.

The (R, f(R))-decomposition is used in the theorem to model H's features. As for G, it is modeled through the function  $z_G(a, \varepsilon, c)$ , where  $a \le c$  are integers in  $[0, |V_G|]$  and  $0 \le \varepsilon < 1$ . To understand the role of function  $z_G$ , consider the following situation: suppose that a region  $\mathcal{R}$  of H has to emulate a set of a nodes of G for a particular time step t of the guest time.  $\mathcal{R}$  has to import or compute predecessors of these nodes before computing them. In particular, if the nodes to compute are  $X_0 \subset V_G$ , it needs  $Z_1 = X_0 \cup \mathcal{N}_1(X_0)$  for guest time t-1. If it imports  $Y_1$  nodes among  $Z_1$ , it will have to compute nodes  $X_1 = X_0 \cup \mathcal{N}_1(X_0) \setminus Y_1$  for time step t-1. We can iteratively define for time step t-i, the set  $X_i = X_{i-1} \cup \mathcal{N}_1(X_{i-1}) \setminus Y_i$  of nodes which  $\mathcal{R}$  will have to compute. Consider i = k such that  $|X_{k-1}| \le c$  and  $|X_k| > c$ , with the constraint  $\sum_{i=0}^k Y_i \le \varepsilon a$  and k as big as possible. Function  $z_G(a, \varepsilon, c)$  is an upper bound to k and it is defined so that it is non-increasing in a. Basically, it takes into account the expansion speed of network G considering how fast a region  $\mathcal{R}$  of H, which has to compute a nodes of a guest time t and only imports  $\varepsilon a$  nodes, must compute c predecessors of a previous guest time step.

**Theorem 3.** Suppose that  $H = (V_H, E_H)$  is an  $N_H$ -nodes host network with an (R, f(R))-decomposition, and that  $G = (V_G, E_G)$  is an  $N_G$ -node guest network. Let

$$\beta = \max \left\{ z_G \left( \frac{N_G}{4}, 0, \frac{3N_G}{4} \right), z_G \left( \frac{3N_GR}{8N_H}, \frac{1}{2}, \frac{N_G}{2} \right) \right\}.$$

Then for any emulation of G by H where  $T_G > 3\beta$ ,

$$I \ge \min\left\{\frac{R}{32\beta f(R)}, \frac{N_H}{192R}\right\}.$$

Again, we refer to [KLM+97] for the proof of the result, while here we just recall the main ideas. Consider the CDAG obtained by the execution of the network G for  $T_G$  time steps; the theorem partitions it in blocks of  $3\beta$  consecutive steps and classifies each of it as *importer block* or *creator block*, depending if it can point out for some region a certain quantity of imported nodes or a certain quantity of nodes computed.

Note that each node  $v \in V_G$  must be pebbled at least once for each  $t \in [1, T_G]$ , in particular in [KLM+97] the first pebble for v for time t created by H is called t-primary pebble of v. For each t, there are  $N_G$  t-primary pebbles and if we order them according the order in which they are created by H, we call the first  $3N_G/4$

t-early pebbles and the last  $3N_G/4$  t-late pebbles ( $N_G/2$  t-primary pebbles are both t-early and t-late).

Focus on a block of the DAG from guest time  $t-3\beta+1$  to t. The (R, f(R))-decomposition of H has at most  $N_H/R$  regions, so that in average every region computes  $p=3N_GR/(4N_H)$  t-early nodes. Consider the following two situations, which characterize an importer block: every region which produces  $s \geq p/2$  t-primary nodes also imports at least s/2 predecessors of them of time steps between  $t-2\beta$  and t-1; a region imports at least  $3N_G/16$  nodes between  $t-2\beta$  and t-1. In both cases we can determine a lower bound for the execution of the block (see [KLM+97]), due to the time needed to import  $3N_G/16$  nodes by the at most  $N_H/R$  regions of H, which have a total bandwidth of  $N_Hf(R)/R$  nodes per step:  $T_{block} \geq 3N_GR/(16N_Hf(R))$ . If half of the blocks are importer, we obtain a lower bound for the execution time of H:

$$T_H \ge \frac{T_G}{2 \cdot 3\beta} \frac{3N_G R}{16N_H f(R)} \qquad \Rightarrow \qquad S \ge \frac{N_G R}{32N_H \beta f(R)}.$$

If the previous hypothesis are not valid, it means that every region imports less than  $3N_G/16$  nodes for guest steps  $t-2\beta$  and t-1 and there is at least a region  $\mathcal{R}$  which produces  $s \geq p/2$  t-primary pebbles but imports less than s/2 for time steps  $t-2\beta$  and t-1. With these limitations, we can show that  $\mathcal{R}$  computes  $\beta N_G/16$  pebbles for the considered block (the block is a creator block). Since  $\mathcal{R}$  has at most 2R nodes, it needs at least  $T_{block} \geq \beta N_G/(32R)$  steps to create the considered nodes. The creation of all these nodes are subsequent to creation of any  $(t-3\beta)$ -primary node, in this way the time required by the region for the creation of its t-primary nodes is disjoint by the time required by other blocks.

If half of the blocks are creator, we have the following lower bound:

$$T_H \ge \frac{T_G}{2 \cdot 3\beta} \frac{\beta N_G}{32R} \qquad \Rightarrow \qquad S \ge \frac{N_G}{192R}.$$

When  $T_G \geq 3\beta$ , the two lower bounds found can be merged in

$$S \ge \min\left\{\frac{N_G R}{32N_H \beta f(R)}, \frac{N_G}{192R}\right\},\tag{2.5}$$

and multiplying both members of inequality by  $N_H/N_G$  we obtain the proposition of the theorem.

In [KLM+97] the theorem is used to derive several results regarding the possibility of obtaining work preserving emulations of specific classes of networks by mean of other classes. For example, authors prove that k-arrays and butterflies can not perform work preserving emulation of expander networks, while a work preserving emulation of a butterfly G by a k-array H has at least slowdown  $2^{\Omega(N_H^{1/k})}$ .

Finally, they prove that a work-preserving emulation of a k-dimensional array G by a j-dimensional array H (j < k) has slowdown at least  $\Omega(N_H^{(k-j)/k})$ , so that such an emulation can not be work preserving ( $S = O(N_G/N_H)$ ) if the j-dimensional array has more than  $O(N_G^{j/k})$  nodes.

#### 2.3.2 Analysis and Critique

Focus again on the emulation of an  $N_G$ -nodes k-dimensional array G by an  $N_H$ -nodes j-dimensional array H (j < k). In order to apply Theorem 3, we can obtain  $\beta = O(N_G^{1/k})$  and  $f(R) = R^{(j-1)/j}$ . Replacing them in Equation 2.5, slowdown is

$$S \ge \min \left\{ \frac{N_G^{(k-1)/k} R^{1/j}}{32N_H}, \frac{N_G}{192R} \right\};$$

in particular, lower bounds are both valid when

$$\frac{N_G^{(k-1)/k} R^{1/j}}{32N_H} = \frac{N_G}{192R} \qquad \Rightarrow \qquad R = \left(\frac{N_G^{\frac{1}{k}} N_H}{6}\right)^{\frac{j}{j+1}},$$

which holds to

$$S = \Omega \left( \frac{N_G}{\left(N_G^{\frac{1}{k}} N_H\right)^{\frac{j}{j+1}}} \right). \tag{2.6}$$

Figure 2.3 represents the fact that for  $N_H = O(N_H^{\frac{1}{k}})$  the lower bound is matched by an embedding and that Theorem 3 gives a tighter lower bound respect to 1 when  $N_G > N_H$  (we can obtain this by comparing the lower bound in Equation

2.6 and those in previous subsection).

This fact is a counter-example which proves the following proposition.

**Proposition 4.** Lower bounds obtained by Theorem 3 can be tighter than lower bounds obtained by Theorem 1.

Now consider the emulation of a  $N_G$ -nodes tree G by a  $N_H$ -nodes k-dimensional array H. From the previous subsection we know that the optimal emulation slow-down is

$$S = \begin{cases} \Theta\left(\frac{N_G}{N_H}\right) & \text{if } N_H = o((N_G \log N_G)^{1/(k+1)}) \\ \Theta\left(\left(\frac{N_G}{\log^k N_G}\right)^{\frac{1}{k+1}}\right) & \text{if } N_H = \Omega((N_G \log N_G)^{1/(k+1)}) \end{cases}.$$

Parameter f(R) for Theorem 3 still is  $R^{(k-1)/k}$ , while  $\beta$  is more tricky than in previous example. In fact  $z_G\left(\frac{N_G}{4},0,\frac{3N_G}{4}\right) = O(\log N_G)$ , while  $z_G\left(\frac{3N_GR}{8N_H},\frac{1}{2},\frac{N_G}{2}\right) = O(N_GR/N_H + \log N_G)$ , using a strategy to maximize  $\beta$  that targets a subtree as starting set and uses all importations available in its root.

Since depending on value of R,  $1 \le R \le N_H/2$ , the term  $N_G R/N_H$  assumes values in  $N_G/N_H \le N_G R/N_H \le N_G/2$ , the inequality  $N_G R/N_H = \omega(\log N_G)$  holds for every  $N_H = o(N_G/\log N_G)$ . In this case  $\beta = O(N_G R/N_H)$  and Equation 2.5 becomes

$$S \ge \min \left\{ \frac{N_G R}{32N_H \frac{N_G R}{N_H} f(R)}, \frac{N_G}{192R} \right\} = \min \left\{ \frac{1}{32f(R)}, \frac{N_G}{192R} \right\},$$

and since in a connected network  $f(R) = \Omega(1)$ , we obtain

$$S = \Omega(1)$$

,

which is trivial. In this case the lower bound for the emulation of a tree by a k-dimensional array obtained by Theorem 1 is tight, while that obtained by Theorem 3 is not, so the following proposition is true.

**Proposition 5.** Lower bounds obtained by Theorem 1 can be tighter than lower bounds obtained by Theorem 3.

Now, we consider which elements make lower bounds of Theorem 3 weak.

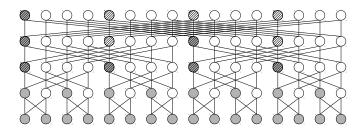

**Example 1.** Consider the emulation of a  $\sqrt{N} \times \sqrt{N}$  2-dimensional mesh G by an N-nodes linear array. Theorem 3 gives  $S = \Omega(N^{1/4})$  (obtained when  $R = \Theta(N^{3/4})$ ), while the strict lower bound is  $N = \Omega(N^{1/2})$ , by Theorem 4. A (R, f(R))-decomposition of a linear array has  $f(R) = O(1), \forall R$ . If we con-

Figure 2.7: Consider an N-nodes "linear array of meshes" network: it consists of  $N^{1/4}$  meshes  $N^{3/8} \times N^{3/8}$  disposed as in picture. When  $R = N^{3/4}$ , the (R, f(R))-decomposition of this network and that of a N-nodes linear array are the same.

sider the N-nodes network A in Figure 2.7, it has the same parameters of the  $(N^{3/4}, f(N^{3/4}))$ -decomposition of a linear array. Unlike linear array, it is easy to match the lower bound of Theorem 3 emulating G by means of A. In fact, we need just to consider one region, which has  $N^{3/4}$  nodes, and perform the well-known work-preserving emulation of an N-nodes mesh on a  $N^{3/4}$ -nodes mesh.