Sede Amministrativa: Università degli Studi di Padova Sede Consorziata: Università degli Studi di Trieste

Dipartimento di Ingegneria Elettrica

## SCUOLA DI DOTTORATO DI RICERCA IN : INGEGNERIA INDUSTRIALE INDIRIZZO: INGEGNERIA ELETTROTECNICA CICLO XXIV

## REAL-TIME APPLICATIONS FOR ELECTRIC POWER GENERATION AND CONTROL

Direttore della Scuola: Ch.mo Prof. Paolo Bariani

Coordinatore d'indirizzo: Ch.mo Prof. Giovanni Martinelli

Supervisore: Ch.mo Prof. Giorgio Sulligoi

Co-tutor: Ing. Vittorio Arcidiacono

Dottorando: Massimiliano Chiandone

31 Gennaio 2012

ii

To Sabina, Giovanni and Elisabetta.

ii

## Abstract

### Sommario.

Il controllo dei sistemi elettrici di potenza ha per scopo la fornitura di energia agli utilizzatori (carichi) garantendo una adeguata qualità malgrado le continue variazioni di topologia, le variazioni nella generazione e le fluttuazioni dei carichi che avvengono nel sistema stesso.

Questa tesi riguarda il problema della regolazione di uno tra i principali parametri che determina la qualità del servizio fornito: la tensione a cui l'energia viene fornita.

Una eventuale definizione di adeguata qualità è fuori dagli scopi del lavoro.

Molti dispositivi atti a regolare il valore della tensione in diverse parti del sistema sono stati sviluppati nel corso degli anni. In questa tesi vengono approfonditi alcuni aspetti dei dispositivi di regolazione della tensione che agiscono attraverso il controllo della potenza reattiva erogata dai generatori.

La regolazione della tensione nei sistemi elettrici è tradizionalmente suddivisa almeno in regolazione primaria, che avviene agendo sulla tensione di eccitazione dei singoli generatori, e regolazione secondaria, con il controllo della potenza reattiva di intere centrali. Entrambe, in ultima analisi, vengono attuate variando la tensione di eccitazione dei generatori sincroni.

In questo lavoro viene presentata una unica piattaforma hardware e software che ha permesso di implementare due dispositivi di controllo digitale:

- un sistema di controllo dell'eccitazione per la regolazione primaria della tensione nei generatori sincroni;

- un sistema di controllo della potenza reattiva per la regolazione secondaria della tensione nelle grandi centrali elettriche. Questo dispositivo è presente nel codice di rete italiano dal 2003 e viene chiamato SART (Sistema Automatico di Regolazione della Tensione).

Questi regolatori di tensione sono nati storicamente come apparati analogici e sono poi stati implementati come sistemi digitali con varie tecnologie. In questa tesi si tratta dell'implementazione di tali sistemi come controlli digitali utilizzando microprocessori e software di elaborazione matematica di uso generale equipaggiati con sistemi operativi di uso generale ma con caratteristiche real-time.

Una tecnica emergente per la prototipizzazione rapida di sistemi di controllo prevede l'utilizzo di strumenti di simulazione di alto livello in cui progettare e simulare il funzionamento dell'impianto e del controllo generando automaticamente il codice del controllo. In questa tesi è presentata e descritta l'applicazione della citata tecnica nell'ambito della produzione e regolazione dell'energia elettrica. I due sistemi di controllo oggetto di questa tesi sono progettati e simulati con un linguaggio di alto livello ed implementati con l'utilizzo di un sistema operativo Linux modificato (RTAI) per avere prestazioni real-time.

In questo lavoro vengono anche presentati i dati sperimentali di alcune sessioni di collaudo dell'apparato SART.

In fase finale è stata indagata la possibilità di utilizzare la piattaforma per sviluppare analoghi dispositivi di regolazione da applicare alla rete di distribuzione. La crescita della generazione di piccola e media taglia all'interno delle reti di distribuzione avvenuta nell'ultimo decennio ed ancora in corso, pone nuove problematiche per la regolazione di tensione. Viene quindi proposto un controllo della tensione per reti di distribuzione, in presenza di generazione distribuita, in cui dispositivi analoghi a quelli presentati per la rete di trasmissione possono trovare utile applicazione.

### Summary.

The aim of an electric power control system is to supply electric energy to final users ensuring an adequate quality regardless to the constant changes in network topology, the variations in generation and the load fluctuations within the system itself.

This dissertation deals with the control aspects of one of the main parameters involved in the quality of the service provided: the voltage value energy is supplied.

It is herewith not intended to look at the definition of adequate quality of energy.

Over the years several devices have been developed to control the voltage value in different parts of the power system. This work aims at studying in deep some of the aspects of the voltage control systems regulating the reactive power absorbed and injected into the network by generators.

Voltage regulation in electrical systems is traditionally divided at primary level by operating on the reactive power of the single generator and by controlling the reactive power of entire power stations at secondary level. Ultimately these regulations are both carried out by varying the current or the excitation voltage in synchronous generators.

This work presents a single hardware and software platform enabling the implementation of two digitally controlled devices:

- a control system controlling the excitation in synchronous generators;

- a system controlling the reactive power of the secondary voltage control in large power plants. This device is prescribed in the Italian network code since 2003 and is called SART (Automatic System for Voltage Regulation).

These voltage regulators were historically born as analog devices and were subsequently implemented as digital controls using various technologies. The central topic of this dissertation is the implementation of the above-mentioned devices as digital control systems using microprocessors and general purpose computing systems, fitted out with operating systems for general use but with real-time characteristics.

An emerging technique to quickly prototype a control system implies the utilization of high level simulation tools to design and simulate the plant to be controlled and automatically generate a control code. This work presents in detail the above-mentioned technique in the production and regulation of electric energy. The two control systems taken into consideration are designed and simulated using a high-level language and implemented with a modified Linux operating system (RTAI) in order to offer real-time performance. Furthermore, the experimental data of some SART device commissioning sessions are also included.

In conclusion, the possibility of using the same platform for the development of similar voltage control devices to apply in the distribution network was investigated. The growth of little and medium-sized generation units, within the distribution network, which has taken place in the last decade, has introduced new issues in voltage regulation. For this reason a new control strategy was suggested for voltage controlling in distribution networks, where the generation is spread and control devices similar to the ones presented for the transmission network can be applied.

## Acknowledgements

Un sentito ringraziamento al mio tutor prof. Giorgio Sulligoi, per la fiducia che ha riposto in me e nelle mie competenze, spero sia stata ripagata dal lavoro svolto. Lo ringrazio per avermi spronato con continuità e con sempre nuovi obiettivi.

E' doveroso anche ringraziare l'Ing. Vittorio Arcidiacono, e' stata una grande fortuna ed un immenso onore poter lavorare al suo fianco.

Un grazie ai sig.ri (Vinc)Enzo Bordonaro, Fabi(ett)o Danini, Roberto Mariani, Fabio(ne) Veschi e Giuseppe Vit per la collaborazione e grande disponibilita' sempre dimostratami.

Un grande aiuto mi è arrivato dall'amico Marino, anche nella veste del prof. Miculan: il suo invito a cogliere l'opportunità offertami è stato decisivo.

A Massimo, Edi, Silvia e Daniela un abbraccio per la pazienza e le correzioni. Un grazie anche a Daniele per la lettura.

Un riconoscente ringraziamento al prof. Furio Honsell per avermi formato prima ed avermi permesso ora di affrancarmi temporaneamente dalla mia principale attività per questa sfida.

Many thanks to Mrs. Elisabetta Salvador and Miss. Sabina Damiani for all the corrections to the manuscript.

vi

# Contents

| Li       | st of | Figures                                       | ci |

|----------|-------|-----------------------------------------------|----|

| Li       | st of | Tables x                                      | v  |

| G        | lossa | ry xvi                                        | ii |

| 1        | Intr  | oduction                                      | 1  |

|          | 1.1   | Objectives                                    | 1  |

|          | 1.2   | Outline of the thesis                         | 1  |

| <b>2</b> | Vol   | tage Control                                  | 5  |

|          | 2.1   | Introduction                                  | 5  |

|          | 2.2   | Complexity of power systems                   | 5  |

|          | 2.3   | Voltage control                               | 8  |

|          |       | 2.3.1 Primary voltage control                 | 0  |

|          |       | 2.3.2 Secondary voltage control               | 4  |

|          |       | 2.3.3 Voltage control in distribution network | 7  |

|          | 2.4   | Conclusions                                   | 9  |

| 3        | Rea   | l-time operating systems 2                    | 1  |

|          | 3.1   | Introduction                                  | 1  |

|          | 3.2   | Real-time control systems                     | 1  |

|          |       | 3.2.1 Operating systems                       | 3  |

|          |       | 3.2.2 Linux                                   | 4  |

|          |       | 3.2.3 Real Time Operating Systems             | 5  |

|          | 3.3   | RTAI                                          | 7  |

|          |       | 3.3.1 Why Linux is not real-time              | 7  |

|          | 3.4   | Real-time performance                         | 0  |

### CONTENTS

|          |     | 3.4.1 Jitter scheduling measurements |

|----------|-----|--------------------------------------|

|          |     | 3.4.2 Results analysis               |

|          |     | 3.4.3 Reading sinusoidal waves       |

|          | 3.5 | RTAI applications                    |

|          | 3.6 | Controller design with RTAI          |

|          | 3.7 | Conclusions                          |

| 4        | Con | nmunications 43                      |

|          | 4.1 | Introduction                         |

|          | 4.2 | Communication Capability             |

|          | 4.3 | Communication system architectures   |

|          |     | 4.3.1 Industrial network protocols   |

|          |     | 4.3.2 The Ethernet protocol          |

|          |     | 4.3.3 Real-time Ethernet             |

|          |     | 4.3.4 Ethernet in controls           |

|          |     | 4.3.5 Performance                    |

|          | 4.4 | Communication architecture           |

|          |     | 4.4.1 Communication task             |

|          |     | 4.4.2 Round-trip measurement         |

|          | 4.5 | Redundancy in communications         |

|          | 4.6 | Industrial protocols                 |

|          |     | 4.6.1 OPC-DA                         |

|          |     | 4.6.2 Modbus TCP                     |

|          | 4.7 | Data recording                       |

|          | 4.8 | Conclusions                          |

| <b>5</b> | Exc | itation control system 61            |

|          | 5.1 | Introduction                         |

|          | 5.2 | ECS description                      |

|          | 5.3 | ECS logic scheme                     |

|          |     | 5.3.0.1 3-Phase Input Processing     |

|          |     | 5.3.0.2 Finite State Machine         |

|          |     | 5.3.0.3 Compound                     |

|          |     | 5.3.0.4 PSS                          |

### CONTENTS

|   |     | 5.3.0.5 UEL and OEL                            | 68  |

|---|-----|------------------------------------------------|-----|

|   |     | 5.3.0.6 Var/PF Control                         | 68  |

|   |     | 5.3.0.7 AVR Reference                          | 69  |

|   |     | 5.3.0.8 Manual Reference                       | 69  |

|   |     | 5.3.0.9 AVR                                    | 69  |

|   |     | 5.3.0.10 Reference Follower                    | 69  |

|   |     | 5.3.0.11 Simulator $\ldots$                    | 69  |

|   | 5.4 | Redundancy                                     | 70  |

|   | 5.5 | Conclusions                                    | 72  |

| 6 | Aut | omatic voltage and reactive power regulator    | 73  |

|   | 6.1 | Introduction                                   | 73  |

|   | 6.2 | Hierarchical voltage control                   | 73  |

|   | 6.3 | Coordinated Automatic Voltage Control in Italy | 74  |

|   | 6.4 | SART Description                               | 76  |

|   |     | 6.4.1 SART Central Unit                        | 76  |

|   |     | 6.4.2 Regulator block                          | 77  |

|   |     | 6.4.2.1 Busbar voltage control mode            | 82  |

|   |     | 6.4.3 Simulator block                          | 83  |

|   |     | 6.4.4 Finite state machine block               | 84  |

|   |     | 6.4.5 Human Machine Interface                  | 84  |

|   |     | 6.4.6 Input - output block                     | 85  |

|   |     | 6.4.6.1 Cabled I/O                             | 86  |

|   |     | 6.4.6.2 Internal communications                | 86  |

|   |     | 6.4.6.3 SCADA and DCS communications           | 87  |

|   | 6.5 | Experimental data                              | 90  |

|   |     | 6.5.1 Case 1                                   | 90  |

|   |     | 6.5.2 Case 2                                   | 96  |

|   |     | 6.5.3 Case 3                                   | .00 |

|   |     | 6.5.4 Case 4                                   | .02 |

|   | 6.6 | Conclusions                                    | .02 |

### CONTENTS

| 7  | Dist  | tribute                        | d Generation                                                                                             | 105 |  |

|----|-------|--------------------------------|----------------------------------------------------------------------------------------------------------|-----|--|

|    | 7.1   | Introd                         | uction                                                                                                   | 105 |  |

|    | 7.2   | 2 Distributed energy resources |                                                                                                          |     |  |

|    | 7.3   | Voltag                         | e rise                                                                                                   | 108 |  |

|    | 7.4   | Voltag                         | e rise mitigation based on sensitivity matrices $\ldots \ldots \ldots \ldots \ldots \ldots$              | 112 |  |

|    |       | 7.4.1                          | Case full matrix $[A]$                                                                                   | 114 |  |

|    |       | 7.4.2                          | Case diagonal matrix $[A]$                                                                               | 115 |  |

|    |       |                                | 7.4.2.1 Term $P^T A C^T B P$                                                                             | 116 |  |

|    |       |                                | 7.4.2.2 Term $P^T B^T CAP$                                                                               | 117 |  |

|    |       | 7.4.3                          | Term $P^T A C^T C A P \dots$                                                                             | 117 |  |

|    | 7.5   | Simula                         | ations                                                                                                   | 118 |  |

|    |       | 7.5.1                          | Simulation software                                                                                      | 118 |  |

|    |       | 7.5.2                          | Network test                                                                                             | 119 |  |

|    |       |                                | 7.5.2.1 Diagonal solution $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 123 |  |

|    |       | 7.5.3                          | Choosing the pilot nodes                                                                                 | 124 |  |

|    |       | 7.5.4                          | IEEE-37 bus test network                                                                                 | 126 |  |

|    | 7.6   | Voltag                         | e Control Systems                                                                                        | 130 |  |

|    | 7.7   | Conclu                         | usions                                                                                                   | 131 |  |

| 8  | Con   | clusio                         | n                                                                                                        | 133 |  |

| Bi | bliog | graphy                         |                                                                                                          | 135 |  |

# List of Figures

| 2.1  | AC line                       | 8  |

|------|-------------------------------|----|

| 2.2  | Phasor diagram                | 10 |

| 2.3  | Primary Control               | 11 |

| 2.4  | ECS                           | 12 |

| 2.5  | ECS diagram                   | 12 |

| 2.6  | SVR diagram                   | 16 |

| 2.7  | RPR diagram                   | 17 |

|      |                               |    |

| 3.1  | Control                       |    |

| 3.2  | RTAI                          |    |

| 3.3  | Scheduling jitter             | 32 |

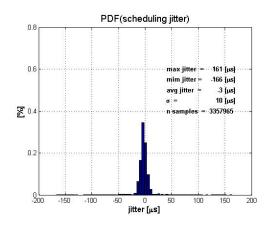

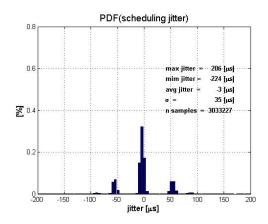

| 3.4  | Scheduling jitter pdf 11 I/O  | 33 |

| 3.5  | Scheduling jitter pdf 50 I/O  | 34 |

| 3.6  | Scheduling jitter pdf 100 I/O | 34 |

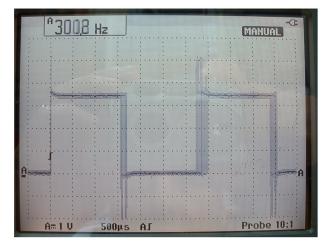

| 3.7  | Square wave model             | 34 |

| 3.8  | Square wave output            | 35 |

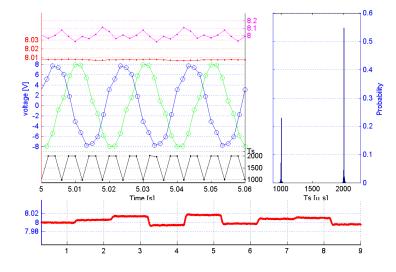

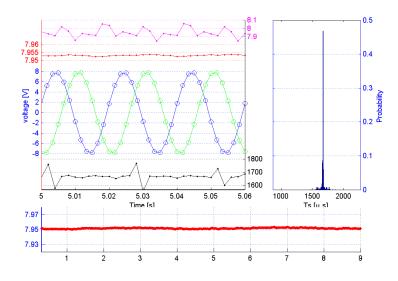

| 3.9  | Three phase voltages          | 37 |

| 3.10 | Three phase voltages          | 37 |

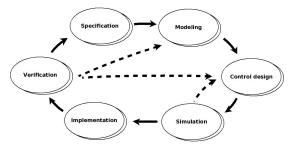

| 3.11 | Model based design            | 38 |

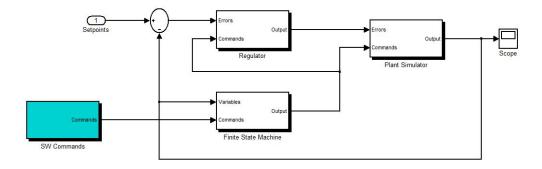

| 3.12 | Control system model          | 40 |

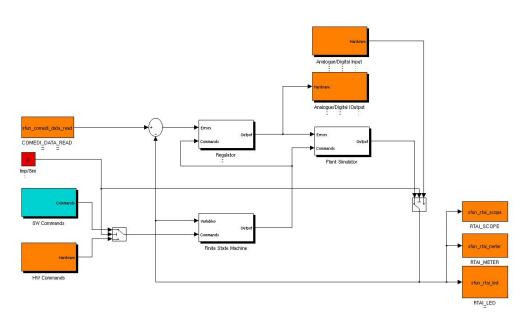

| 3.13 | Control system design         | 41 |

|      |                               |    |

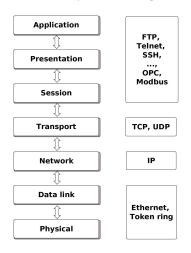

| 4.1  | TCP/IP and OSI model          |    |

| 4.2  | Real-time communication       |    |

| 4.3  | Roundtrip measurement         | 54 |

### LIST OF FIGURES

| 4.4        | XML-DA protocol                                                                                          | 56       |

|------------|----------------------------------------------------------------------------------------------------------|----------|

| 4.5        | OPC DA protocol                                                                                          | 57       |

| 4.6        | Modbus communication                                                                                     | 58       |

| 5.1        | ECS scheme                                                                                               | 63       |

| 5.2        | ECS functional scheme                                                                                    | 64       |

| 5.3        | ECS description                                                                                          | 65       |

| 5.4        | Drop compensation                                                                                        | 66       |

| 5.5        | Common busbar                                                                                            | 67       |

| 5.6        | Droop compensation                                                                                       | 67       |

| 5.7        | PSS                                                                                                      | 68       |

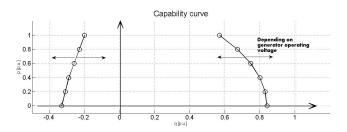

| 5.8        | Capability curve input                                                                                   | 68       |

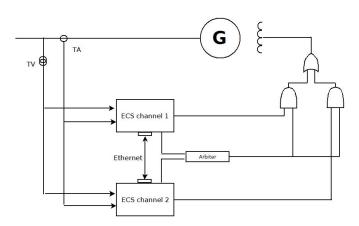

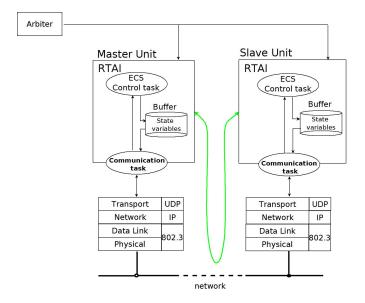

| 5.9        | Redundancy principle                                                                                     | 71       |

| 5.10       | Two channel communication system $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 71       |

| 6.1        | SVR                                                                                                      | 75       |

| 6.2        | SART Central Unit.                                                                                       | 73<br>78 |

| 0.2<br>6.3 | Regulator                                                                                                |          |

| 0.3<br>6.4 | Capability curve                                                                                         | 78<br>79 |

| 6.5        | Dynamic decoupling matrix                                                                                |          |

| 6.8        | Network model   Network model                                                                            |          |

| 0.8<br>6.9 |                                                                                                          |          |

|            | HMI                                                                                                      |          |

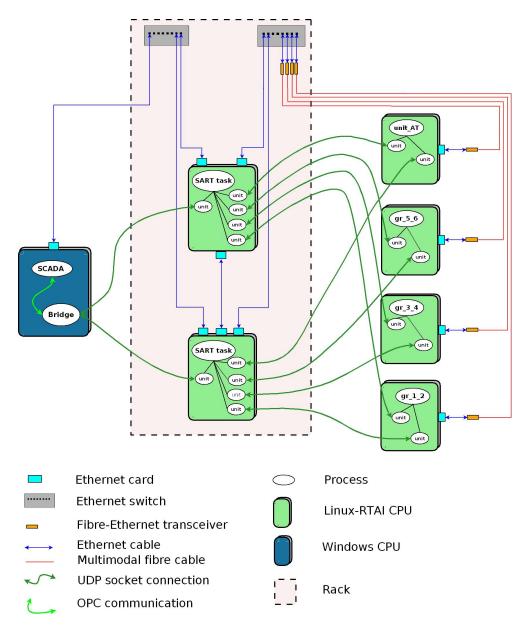

|            | Communications                                                                                           |          |

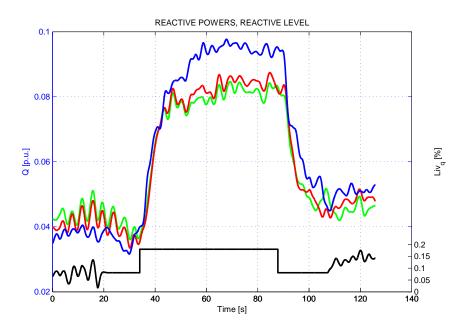

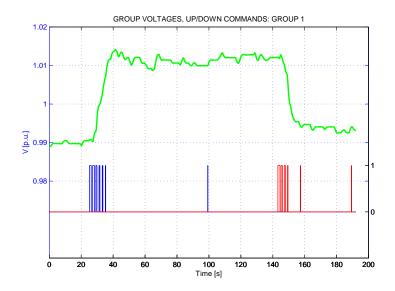

|            | Case 1 - Step 1                                                                                          |          |

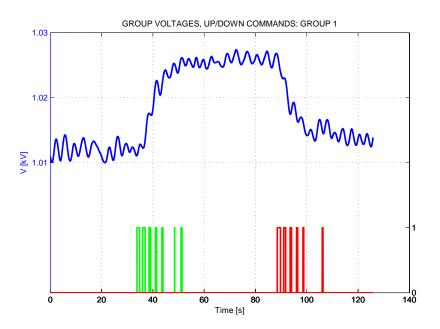

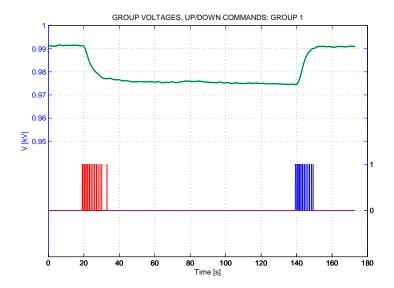

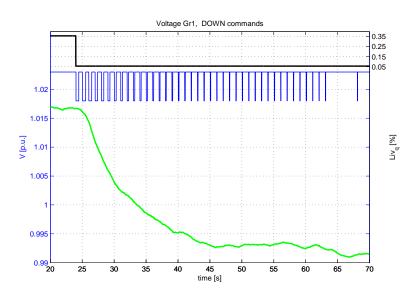

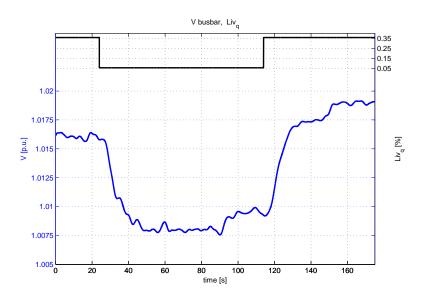

|            | Case 1 - Voltage GR1                                                                                     |          |

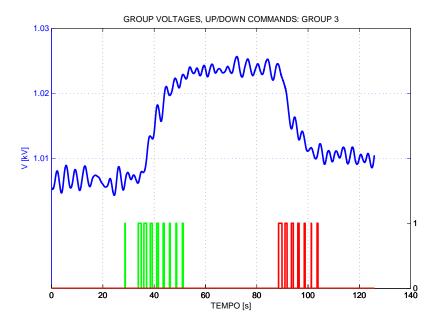

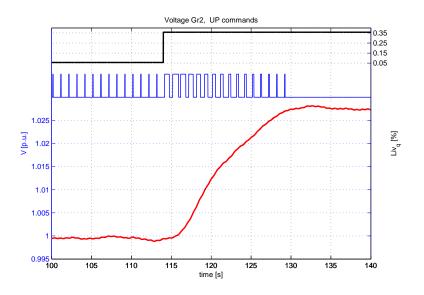

|            | Case 1 - Voltage GR3                                                                                     |          |

|            | Case 1 - Step 2                                                                                          | 92       |

|            | Case 1 - Two Steps                                                                                       | 94       |

|            | Case 1 - Three Steps                                                                                     | 95       |

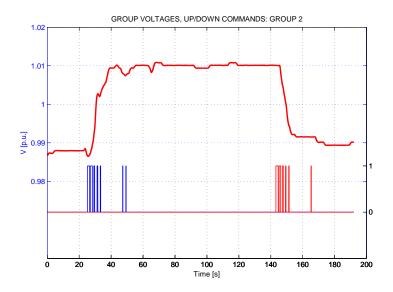

|            | Case2 - Step -20                                                                                         | 96       |

|            | Case2 - Step -0.2 Group 1                                                                                | 97       |

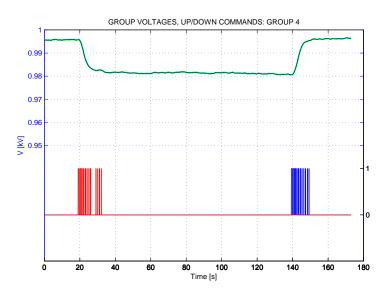

|            | Case2 - Step -0.2 Group 4                                                                                | 97       |

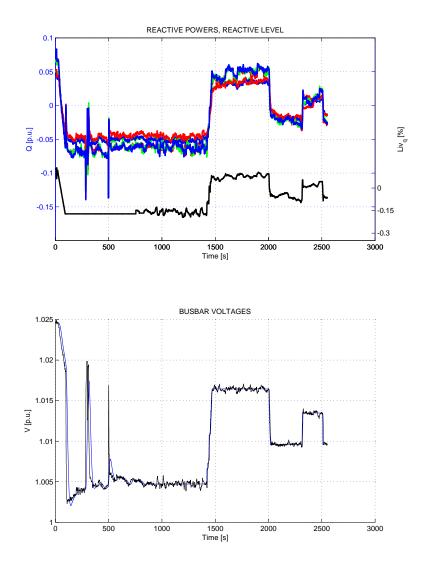

|            | Case2 - Livq RTS transition                                                                              | 99       |

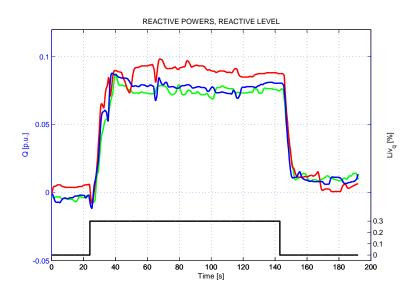

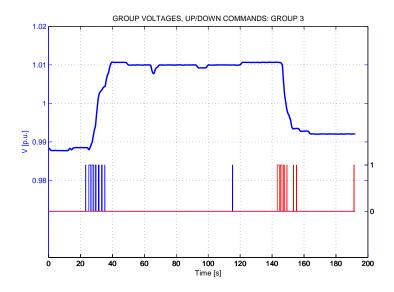

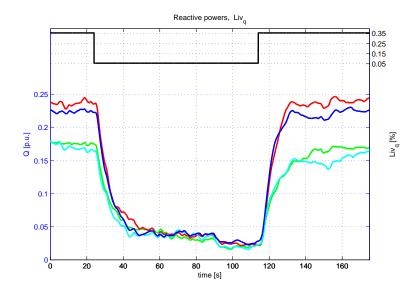

| 6.21       | Case3 - Reactive power response                                                                          | 100      |

### LIST OF FIGURES

| 6.22 | Case3 - Voltage GR1             |

|------|---------------------------------|

| 6.23 | Case3 - Voltage GR2             |

| 6.24 | Case3 - Voltage GR3             |

| 6.25 | Case4 - Reactive power response |

| 6.26 | Case4 - Voltage GR1             |

| 6.27 | Case4 - Voltage GR2             |

| 6.28 | Case4 - Busbar voltage          |

|      |                                 |

| 7.2  | Voltage drop                    |

| 7.3  | Voltage rise                    |

| 7.4  | Voltage drop                    |

| 7.5  | Voltage rise                    |

| 7.6  | Voltage profile with OLTC       |

| 7.7  | Coordinated control             |

| 7.8  | Local control                   |

| 7.9  | Network test                    |

| 7.10 | Network model                   |

| 7.11 | Voltage profile                 |

| 7.14 | IEEE 37 nodes                   |

# List of Tables

| 2.1  | Line cable data                                                                      |

|------|--------------------------------------------------------------------------------------|

| 7.1  | MV test network lines data                                                           |

| 7.2  | Table MV test network generator data    121                                          |

| 7.3  | Active and reactive power with the proposed control                                  |

| 7.4  | Active and reactive power with the proposed control and diagonal solution 123 $$     |

| 7.5  | Sensitivity of nodes to generators active power injection                            |

| 7.6  | MV test network lines data                                                           |

| 7.7  | Table IEEE 37 nodes MV test network generator data.    128                           |

| 7.8  | MV IEEE 37 bus test network load data                                                |

| 7.9  | Table IEEE 37 nodes MV test network reactive powers imposed with diagonal [A].129 $$ |

| 7.10 | Table IEEE 37 nodes MV test network reactive powers imposed with full [A] 129 $$     |

|      |                                                                                      |

# Glossary

|        |                                                      | OPC UA | • OPC Unified Architecture              |

|--------|------------------------------------------------------|--------|-----------------------------------------|

| ADEOS  | Adaptive Domain Environment for Op-                  | OSI    | International Standard Organization     |

|        | erating Systems                                      | PCU    | Power Control Unit                      |

| API    | Application Programming Interface                    | PLC    | Programmable Logic Control              |

| AVR    | Automatic Voltage Regulator                          | POSIX  | Portable Operating System Interface for |

| BVR    | Busbar Voltage Regulator                             |        | Unix                                    |

| COTS   | Commercial-Off-The-Shelf                             | PSS    | Power System Stabilizer                 |

| CSMA/C | $\mathbf{A}$ Carrier sense multiple access with col- | PVR    | Primary Voltage Regulation              |

|        | lision detect                                        | RPL    | Reactive Power Level                    |

| DCOM   | Distribuited Component Object Model                  | RTAI   | Real Time Application Interface         |

| DCS    | Distributed Control System                           | RTOS   | Real Time Operating System              |

| DG     | Distributed Generation                               | RVR    | Regional Voltage Regulator              |

| DMS    | Distribution Management Systems                      | SCADA  | Supervisor and Control and Data Acqui-  |

| DSP    | Digital Signal Processor                             |        | sition                                  |

| ECS    | Excitation Control System                            | SVR    | Secondary Voltage Regulation            |

| EHV    | Extra High Voltage                                   | TCP    | Transmission Control Protocol           |

| EMS    | Energy Management System                             | TDMA   | Time Division Multiple Access           |

| GPP    | General Purpose Processor                            | TVR    | Tertiary Voltage Regulation             |

| GRPR   | Generator Reactive Power Regulators                  | UDP    | User Datagram Protocol                  |

| HMI    | human-machine interface                              | UEL    | Under Excitation Limiter                |

| HRT    | Hard Real Time                                       | WCET   | Worst Case Execution Time               |

ISO

LAN

MMU

OEL

OLTC

OPC

OPC

Independent System Operator

Memory Management Unit

Over Excitation Limiter

On-Line Tap Changers

OLE for Process Control

Open Productivity and Connectivity

Local Area Networks

1

# Introduction

### 1.1 Objectives

This thesis concerns the use of real-time operating systems aimed at developing control devices to be used in power systems to control the voltage. The real-time performances of some real time operating systems have been compared with the dynamics requested by some voltage control devices used in power systems. Two different control devices have been developed. Simulation and extended experimental results obtained in real commissioning tests are shown. The possibility to use this kind of hardware and software platforms for developing control devices of the new grid (the so called Smart-Grid) is outlined.

### 1.2 Outline of the thesis

Electrical power systems are often cited as the most complex systems ever made by human being. The topology of an electric power system is continuously affected by changes due to maintenance, developments and also automatic operations. Also generation and loads, that should be continuously and rapidly balanced, fluctuate partially uncontrolled. The quality of the service strongly depends on some quantities (e.g. voltage and frequency) of the energy supplied to the customers while the power system is subject to a wide range of electromechanical and electromagnetic phenomena.

The voltage at fundamental frequency is a particularly important issue because any deviation from the nominal voltage to the supplied consumers can deteriorate their performance and continuity. Several electromechanical and electronic equipments require the voltage to be kept within a small range of variability around a nominal value. The complexity is traditionally

### 1. INTRODUCTION

managed with a decomposition approach. Therefore the voltage problem is split on a geographical criteria separating the high voltage network from medium and low voltage networks and subdividing the high voltages network itself in different areas weakly coupled. The voltage problem is also decomposed with a time-horizon criteria according with the dynamics of the subsystem under consideration.

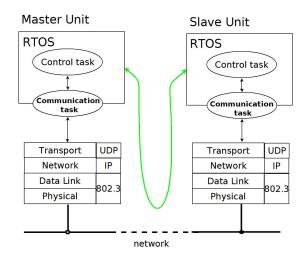

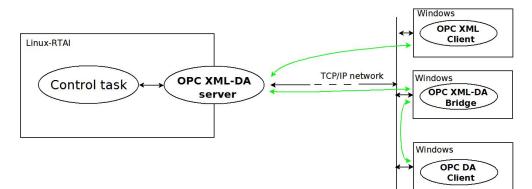

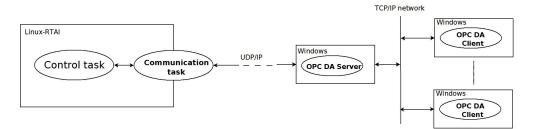

In chapter 2 the problem of voltage control is presented. The aim of this chapter is to describe the main characteristics of the control problems in which the developed devices have been applied. The focus will be on the voltage control through the reactive power control. In transmission system it can be shown how the voltage amplitudes strongly depend on the reactive power flow and are weakly coupled to active power flows. Different levels of control will be presented together with their dynamic characteristics: a primary voltage control through generators excitation control systems characterized by a dominant time constant (closed loop) of about 0.5-1 s, the reactive power control loops of the power stations characterized by a dominant time constant (closed loop) of about 5-10 s and grid pilot nodes voltages control loops characterized by a dominant time constant time constant (closed loop) of about 50 s or higher.

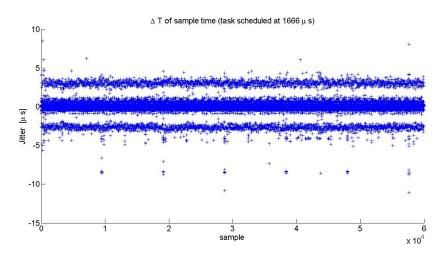

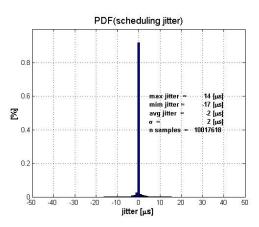

These controls require an ever growing set of functionalities and flexibility to be integrated in complex control centers and therefore an emerging development strategy is to use general purposes processors endowed with a complete operating system with real-time performance. In chapter 3 a review on RTOS (Real Time Operating System) proceed specific performance analysis of RTAI (a Linux based RTOS) and comparisons among RTAI and other commonly used RTOSs. Comparisons and performance analysis are focused on applications, therefore the main parameter considered is the jitter of scheduling time. One of the advantages in using a complete RTOS concerns the communication features offered by these OSs. Some consideration on communication are outlined in chapter 4.

The proposed platform based on RTAI was used in order to develop two real-time control devices: a control excitation system for synchronous generators is presented in chapter 5 and a reactive control system used in secondary voltage control is described in chapter 6.

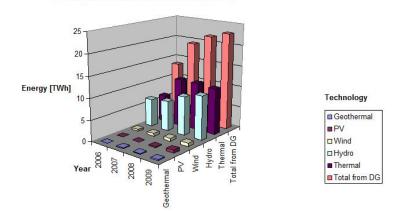

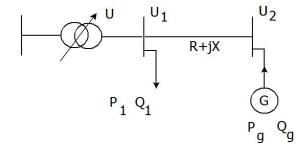

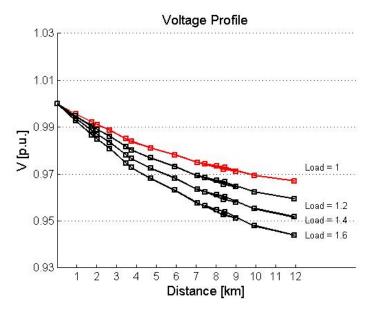

These two applications concern mainly the transmission system but new issue is arising in distribution systems: the connection of small size generators mainly to the medium and low voltage networks. The so called embedded or distributed generation introduces new challenges in voltage control. In chapter 7 the problem of voltage rise in distribution network in presence of distributed generation is reviewed and a new control strategy is presented and simulation results are shown. The implementation of this strategy is outlined with a kind of devices very similar to those previously presented and therefore the technology presented is shown suitable for the architecture of the new grid.

### 1. INTRODUCTION

# Voltage Control

## 2.1 Introduction

$\mathbf{2}$

Some aspects of power systems complexity and the decomposition of the control problem typically applied are introduced. The control issues treated in this work are then summarized. Requirements for the control devices bandwidth are drawn.

## 2.2 Complexity of power systems

An electric power system normally encompasses a very high number of machinery and devices and hence of physical quantities. It is essentially devoted to produce energy, transfer the produced energy near to consumers and distribute it to each one of the different users (called loads) at any moment and with the required quality (e.g. guaranteed frequency and voltage)[1].

This rough description has a precise counterpart in the physical structure of power systems: there is the presence of central stations devoted to the conversion of some kind of energy in electrical energy, an high voltage grid to transmit the energy over long distances and a distribution network using lower voltage levels to supply energy to the final users (e.g. private houses, stores and any kind of electrical device).

The overall network (comprising transmission and distribution grids) is meshed and continuously subject to modifications in topology (due to faults, improvements, maintanance), production (insertion and disconnection of generators) and consumes (fluctuation of the loads), therefore the operating point is continuously changing.

The system is not linear: although the grid can be represented by a linear system relating

current injected into the nodes and voltages of the nodes [2]:

$$[\bar{I}] = [\bar{Y}][\bar{V}] \tag{2.1}$$

the relations among node voltages and injected powers by generators and absorbed by loads are non linear:

$$P_h = V_h \sum V_k (G_{hk} \cos \theta_{hk} + B_{hk} \sin \theta_{hk})$$

(2.2)

$$Q_h = V_h \sum V_k (G_{hk} \sin \theta_{hk} - B_{hk} \cos \theta_{hk})$$

(2.3)

where:

- $P_h$ ,  $Q_h$  are real and reactive power injections at node h;

- $V_h$  is node voltage amplitude at node h;

- $\theta_{hk}$  is phase displacement between voltages phasors at node h and k;

- $Y_{hk} = G_{hk} + jB_{hk}$  is the generic element of matrix [Y].

In addiction to that, there are several devices inside the network, whose behavior is linear only if limited to an interval with the presence of saturation phenomena, or devices that are inherently not linear (e.g. switches).

The complexity of the control of such system is augmented by several factors:

- external constraints (as environmental issues) strongly limit the expansion of the system;

- while in the past the operations and management were vertically centralized and controlled, nowadays several actors participate in the control. Generation, transmission and distribution are now managed by different companies. Each participant in the system has different goals, thus an additional issue about the coordination of these independent operators arises;

- in the last decades the production of energy is changing rapidly with emerging distributed generation of medium and little (some kVA) size. Distributed generation has performed a rapidly growth due to environmental concerns leading to an incremented use of renewable resources and a better use of fossil fuels (e.g. the combined heat and power power plants of medium and small size) and to the open market of electricity: now it is possible to enter this market also with small productions (and thus small investments). This breaks

the traditional vertical structure in which energy used to be transferred following a topto-bottom pattern.

Such a complex system is managed and controlled with multiple objectives three of the major being:

- supplying loads with adequate level of quality;

- optimizing the economic issues of the overall system;

- minimal environmental impact.

Further, the control objectives are dependent on the operating state of the system. The different operating points are for example classified as normal, alert, emergency, restorative.

A complete centralized control of the whole system is considered unfeasible. Therefore, the system is traditionally decomposed to use the ancient strategy "divide et impera".

Several subdivisions overlap [3]:

- at the voltage level, the electrical network is commonly divided into three main levels: the high voltage network (EHV or HV), the medium voltage network (MV) and the low voltage network (LV). Each of these three can comprise a deeper subdivision with several different voltages. The HV network comprises the high voltage at 400 kV, the 220 kV level and the subtransmission network at 130 kV. The MV as well comprises levels from 60 kV to 20 kV and some parts in 15 kV and 10 kV. The LV is normally distributed in 400 V for the three phase and 230 for the monophase. Although different countries present some differences, for all of them it is common to have a functional subdivision into at least two main levels: a transmission network with high voltages and a distribution network with medium and a low voltage;

- a geographical criteria: although the transmission grid is connected at continent level, it is usually subdivided into different areas interconnected. Also, the distribution network can be subdivided into independent feeders. From the industrial point of view, Independent System Operators (ISO) are organized as national structures and also distribution companies are normally organized on geographical homogeneous areas;

- on time-horizon criteria, the power system comprises physical phenomena with different dynamic time scale. Description and control of the system can be therefore classified and divided on the basis of the dynamic time scales;

- decoupling of variables permits to separate control problems about variables, that are weakly coupled. In transmission networks, voltages are strictly dependent on reactive power flow, while frequency is strongly coupled with active power flows;

- small and large perturbations: the non linear power system is often linearized, thus separating the control problem of response to small perturbations from the problem of response to large perturbations;

- objective criteria: A power system is typically a multi-objective system and it is studied and controlled separately for each objective.

A big issue is to account for the overlapping among the different subproblems, but this will not be considered here. The focus will be only on some aspects of voltage control.

### 2.3 Voltage control

Electric power systems are built essentially with lines connecting generators and users. For the purpose of this thesis an AC line can be modeled as a linear and passive four terminal element. This represents the positive-sequence singular phase equivalent circuit of a line under steady state operating conditions.

Voltages propagates via two voltage waves with a speed w depending on the physical characteristics of the line. The wave length of a line is defined as the distance between two points of the line where at an instant the voltage phasors have a phase difference of  $2\pi$ . Electrical short lines are those lines whose length is small compared to wavelength. The wavelength varies from 6000 km for typical 380 kV ahead lines to 1760 km for underground 15 kV lines. In short lines admittance is negligible and therefore a line can be modeled with the four terminal element shown in Fig. 2.1.

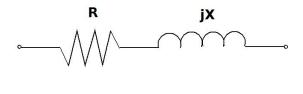

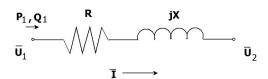

Figure 2.1: AC line - Equivalent circuit of short lines.

The resistance of lines accounting for stranding and skin effect can be determined from manufacturers' tables or calculated by:

$$r = \frac{\rho}{S}k\tag{2.4}$$

where:

- $\rho$  is the dc resistivity expressed in  $\Omega \times mm^2/km$ ;

- S is the cross section in  $mm^2$ ;

- ${\bf k}$  is a coefficient taking into account the temperature effect, the skin effect and the conductor construction.

The positive sequence inductance per unit length can be expressed as:

$$l = 0.46 \log_{10} \frac{2D}{kd} \qquad [mH/km] \tag{2.5}$$

where:

- $\mathbf{D}$  is the geometric mean distance between the three conductors expressed in mm;

- ${\bf d}$  is the diameter of the conductor (supposed equal for all the three conductors) expressed in  $$mm;$}$

- ${\bf k}$  is a coefficient that takes into account the conductor composition, stranding and bundling. It can vary from 0.75 to 0.85.

Considered that the conductors in cable are much closer to each other than are the conductors of overhead lines the inductance per phase in underground cables is lower than in overhead lines.

Most of electrical lines of the distribution system can be considered electrically short.

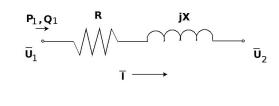

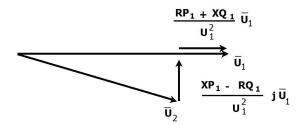

The phasor diagram in Fig. 2.2 of the circuit allows to write the following relations between reactive power, active power and voltage drop in such a line:

$$V_1 - V_2 \simeq \frac{RP + XQ}{V_2} \tag{2.6}$$

Figure 2.2: Phasor diagram - Phasor diagram for short lines.

For lines where also resistance is negligible if compared to reactance, the voltage drop can be expressed in terms of the only reactive power flowing through the line:

$$V_1 - V_2 \simeq \frac{XQ}{V_2} \tag{2.7}$$

Therefore the voltage problem control in the transmission grid (where resistance and admittance of the lines are neglected) depends on the flow of reactive power.

Several reactive power sources are used for controlling voltage

- shunt capacitors;

- shunt reactors;

- SVC Static VAR compensator;

- OLTC On Line Tap Changer;

- synchronous generators;

In this work, only voltage regulation based on generators will be considered.

### 2.3.1 Primary voltage control

Electrical energy generation in transmission networks is essentially constituted by synchronous generators. Therefore a first voltage regulation action is pursued through generators. This regulation action is called the primary voltage control and is provided by excitation control of generating sets, which tends to reduce the difference between the actual voltage at generator terminals and the scheduled set point.

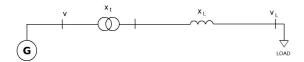

With the approximation of line impendance with the only reactance  $x_L$  (thus neglecting the influence of active power flow on voltage), the relation between the voltage at the generator terminal and at the load is expressed by the equation:

$$v_L = v - (x_t + x_L)q_L$$

Figure 2.3: Primary Control - Generator supplying a load.

Under steady state, voltage at generator terminal can be expressed in terms of excitation voltage:

$$v = v_f - x_d i \tag{2.8}$$

where  $x_d$  is the direct axis synchronous reactance and  $v_f$  is the excitation voltage. The voltage control, acting on the excitation voltage, can support the voltage at load node, increasing the excitation voltage when reactive load increases.

When the active power flowing through a transmission line is lower than the natural power (i.e. natural load) of the line, the line generates reactive power. Therefore, to maintain a constant voltage to the load terminals, the generator should absorb reactive power.

It is possible to control the voltage at the alternator terminals acting on the excitation voltage.

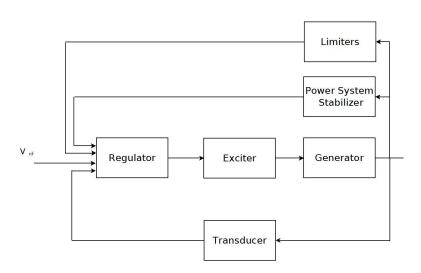

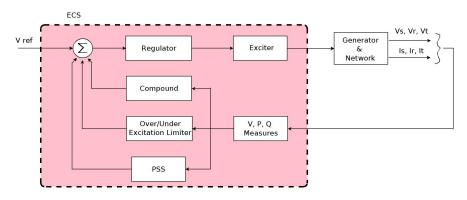

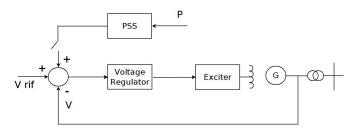

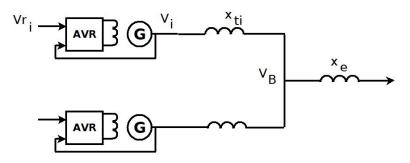

The voltage control for a synchronous generator is performed via the Excitation Control Systems (ECS) whose structure is in Fig. 2.4 [4].

For the aim of the study of the primary regulation, a synchronous generator can be considered connected to a large power system modeled as an infinite bus (i.e. its inertia and short-circuit power is infinite to respect to those of the alternator and therefore bus voltage is constant under any load condition) through a single reactance  $x_R$  (the reactance  $x_R$  is that reactance viewed from the generator terminals).

### 2. VOLTAGE CONTROL

Figure 2.4: ECS - Functional block diagram of a synchronous generator excitation control system [4].

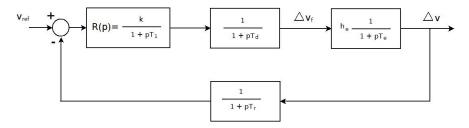

Merely to consider the voltage control loop we can refer to the approximated block diagram in Fig. 2.5

Figure 2.5: ECS diagram - Block diagram of the voltage control loop of a synchronous generator.

Considering that:

- $T_1$  is the high frequency dominant time constant of the voltage regulator which is approximated with a first order transfer function; k is the high frequency dynamic gain of the voltage regulator;

- $T_r$  is the constant time of the transducer that, for modern systems, is of the order of 0.02 s;

- $T_d$  is the time constant of the exciter and is negligible for static exciters, i.e. the static excitation system is approximated with a fast, comparing to the other subsystems, first order system.

To find the transfer function between excitation voltage and generator terminal voltage some approximation can be done. For small variations, assuming an asymptotic high frequency approximation (i.e.  $\omega \gg 1/T'_d$ ) and with a low (dynamic) load angle, the following approximated relations can be considered:

$$\Delta v \simeq \Delta v_q$$

Stator current and voltage and excitation voltage are related with the following expression<sup>1</sup>:

$$v_q = \frac{1}{1 + pT'_{d0}} v_f - x_d \frac{1 + pT'_d}{1 + pT'_{d0}} i_d$$

(2.9)

where :

- $T'_{d0}$  is the direct-axis open circuit time constant: from 5 to 8 seconds;

- $T_d^{'}$  is the direct-axis transient short-circuit time constant: from 0.75 to 1.5 seconds;

- $x_d$  is the direct-axis synchronous reactance: from 1 to 2.5 [p.u.];

The direct axis current  $i_d$  can be expressed in terms of the voltage machine and the network voltage:

$$i_d = \frac{v - v_R}{x_R} \tag{2.10}$$

Modeled the network as an infinite bus ( $\Delta v_R = 0$ ), small variations of the armature current can be expressed as:

$$\Delta i_d = \frac{\Delta v}{x_R} \tag{2.11}$$

Therefore, for small variations:

$$\Delta v = \frac{1}{1 + pT'_{d0}} \Delta v_f - \frac{x_d}{x_R} \frac{1 + pT'_d}{1 + pT'_{d0}} \Delta v$$

(2.12)

It follows that the relation between excitation voltage and terminal voltage variations is:

$$\Delta v = h_e \frac{1}{1 + pT_e} \Delta v_f \tag{2.13}$$

where:

•  $h_e = \frac{x_R}{x_R + x_d}$  can be considered of 0.5 [p.u./p.u.];

<sup>&</sup>lt;sup>1</sup>the additional circuits have no impact under steady-state operating conditions

### 2. VOLTAGE CONTROL

•  $T_e = T'_{d0} \frac{x_R + x'_d}{x_R + x_d}$  is therefore the time constant of the generator under load conditions.

Finally, from Fig. 2.5, the fact that the voltage control loop for a synchronous generator has a cut-off frequency in the order of units of radiants (3 - 6 rad/sec), can be deduced (also in [5]). In other words the closed loop time constant of the primary voltage control loop is lower than 1 second.

The sampling frequency for a digital control system has to be chosen according to the desired bandwith of the closed loop system. the rule that can be used to choose the sampling frequency in control system could be [6]:

$$f_s = (6 \quad to \quad 25) f_B^{CL} \tag{2.14}$$

where  $f_B^{CL}$  is the closed loop bandwidth. This requested sampling frequency will be compared with the real-time performance of the chosen hardware and software platform described in chapter 3.

Although SVC and OLTC are traditionally considered to be part of primary voltage control, they will not be analyzed in this work.

### 2.3.2 Secondary voltage control

Studies on real-time automatic control of power system voltage and reactive power started in the 1970s and led to significant proposals and applications. Hierarchical approaches in frequencyactive power control of multimachine power systems for reducing the complexity of solutions with a large-ordes systems can be found in [7]. A centralized optimizing computational algorithm for the on-line control of voltage and reactive power is presented in [8] [9] and [10]. The stress is on real-time control of reactive power and voltage, using large-scale digital computing facilities and system-wide data transmission channels already installed for the automatic frequency control.

One of the implemented strategies of voltage control in EHV transmission networks consists in dividing a power system into several areas [11] and setting up a hierarchical voltage control system. The crucial idea to decompose a large power system into several blocks in such a way, that the electrical coupling between blocks can be made as small as possible, is also presented in [12].

Algorithms and control schemes using electric power plants as continuous sources of reactive power for voltage control, together with the subdivision of the power system into different coordinated blocks, were then exploited and developed in several countries under different approaches.

Voltage hierarchical controls were studied and developed in Italy [13] and [14].

Also in France since the 1980s a secondary voltage control has been studied [15].

Hence, similar hierarchical controls for EHV transmission networks were adopted also in Spain [16] and South Africa [17].

The aim of the Secondary Voltage Regulation (SVR) is to keep constant the voltages of some HV nodes, upon load variations and perturbations in the system. As already seen, voltages in HV nodes are mainly affected by reactive power flows and several sources of reactive power are present in power sistems: generators, shunt capacitors and reactors, static VAR systems.

Once the appropriate operating voltages of the HV nodes is determined solving optimal power flow problems, an automatic system is desired acting on reactive power sources, to maintain such voltages constant despite the perturbations in the system. A centralized control, reading all selected HV node voltages and acting simultaneously on all reactive power sources in the system to maintain the voltages in those nodes constant, has always been considered unfeasible.

The main reasons against a centralized control are the complexity of the transmission data system, the computing time for a central unit to cover all the system and the reliability of a centralized architecture.

Node voltages variations and reactive power variations of the linearized power system, can be expressed with a linear relation:

$$[\Delta v] = [A][\Delta Q] \tag{2.15}$$

where [A] is a voltage sensitivity matrix.

A transmission power system is convenientely subdivided into subsets of nodes and therefore the linear relations above can be written as:

| $4_{1,1}$ | ÷     | $A_{1,j}$ | ÷     |           | ÷     | ]         | $\left[\Delta Q_{S1}\right]$                                   |   | $\Delta v_{S1}$ |        |

|-----------|-------|-----------|-------|-----------|-------|-----------|----------------------------------------------------------------|---|-----------------|--------|

| • • •     | • • • |           | • • • | •••       | • • • |           |                                                                |   |                 |        |

|           | ÷     | $A_{i,i}$ | ÷     | $A_{i,j}$ | ÷     |           | $\begin{array}{c} \dots \\ \Delta Q_{Si} \\ \dots \end{array}$ |   | $\Delta v_{Si}$ |        |

| • • •     |       |           |       |           |       |           |                                                                | = |                 | (2.16) |

|           | ÷     |           | ÷     |           | ÷     |           |                                                                |   |                 |        |

| • • •     | • • • |           | • • • | • • •     | • • • |           |                                                                |   |                 |        |

|           | ÷     |           | ÷     |           | ÷     | $A_{n,n}$ | $\Delta Q_{Sn}$                                                |   | $\Delta v_{Sn}$ |        |

In a decentralized control scheme each subsystem is controlled independently, i.e. the non diagonal submatrices  $A_{i,j}$  where  $i \neq j$  are neglected.

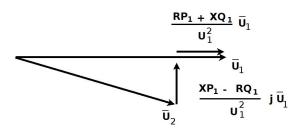

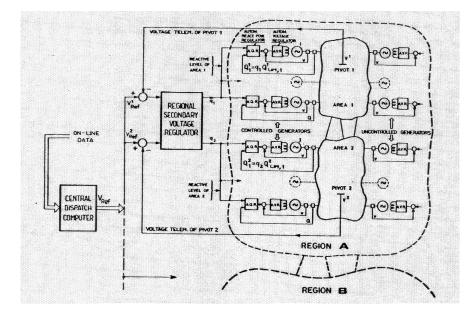

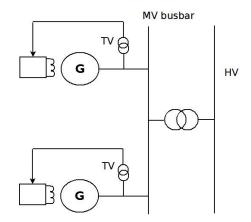

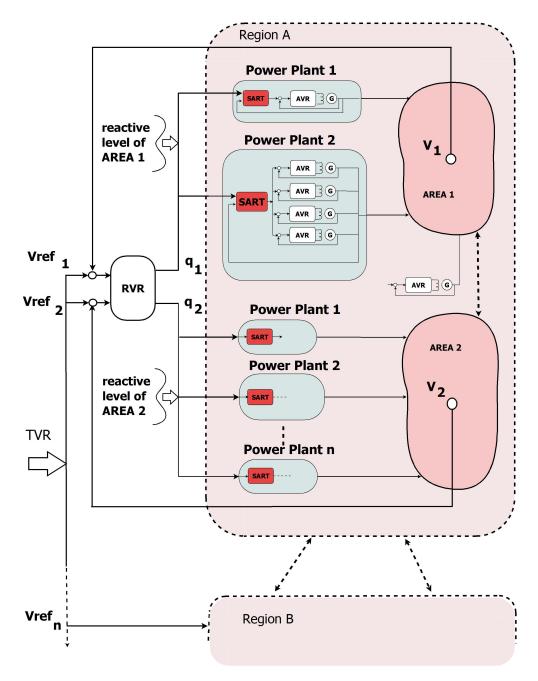

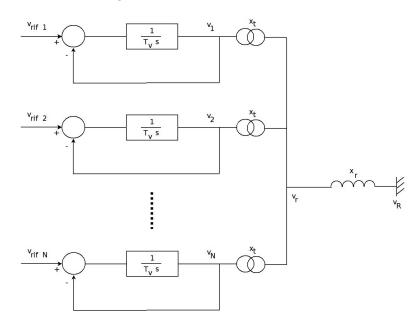

In Fig 2.6 the original schematic diagram of the hierarchical voltage control system is reported as it was presented in 1983 in [14] for the italian HV power system.

Figure 2.6: SVR diagram - Schematic diagram of the hierarchical voltage control as it was presented in 1983.

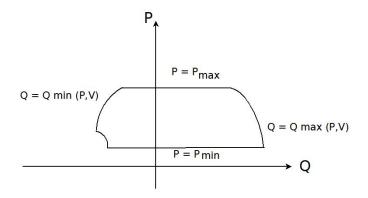

The above diagram is still relevant and in chapter 6 the same schema is presented with the terminology as it stands now according to the Italian national grid code. The first hierarchical level is constituted by the conventional voltage regulator of each generator (i.e. AVRs). The second level consists of the regional secondary voltage regulators and the reactive power station regulators (called Automatic Reactive Power Regulator - AQR in the schema 2.6 and called SART in the Italian Grid code as it will be described in chapter 6 ). The regional secondary voltage regulator controls the voltage of pilot nodes through an integral action while the SARTs apparatus actuates the reactive power level required by the regional controller acting on the AVRs. The regional regulator receives the voltage values of its pivot nodes and compares these values with the reference values fixed by the tertiary regulator and sends a reactive level signal to each of the reactive power regulators of its area. The reference of reactive regulators is the reactive level ( a scalar quantity q in the range of  $-1 \le q \le 1$  multiplied by the reactive power limit (depending on the size of the generators and their operating point, i.e. depending on the

capability curves):

$$Q_{ref} = q_{ref} \cdot Q_{lim} \tag{2.17}$$

where:

- $Q_{ref}$  is the reactive power requested to the generator;

- $Q_{lim}$  is the reactive power limit of the generator;

- $q_{ref}$  is the reactive level transmitted.

The third hierarchical level is made at central level and has the purpose to determine optimum values of the voltages of some nodes (called pilot nodes), that are controlled by the secondary regulators. The architecture and implementation of the AQR (now called SART) apparatus is the main topic of this work.

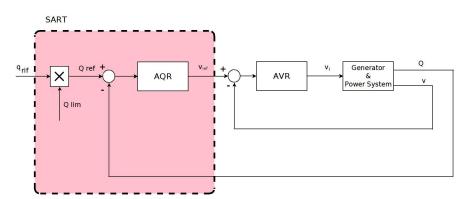

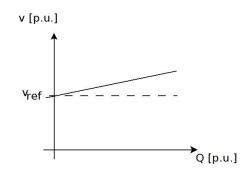

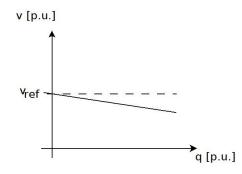

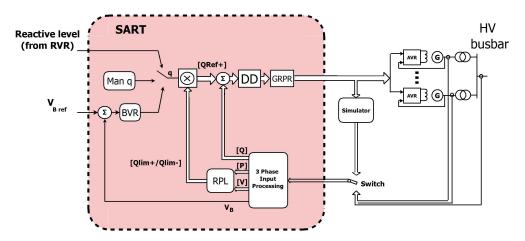

The reactive power control loop implemented by SART apparatus is shown in Fig 2.7.

Figure 2.7: RPR diagram - Block diagram of the reactive power control loop of the secondary voltage regulation.

The closed-loop time constant of the reactive power control loop of a power plant is set to be ten times lower than the inner voltage control loop (i.e. the one before described and implemented with AVRs), and therefore is usually in the range from 5 to 10 seconds.

#### 2.3.3 Voltage control in distribution network

Despite the differences that can be noticed across the world, some common elements in the realization and mode of operation and connection in the distribution networks can be found:

- the network is normally designed in a radial way: starting from HV/MV substations, conductors take different directions with a tree structure;

- every country imposes constraints on the characteristics of voltage signals limiting amplitudes fluctations (often a  $\pm 5\%$  limit is considered);

- although it is hard to highlight a constant type of conductor the main physical characteristics used are

- aluminum (and combinations aluminum-steel) cables with sections varying from 50  $mm^2$  to 500  $mm^2$ ;

- copper (and combinations copper-steel) cables with sections varying from 40  $mm^2$  to 150  $mm^2$ ;

- MV lines are normally three-phased feeders with or without a neutral conductor. The three (or four in case of distributed neutral) conductors can be overhead or underground, being the latter the most common choice in urban areas.

The voltage drop in a distribution feeder can be expressed as in equation 7.2, here reported:

$$V_1 - V_2 \simeq \frac{RP + XQ}{V_2} \tag{2.18}$$

This approximation is true if the angle between the voltages of the input and output of the line is small (as it is for short lines not highly charged).

Differently from transmission networks, where the term RP can be neglected due to the low value of the R/X ratio, in distribution networks both terms must be considered, as R/X is higher. Table 2.1 reports some typical values for longitudinal primary constant of lines as in [18].

| Type of line                           | r[ohm/km] | l[mH/km] | x[ohm/km] | R/X   |

|----------------------------------------|-----------|----------|-----------|-------|

| 380 kV overhead line, single conductor | 0.029     | 1,22     | 0.383     | 0.075 |

| 380 kV overhead line, twin conductors  | 0.028     | 0.99     | 0.310     | 0.090 |

| 220 kV overhead line                   | 0.084     | 1.30     | 0.408     | 0.206 |

| 130 kV overhead line                   | 0.228     | 1.26     | 0.395     | 0.577 |

| 380 kv underground cable               | 0.028     | 0.22     | 0.069     | 0.406 |

| 220 kV underground cable               | 0.056     | 0.37     | 0.116     | 0.483 |

| 15 kV underground cable                | 0.150     | 0.30     | 0.094     | 1.596 |

Table 2.1: Line cable data - Line data for different type of cables at 50Hz.

In traditional distribution networks, the power flow is unidirectional: it goes from the HV/MV station to the consumers. Therefore the voltage decreases between the distribution substation to the end of the feeder. When in presence of generators in the distribution network, due to the injection of active power, the voltage profile can be non monotonically descendant.

To guarantee equipment safety (too high voltage can reduce the lifespan of users' appliances) and correct functioning, the voltage has to be kept within its contractual range defined on the grid code.

The main control devices used in distribution feeders to regulate the voltage in order to guarantee the contractual limits are On-Load Tap Changers (OLTC) transformers and auto transformers. These are devices in which is possible to alter the transformation ratio by discrete steps. The voltage of MV buses is adjusted in function of the variations of loads and the evolution of the upstream voltage. Although some industrial customers connected to the MV network having their own means of reactive compensation (e.g. capacitor banks and static var compensators), no other voltage control is made in distribution grids apart than those discrete regulations with transformers described.

An evolution in distribution networks has taken place over the past few years with the introduction of the so called Distributed Generation. A deep exploitation of the problems leaded by the introduction of DG can be found in [19]. In chapter 7 the impacts on the voltage profile because of the active power injections, when in presence of productions of electrical energy connected to the distribution network, will be described and a possible strategy of voltage/var control is presented.

# 2.4 Conclusions

Due to the complexity of power systems, their control is split into a number of subproblems. Some aspects of voltage control were reported. Time constant of the voltage control loop for synchronous generators is commonly reported to be in the range  $0.2 \div 1$  second. For the secondary voltage control, the power plant reactive power control loop time constant is usually around 5 seconds. Time constants of these control loops have to be compared to real-time performances of the operating system, that is described in next chapter.

## 2. VOLTAGE CONTROL

# **Real-time operating systems**

## 3.1 Introduction

A review of real-time operating systems and their performance is reported. RTAI has been chosen and its structure and development tools are detailed. Adequacy of RTAI to the development of control systems for electrical energy production and regulation is attested through measurements of its performance under different working conditions. The design and development methodology used are presented.

# 3.2 Real-time control systems

Several different hardware and software architectures are available to build real-time controls, each with an impressive variety of different commercial or open source products. We have focused on utilizing common hardware, which is easy to maintain, with general-purpose widely used processors and operating systems which can be profitably integrated in a distributed environment. Often, Hard Real Time (HRT) control tasks are accomplished by employing specific dedicated processing units. An example is the wide use of Digital Signal Processors (DSPs) or micro controllers which guarantee a bounded interrupt latency. The key issue in HRT is that the control system has to guarantee signal processing timing, without missing deadlines for interrupts and keeping latency bounded within a level compatible with the sampling time of the process. As in [20], a real-time system has to respond to externally generated input stimuli within a finite and specifiable delay.

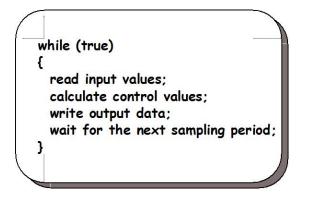

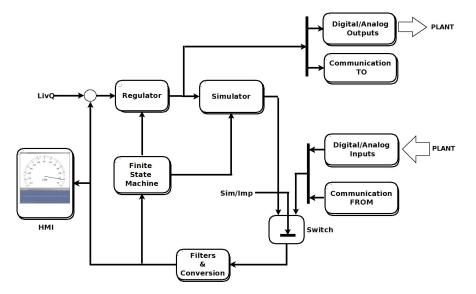

A general control algorithm can be simplified with the code in Fig. 3.1: a control law is designed according to discrete-time control system theory and implemented as a real-time periodic task:

Figure 3.1: Control - General schema of a controller.

In the design process of a digital control system there are two fundamental constraints which have to be fulfilled by the device implementing the control:

- Computational power: inspecting the algorithm and its implementation code is possible to exactly determine how many fundamental mathematical functions have to be executed. The computational requests of the control task can be expressed in floating point operations per second. To simplify all this, it is possible to measure the execution time of the control loop on the target hardware platform;

- Temporal constraints: several temporal requirements can be found in the control algorithm. The first requirement is the frequency at which the control task is executed.

From the control designer's point of view, the variation of the scheduling time is important and determines if a chosen hardware and software platform is suitable for a certain control task.

For the frequencies requested by control algorithms described in chapter 2, considered the computational performance of modern 32 and 64 bit CPUs, the computational time requested for the control algorithm is normally well beyond the period of the control system. Also, the computational time itself presents a negligible variation. Differently from DSPs, that have an architecture focused on numerical computations, and are also designed to have a strong determinism in computational time, General Purpose Processors (GPPs) have been developed for general purpose computing and are not specifically designed and optimized to keep a guaranteed scheduling jitter.

GPPs that can be found in personal computers, servers, network apparatuses but also in personal entertainment devices, present a strong, non-deterministic behaviour in computational time: several tasks (some of them completely out of the control designer's control) fight for the use of the processor units.

Therefore, GPPs while presents adequate performance to carry out signal processing tasks, they do not have suitable deterministic timing characteristics for real-time controls.

The use of Commercial-Off-The-Shelf (COTS) low cost personal computers (and all their hardware and software components) for digital programming and signal processing can lead to a reduction of the cost of the final device. Utilization of cheap microprocessors for real-time systems has been investigated since the 1980s [21].

The great progress made by the semiconductor industry has provided cheaper 32 and 64 bit processors with Memory Management Unit (MMU). One of the features provided by MMU is the memory protection, which gives a higher level of fault tolerance in software development because different tasks can function in a separate and protected memory space [22].

Therefore there are several CPUs on the market with an extremely high computation power, available at low prices, as a complete set of motherboards and entire COTS computing systems ready for running. The main disadvantage of these systems is that they were not designed for real-time, but even if GPPs are not specifically designed and optimized to carry out signal processing tasks keeping a guaranteed scheduling jitter, an RTOS can make them suitable for real-time applications.

#### 3.2.1 Operating systems

An Operating System (OS) is commonly identified as the software that controls and manages the hardware of a computing system; one of its main purposes is to implement the interface used by all the other users' programs to have access to the hardware itself. This interface is a collection of software programs that implement the system-calls. The system calls are all the basic functions required to operate with the hardware. The set constituted by the system calls is what the OS offers to programmers.

For the x86 32 bit architecture of the Linux kernel 2.6.29 there are circa three hundred system calls whose names and numbers can be found in the *include/asm-x86/unistd\_32.h* file in the Linux sources. As an example of system calls these could be taken into consideration:

**sys\_fork** to create a child process;

**sys\_exit** to terminate the current process;

sys\_open to open and possibly create a file descriptor;

sys\_close to close a file descriptor; sys\_read to read from a file descriptor; sys\_write to write to a file descriptor;

## $\mathbf{sys\_mount}$ to mount a file system;

Therefore the set of system calls represents the core (often called kernel) of an OS. On all those system calls several higher level functionalities are built in a modern OS. Although the functionalities that an operating system have to offer to programmers is universally accepted, the way this functionalities are presented is a matter of standard. There are several standards on how system calls ought to be used.

One of the most used standards for the Application Programming Interface (API) offered by an operating system is the standard Portable Operating System Interface for Unix (POSIX). POSIX is an IEEE standard and defines the interface for each feature: it defines all the functions an Unix operating system has to implement.

Unix is one of the most important operating systems. Unix has become important because in it the most of the fundamental ideas on design of OS (ideas that have been implemented also by most of all the other OS on the market) were first implemented, nonetheless Unix, in one of the several existing implementations, is still one of the most used OSs.

Unix was born in the Bell laboratories during the 1960s and 1970s and is the result of the effort by many people, the most famous names that can be remembered are Ken Thomson, Dennis Richie and Brian Kernighan. Multitasking, multiuser and virtual memory management are three pillars of Unix that can now be found in every OS. The Unix source code was published by Bell laboratories to accomplish US antitrust laws and several different Unix-like OSs have since been autonomously developed by different groups and companies.

## 3.2.2 Linux

Among all those that pursued their studies and development on Unix, prof. Tanenbaum from University of Vrije of Amsterdam and his collaborators wrote an Unix kernel named Minix [23]. Minix, at that time, was one of the few running on the cheap x386 platform. To get the Minix source code one only had to buy prof. Tanenbaum book on operating systems [22].

One of the users of Minix was a Finnish student : Linus Torvald. He went some steps forward: he started writing a new, free Unix-like OS. When his kernel was approximately running, during the month of October 1991 he looked for help: as a consequence a new community of developers started.

Linux is one of the several General Purpose Operating Systems (GPOS) which have been developed for 32 and 64 bit processors with MMU that has become widely used. It is known as the GNU/Linux system: it is composed by a kernel [24] [25] and a collection of system software [26] whose source code is freely available under the Generic Public License (GPL) [27].

## 3.2.3 Real Time Operating Systems

Even if GPPs which are normally present on commercial PCs are not specifically designed for real-time, a RTOS can make them suitable for real-time applications.

Several commercially supported embedded operating systems have been proposed in the last two decades: a list of RTOS on wikipaedia includes 106 different ones [28]. Commercial RTOS often require to pay per-unit-royalties but, when adequately supported by the developing companies (normally with an added maintenance cost), they do not require a complete understanding of the hardware and software platform in order to develop an application. Moreover they leave the developer to concentrate their efforts on the application itself rather than on the RTOS used. On the other hand, some commercial RTOS do not rely on an open architecture and do not always offer a standard API. Therefore it can be difficult to migrate to other platforms and thus the developer and the product destiny are too strictly closed to the RTOS company with the risk, when the company disappears, to be left out in the cold.

Some of the RTOS have been designed from ground up starting from a real-time kernel and adding new features to became a complete operating system. The computer performance and the capacity improvements have increased the demand of functionality of each processing device (e.g. the request of graphical interfaces), boosting the request for RTOS to present all the features of a GPOS.

Economical reasons lead to the emerging approach to extend a GPOS to be an RTOS, in particular starting from open source operating systems. Therefore along with the RTOS born as a real-time system, several RTOS have been built as extension of existing non real-time OS.

There are also different strategies in extending an OS to an RTOS: single kernel approach or multi kernel approach. In [29] is presented a summary of different real-time extensions of Linux (therefore different strategies to extend an OS, focused only on Linux).

Although the majority of RTOSs have a Unix-like structure, Windows CE is a version of Windows with real-time performance.

Among consolidated or new emerging RTOSs which can be used with GPPs, the following can be quoted:

- RTLinux: it started at New Mexico Institute of Technology [33]; several other projects based on Linux followed this approach, although the original solution was patented [34];

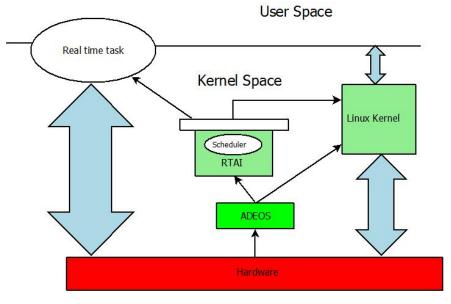

- Real Time Application Interface (RTAI) : it was developed at Politecnico of Milano [30] and has also been used for distributed controls [31];

- QNX: a commercial RTOS based on a microkernel, born on 1982 [32];

- VxWorks: born 25 years ago, it is still one of the worlds leading RTOS.

The listed RTOSs differ for a lot of characteristics. RTLinux and RTAI are two patches that have to be applied to a Linux kernel<sup>1</sup> to make it a real-time system. This means that they are extensions of an existing OS. They do not live by themselves but only as a part of an open source OS. Both are based on Linux and therefore the development of all their parts not strictly implied in the real-time core is left to the international volunteer community of developers.

Having RTLinux been patented, it presents some limitations in its commercial use. On the other hand, RTAI is published under the GPL and is freely usable also for commercial purposes without any royalty.

QNX and VxWorks are two complete RTOSs, they do not depend on other OS. Both OSs are owned by private companies and are maintained, upgraded and ported to different kinds of hardware by those companies.

From a more technical point of view, QNX has a microkernel structure while the others are monolithic kernels. From the user's point of view, the fact that it is based on a microkernel architecture or on a monolithic one does not have any practical effects. Most experts agree on the fact that a microkernel architecture is more appropriate for modern OSs including a huge and always increasing list of functionalities but the majority of the OS on the market are monolithic. All the four OSs can be defined Unix-like because each of them is a POSIX compliant.

Some operating system vendors offer not an extension of their GPOSs but a limited version of them with real-time capabilities; the already mentioned Windows CE is a (limited) version of Windows while Chorus OS from Sun Microsystems is a real-time flavor of the Solaris OS.

$<sup>^1\</sup>mathrm{An}$  original so called vanilla kernel that can be downloaded from http://kernel.org

An analytical review and comparison of all the presented RTOSs is beyond the scope of this work.

This work will present some applications related to the production and management of electrical energy with RTAI. Most of the considerations could be applicable to all the other mentioned RTOSs. All the two implemented devices that will be detailed in the next chapters could be also developed with one of the other RTOS, probably with a similar performance and comparable efforts. Therefore, several different RTOSs could be chosen to develop a real-time device which is easy to integrate in a complex SCADA system, is ready to be ported on different hardware platforms, is open to different communication protocols and has a good performance.

RTAI was chosen for this project.

## 3.3 RTAI

Real-time performance in modern OSs is strictly related to one of the most common characteristics of general purpose OSs: multitasking. There still exist real-time devices implemented in the old DOS: this is possible because DOS was not a multitasking OS. When a single task is running on a CPU there are minimal problems to control interrupts coming from the hardware (e.g. an interrupt coming from a clock saying that the control task has to start). In multitasking systems there are several active processes but only one (in single processor systems) running at a specific time: when a single processor is presented in a system, it executes only one instruction at a time and this instruction belongs to a unique process among those which are active. When an interrupt arrives from the hardware (e.g. the interrupt from a timer to wake up the control loop shown in Fig 3.1) the running task has to be suspended to respond to the interrupt: a real-time system assures that each interrupt will be elaborated in a specific, deterministic time. Therefore each process, no matter if it is running kernel-code or user-code, has to be interruptible and the context switch has to be executed in a specified amount of time.

#### 3.3.1 Why Linux is not real-time

There are several reasons why Linux is not considered a real-time system:

- System calls are not-preemptible: this is strictly true only with the older version 2.4 of Linux. Although the latest 2.6 versions of Linux kernel system calls are preemptible, the granularity level is such that the real-time performance is limited;

- Virtual memory swapping activity can introduce unpredictable delays and latencies;

• I/O activity is normally buffered and scheduled in a non-deterministic way.

There are also some aspects which are strongly related to the hardware architecture that leads to non real-time systems:

- Pipelining: in modern processors, instructions are divided in several phases that are parallelized and loaded in advance. When an inversion in the order of the instructions happens, as for executing an interrupt handler code, the pipeline has to be destroyed, leading to a non deterministic delay;

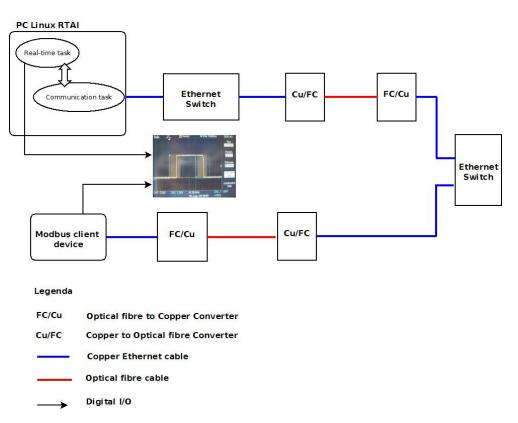

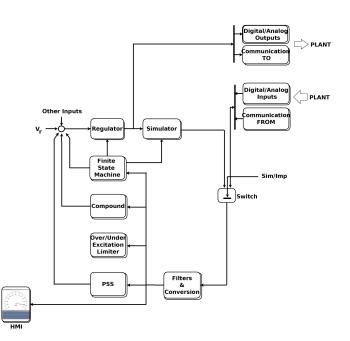

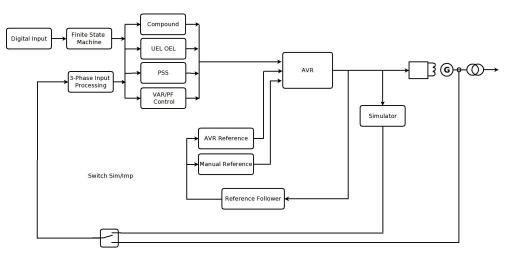

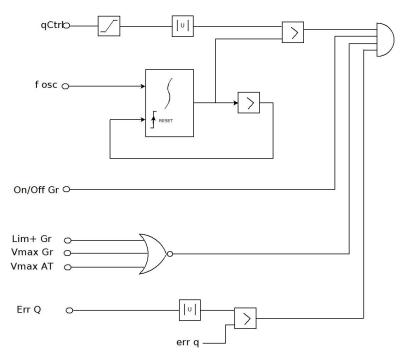

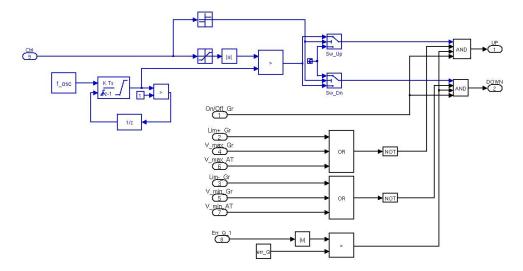

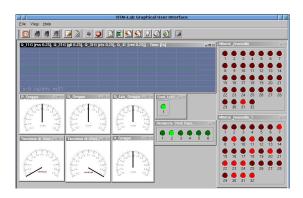

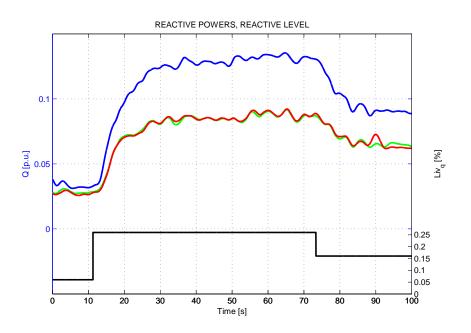

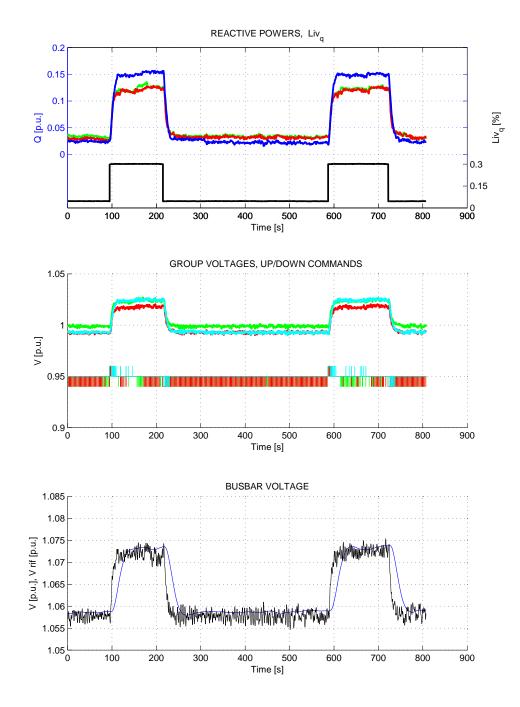

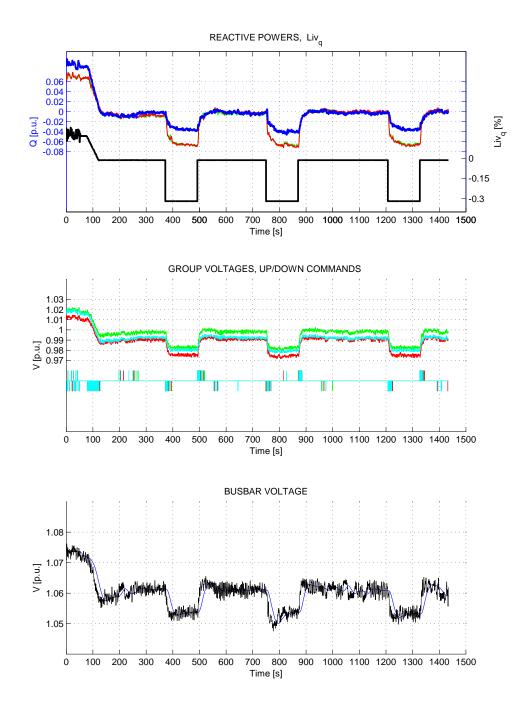

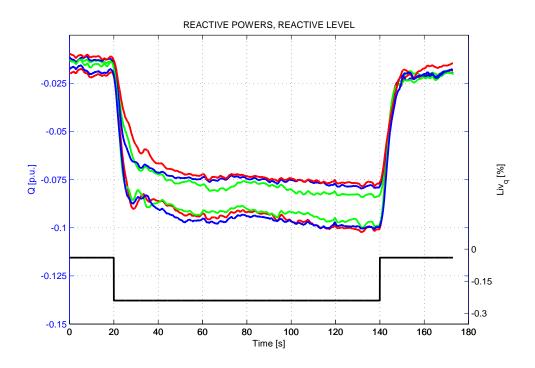

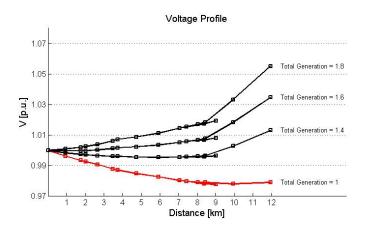

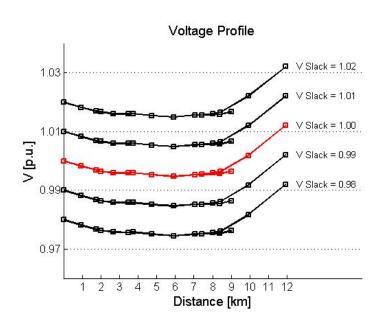

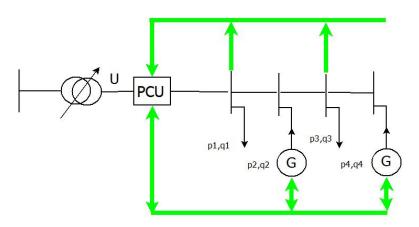

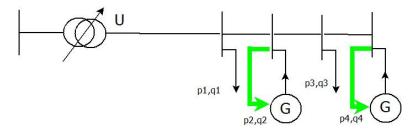

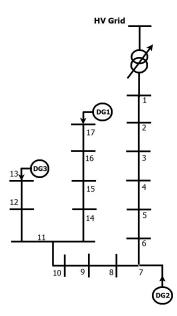

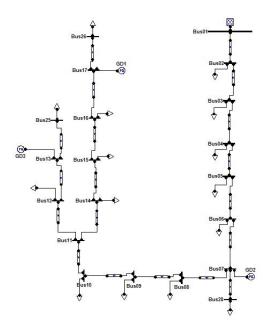

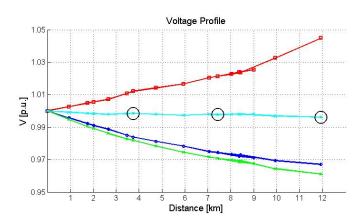

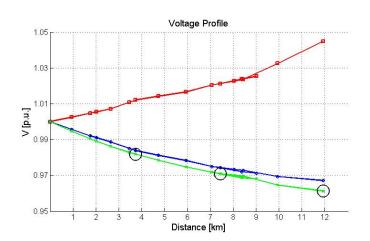

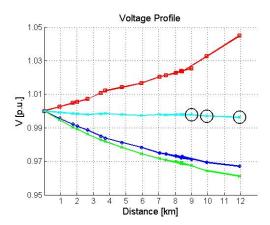

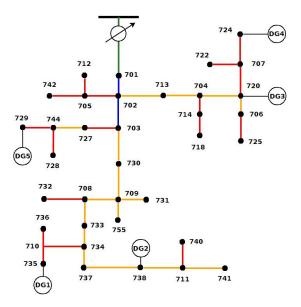

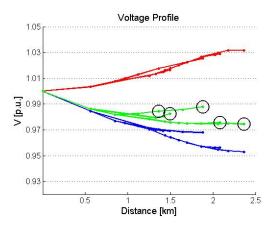

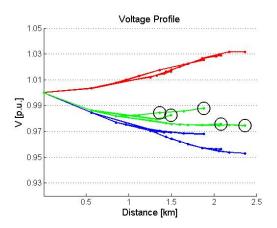

- Cache: as mentioned before, the load of code following an interrupt destroys all the codes and data actually present in cache, introducing extra work with its unexpected delay.