### UNIVERSITÀ DEGLI STUDI DI PADOVA

Facoltà di Ingegneria

Dottorato di ricerca in Scienza e Tecnologia dell'Informazione

Tesi di Dottorato

# RELIABILITY AND PARYLENE ENCAPSULATION OF ORGANIC DEVICES

Supervisore: Prof. ENRICO ZANONI Dottorando: ALESSANDRO PINATO

Cutter: You settled on a name yet? Robert Angier: Yes I have. The Great Danton. Cutter: Bit old-fashioned, isn't it? Robert Angier: No. It's sophisticated.

from Christopher Nolan's "The Prestige", 2006

A Roberto, Lucia, e Luna ...

### Abstract

Organic semiconductors are at the basis of a relatively new research field, called Organic Electronics. The study of the photo-conductive, electrical and optoelectronic properties of organic materials, the charge and exciton transport as well as the thin film growth has led to the development of *organic* transistors, LEDs and solar cells. More complex organic designs, like flexible electronic circuits, photovoltaic panels and Radio Frequency IDentification (RFID) tags are under development, while OLEDs modules are nowadays one of the most promising technologies for display and lighting application and their break-in the mainstream electronic markets is forthcoming.

In this context the stability over time of the organic semiconductor, the use of a proper encapsulation, and a sufficient lifetime of the encapsulated organic devices become essential in order to achieve the success of this technology. Moreover, the investigation of the physical phenomena behind the degradation of the performance of the basic organic devices is both a scientific challenge and an appealing quest for the research community.

During the last three years I mainly focused my studies on two kind of organic devices, namely Organic Light-Emitting Diodes (OLEDs) and Organic Thin-Film Transistors (OTFTs).

More precisely I have worked in two domains: the first part of my work concerns the study of the reliability and thermal properties of OLEDs, mostly based on Alq3 Electron Transport Layer (ETL), and NPD Hole Transport Layer (HTL). These studies have been carried out by investigating the variation of the electrical, optical and thermal characteristics of the devices, during reliability stress tests. Within this work we have tested OLEDs with different inner structure (sort and thickness of the organic layers as well as of the contacts), different size and shapes of the active area. Both temperature and current have been singularly used as stress accelerating factors. The carrying out of reliability tests at different stress current values has allowed to extrapolate degradation laws, and consequently to calculate lifetime laws. Our studies on phosphorescent OLEDs stressed at different current levels, show an increase of the operating voltage univocally correlated with the number of carriers injected in the devices during the stress.

Electro-luminescence degradation mechanisms in small-molecules based OLEDs have been investigated. In particular, we focused on intrinsic degradation phenomena that determine the decrease of the optical power during standard operation. The results of this analysis provide information on the physical processes responsible for OLEDs degradation, suggesting a strong correlation between the reduction in the luminance intensity of the devices and the occurrence of defects and positive trapped charge at the Alq3/NPD interface.

Moreover, we studied the uneven decrease of the optical power along the active area of OLEDs subjected to electrical stress tests. This phenomenon has been correlated to the self-heating and surface temperature profile of the devices. A current crowding phenomenon has been hypothesized in order to explain the light emission, as well as the surface temperature distribution.

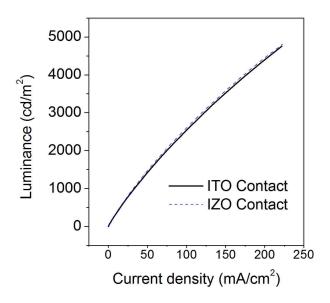

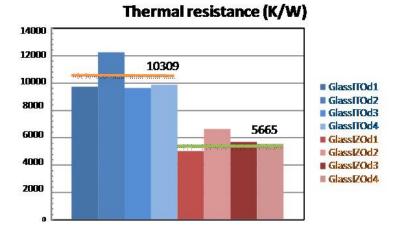

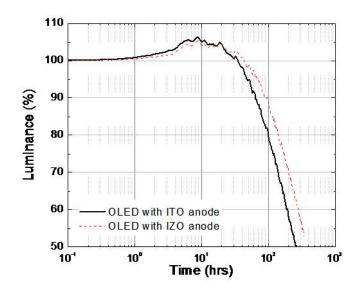

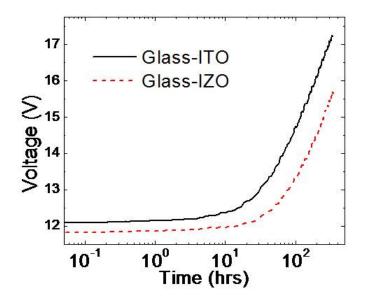

An extensive study has been applied to the thermal properties of the anode layer of the OLEDs, by comparing devices built with different Transparent Conductive Oxides (TCO). Particularly, the performance and reliability of OLEDs with Indium-Tin Oxide (ITO) and Indium-Zinc Oxide (IZO) anode contact layer have been investigated. The devices have been compared in terms of efficiency, thermal resistance and reliability. The results of this study have shown that OLEDs with IZO anodes guarantee performance comparable with OLEDs with ITO anodes, and proved a better heat dissipation as well as longer lifetime.

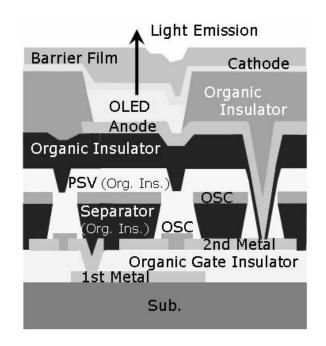

The last part of my work is related to the technological development of both bottom and top contact OTFTs, and to the study of their stability. By working in collaboration with the European microelectronic research centre *IMEC*, we have manufactured innovative photo-lithographic patterned top contact OTFTs. By using a wet etching process, we have realized top contact OTFTs with  $10\mu$ m channel length, obtaining mobilities greater than  $0.5cm^2/(Vs)$ . Moreover, we have developed an innovative process flow that allows the patterning of Silver source-drain contacts on the top of the organic semiconductor, by using plasma dry etching. The process flow has been proved on silicon, as well as on foil substrate. Finally, we have investigated the reliability of standard Pentacene-based organic transistors and the encapsulation of these devices by using a poly(pxylylene) polymer (Parylene C).

### List of Publications:

**A. Pinato**, M. Meneghini, A. Tazzoli, A. Cester, N. Wrachien, E. Zanoni, G. Meneghesso, B. D'Andrade, J. Esler, S. Xia, J. Brown. "Indium Zinc Oxide as an alternative to Indium Tin Oxide in OLEDs Technology". HeTech'08, 17<sup>th</sup> European Workshop on heterostructure Technology, 2008

A. Pinato, M. Meneghini, A. Cester, N. Wrachien, A. Tazzoli, E. Zanoni, G. Meneghesso, B. D'Andrade, J. Esler, S. Xia, J. Brown "Improved Reliability Of Organic Light-Emitting Diodes With Indium-Zinc-Oxide Anode Contact", 2009 IEEE International Reliability Physics Symposium, Montreal, Canada, April 26-30, 2009

A. Pinato, A. Cester, M. Meneghini, N. Wrachien, A. Tazzoli, S. Xia, V. Adamovich, M. S. Weaver, J. J. Brown, E. Zanoni, G. Meneghesso. "Impact of trapped charge and interface defects on the degradation of the optical and electrical characteristics in NPD/ $Alq_3$  OLEDs", IEEE Transactions on Electron Devices, Vol. 57, N<sup>o</sup>. 1, January 2010

N. Wrachien, A. Cester, **A. Pinato**, M. Meneghini, A. Tazzoli, G. Meneghesso, J. Kovacb, J. Jakabovicb, D. Donovalb, "Charge Trapping in Organic Thin Film Transistors", HeTech'08, 17<sup>th</sup> European Workshop on heterostructure Technology, 2008

N. Wrachien, A. Cester, A. Pinato, M. Meneghini, G. Meneghesso, A. Tazzoli, J. Kovac, J. Jakabovic, D. Donoval, "Threshold Voltage Instability In Organic Tft With  $SiO_2$  And  $SiO_2$ /Parylene-Stack Dielectrics", 2009 IEEE International Reliability Physics Symposium, Montreal, Canada, April 26-30, 2009

N. Wrachien, A. Cester, A. Pinato, M. Meneghini, A. Tazzoli, G. Meneghesso J. Kovac, J. Jakabovic, D. Donoval, "Organic TFT with *SiO*<sub>2</sub>-Parylene Gate Dielectric Stack and Optimized Pentacene Growth Temperature", 39<sup>th</sup> European Solid-State device research Conference, ESSDERC 2009, Athen 14 - 18 September 2009

N. Wrachien, A. Cester, N. Bellaio, **A. Pinato**, M. Meneghini, A. Tazzoli, G. Meneghesso, K. Myny, S. Smout, J. Genoe, "Light, Bias, and Temperature Effects on Organic TFTs", 2010 IEEE International Reliability Physics Symposium, Anaheim, USA, April 26-30, 2010

### Sommario

I semiconduttori organici sono alla base di un relativamente nuovo campo di ricerca, chiamato Elettronica Organica. Lo studio delle proprietá elettriche, foto-conduttive e optoelettroniche dei materiali organici, il trasporto di carica e di eccitoni, e lo studio della crescita di film sottili, ha permesso lo sviluppo di transistors, LED e celle solari basati su semiconduttori organici. Design più complessi, quali circuiti elettronici e pannelli fotovoltaici flessibili, RFID (Radio Frequency IDentification) tag sono al momento in via di sviluppo, mentre i display OLED sono considerati una delle tecnologie più promettenti per quanto riguarda i display e l'illuminazione, ed è prevista come imminente la loro diffusione nel mercato elettronico mondiale.

In questo contesto la stabilità nel tempo del semiconduttore, l'utilizzo di un incapsulamento adeguato e un sufficiente tempo di vita del dispositivo incapsulato, diventano essenziali al fine di ottenere il successo di questa tecnologia. Inoltre lo studio dei fenomeni fisici alla base del degrado delle performance dei dispositivi basati su semiconcuttore organico, rappresenta per la comunità scientifica sia una sfida, sia un'affascinante ricerca.

Nel corso degli ultimi tre anni mi sono occupato principalmente dello studio di due tipi di dispositivi organici: LED a semiconduttore organico (OLED) e transistor a semiconductor organico (OTFT). In particolare ho lavorato in due diversi ambiti: la prima parte del mio lavoro riguarda lo studio dell'affidabilità e delle proprietà termiche di OLED, basati sull'electron transport layer (ETL) Alq3 e sull'hole transport layer (HTL) NPD. Questi studi sono stati realizzati monitorando la variazione delle caratteristiche elettriche, ottiche e termiche dei dispositivi durante test di stress accelerato. All'interno di questo lavoro abbiamo testato OLED con differente struttura interna (tipo e spessori sia degli strati organici che dei contatti), con differente dimensione e forma dell'area attiva. Entrambe temperatura e corrente sono state singolarmente utilizzate come fattori acceleranti. La realizzazione di stress di affidabilità utilizzando differenti valori di corrente di stress, ha permesso di estrapolare leggi di degrado, e conseguentemente di calcolare il tempo di vita dei dispositivi. I nostri studi su OLED fosforescenti sottoposti a stress elettrico, con differenti valori di corrente di stress, hanno mostrato un aumento della tensione operativa dei dispositivi univocamente correlato con il numero di portatori iniettato nei dispositivi durante lo stress. Sono stati investigati meccanismi di degrado dell'elettroluminescenza di OLED basati su oligomeri. In particolare ci siamo concentrati sui fenomeni di degrado intrinseco che provocano una diminuzione della potenza ottica durante il funzionamento standard. I risultati di questa analisi forniscono informazioni sui processi

fisici responsabili del degrado degli OLED, e indicano una significativa correlazione tra la diminuzione dell'intensità luminosa dei dispositivi e la presenza di difetti e carica positiva intrappolata all'interfaccia tra Alq<sub>3</sub> e NPD. Inoltre abbiamo investigato la disuniforme diminuzione di potenza ottica lungo l'area attiva di OLED sottoposti a test di stress elettrico. Questo fenomeno è stato correlato all'auto-riscaldamento e al profilo superficiale di temperatura dei dispositivi. Si è ipotizzata la presenza di un effetto di current crowding al fine di spiegare la presenza delle due disuniformi distribuzioni, ottica e termica.

Uno studio approfondito è stato realizzato sulle proprietà termiche dello strato di anodo degli OLED, confrontando dispositivi realizzati con diversi ossidi trasparenti conduttivi (TCO). In particolare si sono investigate le prestazioni e l'affidabilità di OLED con ossido di Stagno-Indio (ITO) e ossido di Zinco-Indio (IZO) come contatto di anodo. I dispositivi sono stati confrontati in termini di efficienza, resistenza termica e affidabilità. I risultati di questo studio hanno dimostrato che gli OLED realizzati con anodi di IZO hanno performance confrontabili con dispositivi con anodi di ITO, e mostrano una migliore dissipazione termica e maggiore tempo di vita.

La seconda parte del mio lavoro è legata allo sviluppo tecnologico di OTFT di tipo bottom e top contact, e allo studio della loro affidabilità.

Collaborando con il centro europeo di ricerca di microelettronica *IMEC*, abbiamo prodotto innovativi top contact OTFT realizzati con fotolitografia. Utilizzando un processo di wet etching, abbiamo realizzato dispositivi di tipo top contact con lunghezza di canale di  $10\mu$ m, ottenendo mobilitá maggiori di  $0.5 \text{cm}^2/\text{Vs}$ . Inoltre abbiamo sviluppato un innovativo processo che permette il patterning fotolitografico di contatti d'Argento sopra il semiconduttore organico, utilizzando dry etching mediante plasma. Tale processo di patterning stato dimostrato sia su substrato di silicio che di pellicola. Infine abbiamo investigato l'affidabilità di transistor organici basati sul Pentacene, e l'incapsulamento di questi dispositivi con il polimero Parylene C.

# Contents

| A                             | bstra | vii vii                                                                        |

|-------------------------------|-------|--------------------------------------------------------------------------------|

| Sc                            | omma  | rio xi                                                                         |

| C                             | ontei | ts xiii                                                                        |

| $\mathbf{Li}$                 | st of | Figures xv                                                                     |

| N                             | omei  | clature xix                                                                    |

| 1                             | Ger   | eral Introduction 1                                                            |

|                               | 1.1   | Organic Electronics                                                            |

|                               | 1.2   | OLEDs                                                                          |

|                               |       | 1.2.1 Intrinsic degradation on Alq3-based OLEDs 4                              |

|                               | 1.3   | OTFTs                                                                          |

|                               |       | 1.3.1 A bit of history $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ 8 |

|                               |       | 1.3.2 Basic Operation                                                          |

|                               |       | 1.3.3 Pentacene                                                                |

| 2 OLEDs optical investigation |       | Ds optical investigation 13                                                    |

|                               | 2.1   | PHOLED size and shape impact on light emission                                 |

|                               | 2.2   | Light emission distribution of solution processed OLEDs $\ldots \ldots 16$     |

| 3                             | Rel   | ability stress tests on Alq3/NPD OLEDs 21                                      |

|                               | 3.1   | Optical and electrical degradation of NPD/Alq3 OLEDs $\ldots$ 21               |

|                               | 3.2   | Phosphorescent OLEDs submitted to accelerated stress 33                        |

| 4                             | The   | mal study on Alq3/NPD OLEDs 43                                                 |

|              | 4.1                               | Evaluation of the junction thermal resistance                       | 43 |  |

|--------------|-----------------------------------|---------------------------------------------------------------------|----|--|

|              | 4.2                               | OLEDs surface thermal analysis                                      | 45 |  |

|              | 4.3                               | Thermal study on OLEDs with different anode materials $\ . \ . \ .$ | 48 |  |

| <b>5</b>     | OTFTs technology development      |                                                                     |    |  |

|              | 5.1                               | OTFTs processing                                                    | 55 |  |

|              | 5.2                               | Photolitographic top contact OTFTs                                  | 57 |  |

|              | 5.3                               | OTFT with wet etched Silver Top Contact                             | 61 |  |

|              | 5.4                               | OTFT with dry etched Silver Top Contact                             | 67 |  |

| 6            | Pary                              | Parylene encapsulation of Organic TFTs                              |    |  |

|              | 6.1                               | OTFT encapsulation                                                  | 75 |  |

|              | 6.2                               | Parylene-C as encapsulation coating                                 | 77 |  |

|              | 6.3                               | Stability test on encapsulated OTFTs                                | 78 |  |

| 7            | Con                               | clusions                                                            | 83 |  |

| $\mathbf{A}$ | Eval                              | uation of the thermal resistance                                    | 85 |  |

| в            | Surf                              | ace Treatment                                                       | 89 |  |

| С            | Organic Molecular Beam Deposition |                                                                     |    |  |

| D            | Spin                              | Coating Process Description                                         | 93 |  |

|              | D.1                               | Spin Coating Stages.                                                | 93 |  |

|              | D.2                               | Static Distribution, Dynamic Distribution                           | 95 |  |

|              | D.3                               | Spin Speed                                                          | 95 |  |

|              | D.4                               | Acceleration                                                        | 95 |  |

|              | D.5                               | Fume Exhaust                                                        | 96 |  |

| $\mathbf{E}$ | MA                                | 6 mask aligner                                                      | 97 |  |

| $\mathbf{F}$ | Pary                              | lene Deposition System                                              | 99 |  |

|              |                                   |                                                                     |    |  |

# List of Figures

| 1.1  | First flexible micro-processor                                             | 6  |

|------|----------------------------------------------------------------------------|----|

| 1.2  | Sony AM-OLED display                                                       | 7  |

| 1.3  | Sony display with bending conditions                                       | 7  |

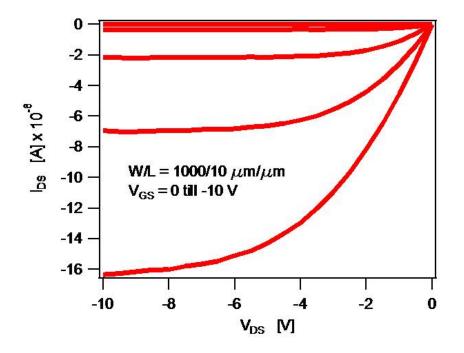

| 1.4  | OTFT transfer characteristic                                               | 9  |

| 1.5  | OTFT output characteristic                                                 | 10 |

| 1.6  | Structure of a molecule of Pentacene $(C_{22}H_{14})$                      | 11 |

| 2.1  | Light emission profiles of squared OLEDs                                   | 14 |

| 2.2  | Light emission profiles of circular OLEDs                                  | 15 |

| 2.3  | Optical comparison of OLEDs with different shape $\ldots \ldots \ldots$    | 16 |

| 2.4  | Light emission profiles of solution processed OLEDs                        | 17 |

| 2.5  | OLED with uneven light emission distribution $\ldots \ldots \ldots \ldots$ | 18 |

| 2.6  | Stereoscopic microscope picture                                            | 18 |

| 2.7  | OLED Emission spectrum at different current levels                         | 19 |

| 2.8  | OLED emission spectra of different devices                                 | 20 |

| 2.9  | Localized spectra profiles                                                 | 20 |

| 2.10 | Localized spectra profiles                                                 | 20 |

| 3.1  | Cross section of standard Alq3-NPD OLEDs                                   | 22 |

| 3.2  | Table of OLEDs layers thicknessess                                         | 22 |

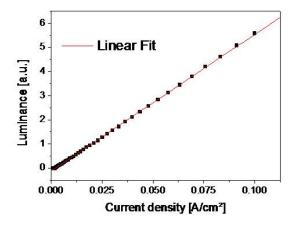

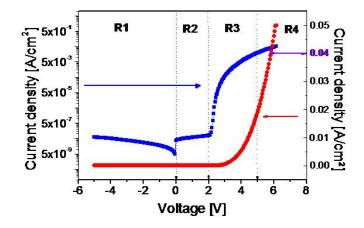

| 3.3  | Luminance as a function of current density                                 | 23 |

| 3.4  | OLED current density vs. voltage                                           | 23 |

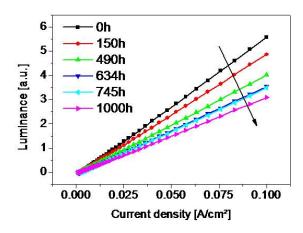

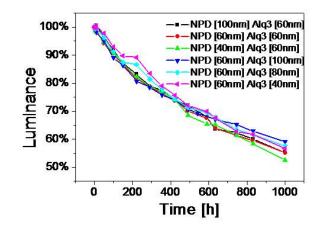

| 3.5  | Normalized luminance vs stress current at different ageing times .         | 25 |

| 3.6  | Optical degradation kinetics                                               | 25 |

| 3.7  | Light emission profiles before and after stress                            | 26 |

| 3.8  | Variation of the electrical characteristics of the OLED during current stress                           | 28 |  |

|------|---------------------------------------------------------------------------------------------------------|----|--|

| 3.9  | Variation of the capacitance of the OLED during current stress                                          | 29 |  |

| 3.10 | Capacitance hysteresis of stress OLEDs                                                                  | 30 |  |

| 3.11 | OLED band diagram model                                                                                 | 32 |  |

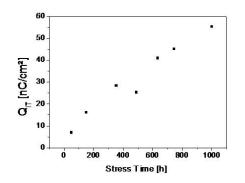

| 3.12 | Interface charge as a function of stress time                                                           | 32 |  |

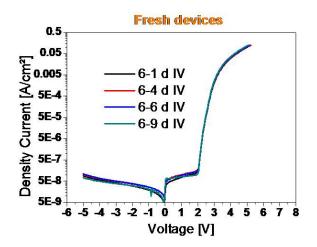

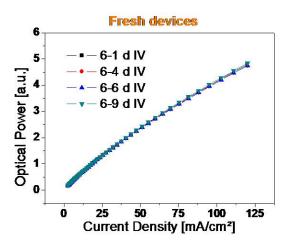

| 3.13 | Current density vs voltage for fresh devices                                                            | 33 |  |

| 3.14 | Optical power vs current density fo fresh devices                                                       | 34 |  |

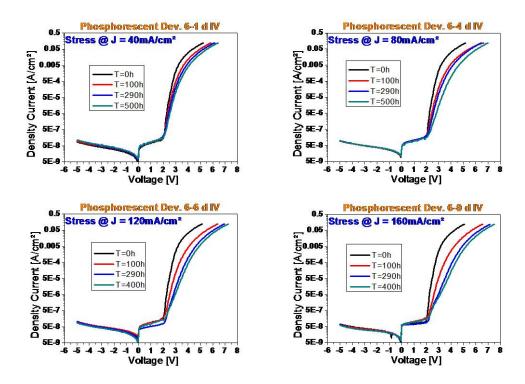

| 3.15 | Current vs voltage curves for phosphorescent OLEDs under stress                                         | 35 |  |

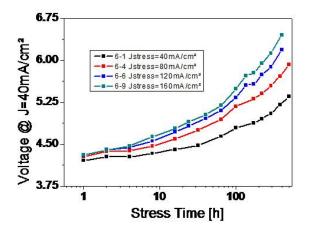

| 3.16 | 6 Voltage rise during stress time                                                                       |    |  |

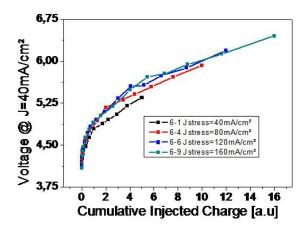

| 3.17 | Voltage rise during stress time as a function of injected carriers .                                    | 36 |  |

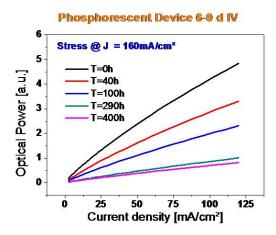

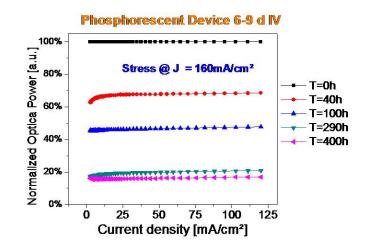

| 3.18 | Optical power plotted as a function of current density                                                  | 37 |  |

| 3.19 | Normalized Optical Power plotted as a function of current density, at different stress times            | 37 |  |

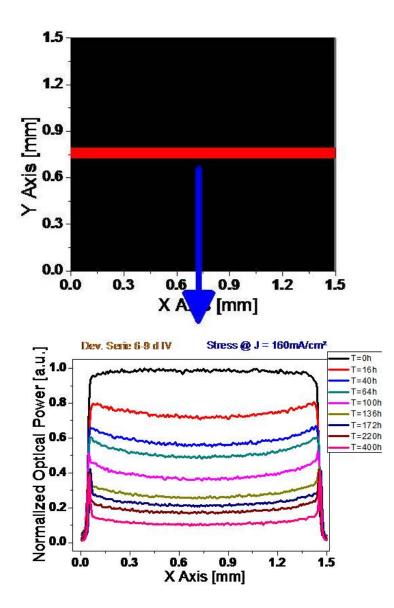

| 3.20 | Light emission profiles during accelerated stress test                                                  | 38 |  |

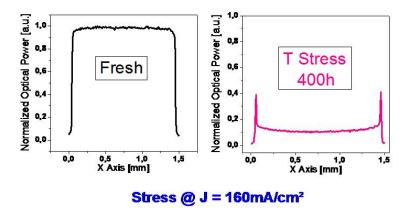

| 3.21 | Longitudinal Light Emission Profile                                                                     | 39 |  |

| 3.22 | Longitudinal Light Emission Profile before and after stress test                                        | 40 |  |

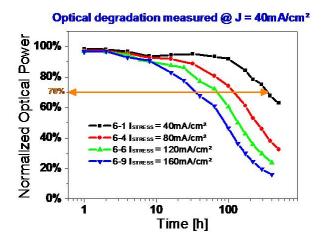

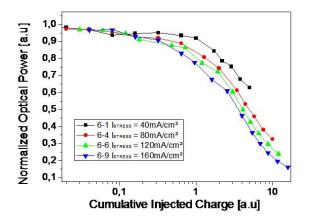

| 3.23 | Optical degradation kinetics as a function of stress time                                               | 40 |  |

| 3.24 | Optical degradation kinetics as a function of injected charge                                           | 40 |  |

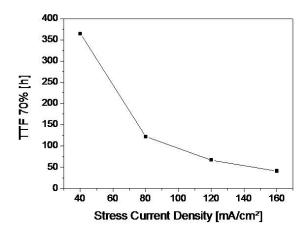

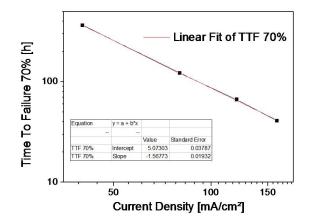

| 3.25 | Time to failure as a function of stress current density                                                 | 41 |  |

| 3.26 | Time to failure in a log-log scale                                                                      | 41 |  |

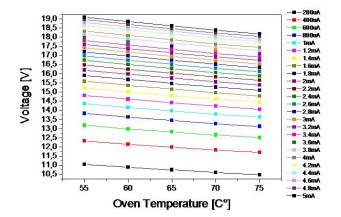

| 4.1  | Voltage mapping as a function of junction temperature $\ldots$ .                                        | 44 |  |

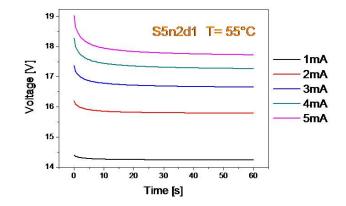

| 4.2  | Voltage thermal transients                                                                              | 45 |  |

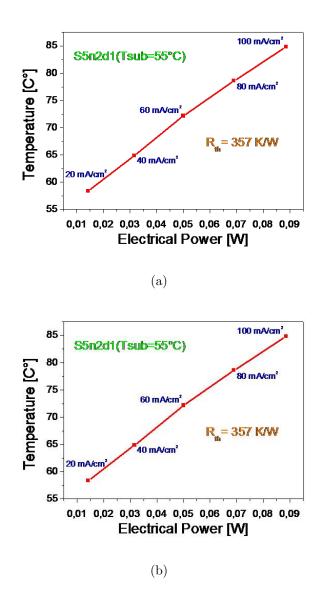

| 4.3  | Junction temperature vs current density and electrical power                                            | 46 |  |

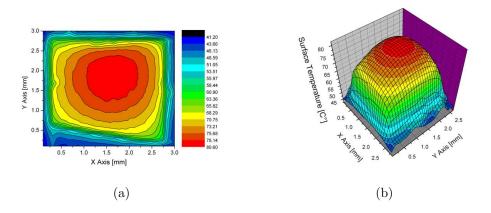

| 4.4  | Surface temperature profile                                                                             | 46 |  |

| 4.5  | Light Emission Profile                                                                                  | 47 |  |

| 4.6  | Comparison between temperature and light emission along the active area of a $0.5$ cm <sup>2</sup> OLED | 47 |  |

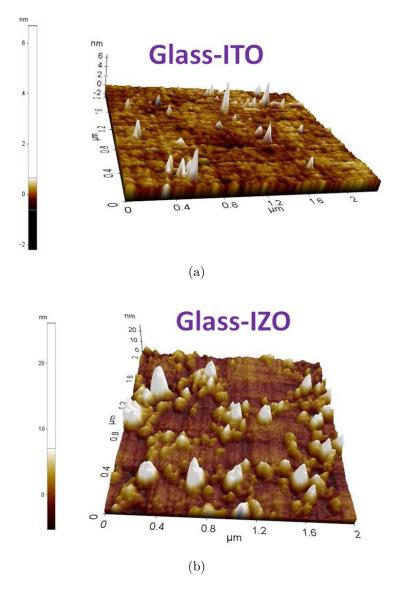

| 4.7  | AFM images of glass substrates                                                                          | 49 |  |

| 4.8  | Luminance vs current density characteristic of devices with ITO and IZO anode                           | 50 |  |

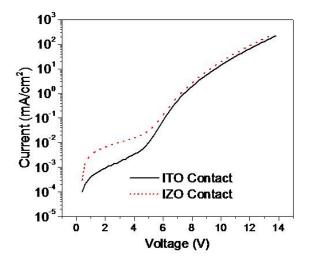

| 4.9  | Current density vs Voltage characteristic of devices with ITO and IZO anode                             | 51 |  |

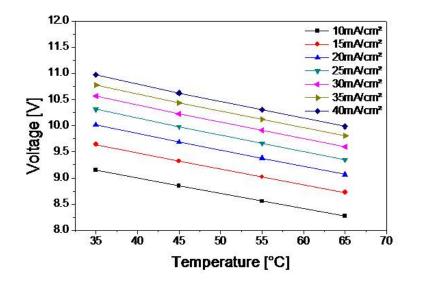

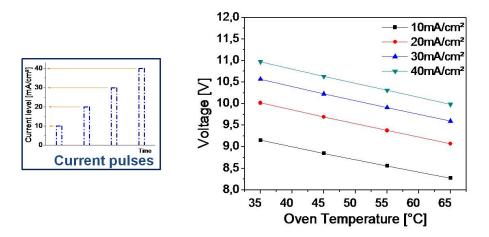

| 4.10 | 10 Voltage vs oven temperature map at different bias current levels .                                   |    |  |

|------|---------------------------------------------------------------------------------------------------------|----|--|

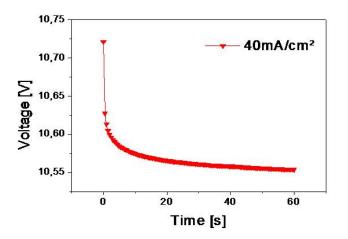

| 4.11 | OLED voltage transient                                                                                  | 52 |  |

| 4.12 | OLEDs thermal resistance histogram                                                                      | 53 |  |

| 4.13 | ITO and IZO OLEDs optical degradation                                                                   | 54 |  |

| 4.14 | Forward voltage increase during accelerated electrical stress $% \left( {{{\bf{x}}_{{\rm{s}}}} \right)$ | 54 |  |

| 5.1  | OTFT structures                                                                                         | 56 |  |

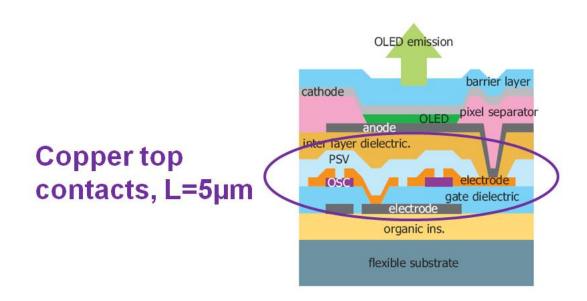

| 5.2  | Sony OLED display cross-section (2007)                                                                  | 58 |  |

| 5.3  | Sony OLED display cross-section (2009)                                                                  | 58 |  |

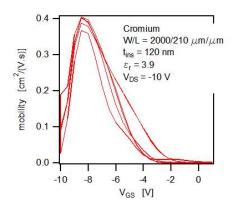

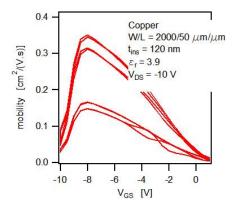

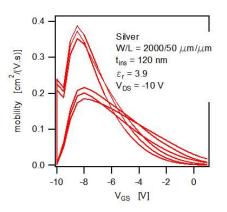

| 5.4  | Mobility curves of Chromium OTFTs                                                                       | 59 |  |

| 5.5  | Mobility curves of Copper OTFTs                                                                         | 59 |  |

| 5.6  | Mobility curves of Silver OTFTs                                                                         | 60 |  |

| 5.7  | Top contact OTFT structure                                                                              | 61 |  |

| 5.8  | Wet Etched Top contact OTFT flow                                                                        | 62 |  |

| 5.9  | Development issue                                                                                       | 63 |  |

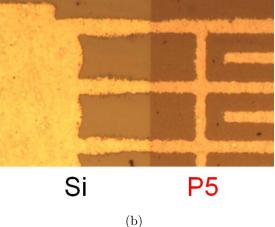

| 5.10 | Silver wet etching tests                                                                                | 64 |  |

| 5.11 | Silver wet etched top contact OTFTs                                                                     | 65 |  |

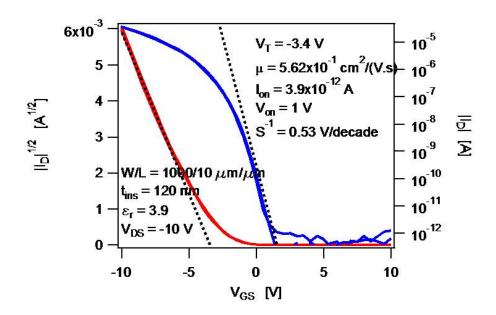

| 5.12 | Output characteristic of a Silver top contact OTFT patterned by wet etching                             | 66 |  |

| 5.13 | Transfer characteristic of a Silver top contact OTFT patterned by wet etching                           | 66 |  |

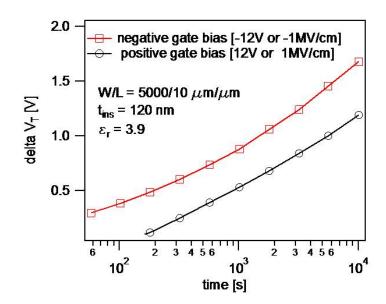

| 5.14 | Bias stress on a Silver top contact OTFT patterned by wet etching                                       | 67 |  |

| 5.15 | Basic Top contact OTFT structure                                                                        | 68 |  |

| 5.16 | Top contact OTFT structure with a protective layer                                                      | 68 |  |

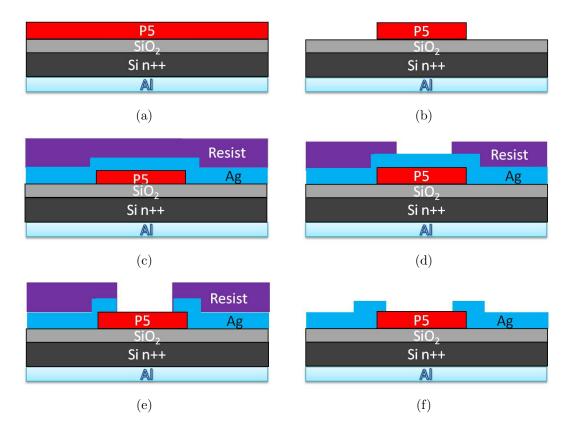

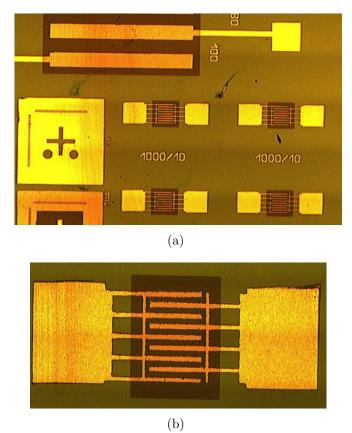

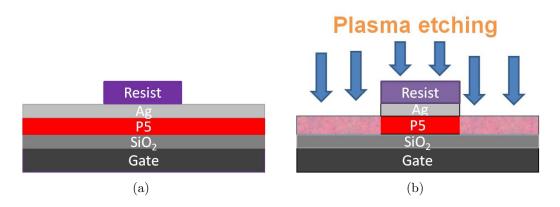

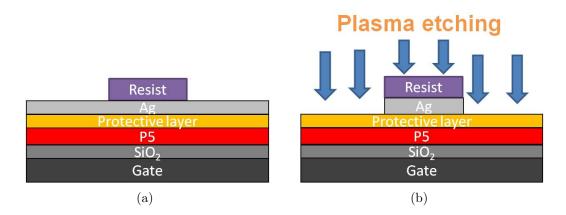

| 5.17 | Dry Etched Top contact OTFT flow                                                                        | 70 |  |

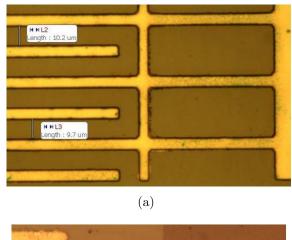

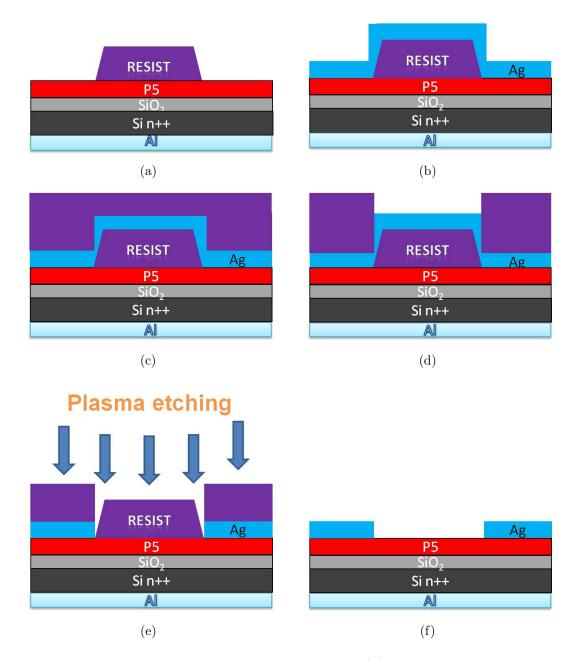

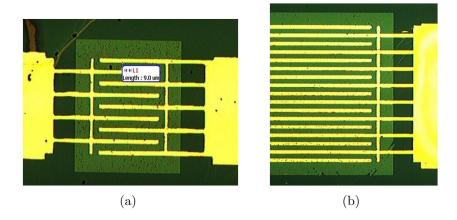

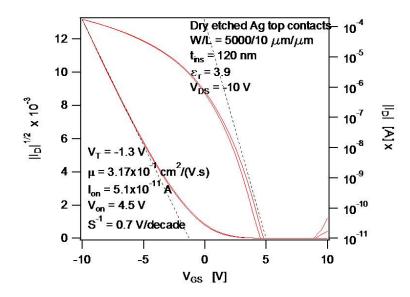

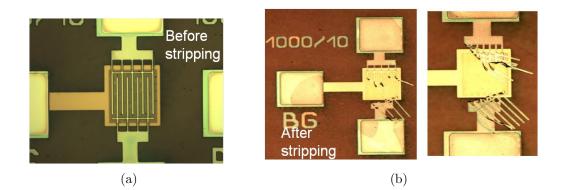

| 5.18 | Dry etched top contact OTFTs                                                                            | 71 |  |

| 5.19 | Transfer characteristic of a dry etched top contact OTFT                                                | 71 |  |

| 5.20 | Bad patterning of top contact OTFTs on foil                                                             | 72 |  |

| 5.21 | Transfer characteristic of a dry etched top contact OTFT on PEN foil                                    | 73 |  |

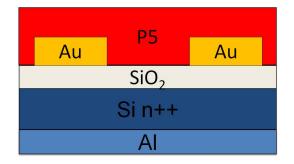

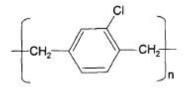

| 6.1  | Bottom contacts OTFT                                                                                    | 76 |  |

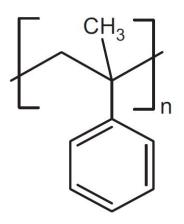

| 6.2  | Structure of Parylene-C                                                                                 | 77 |  |

| 6.3  | Parylene-C                                                                                           | 77  |

|------|------------------------------------------------------------------------------------------------------|-----|

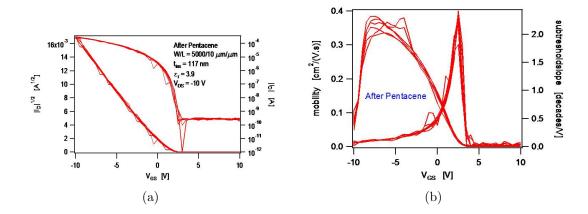

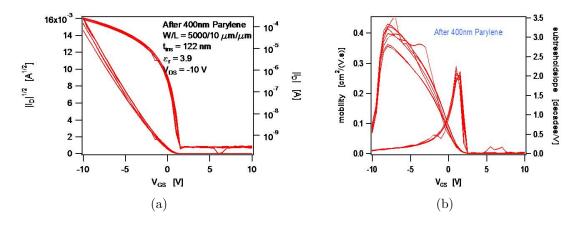

| 6.4  | OTFT curves after Pentacene evaporation                                                              | 79  |

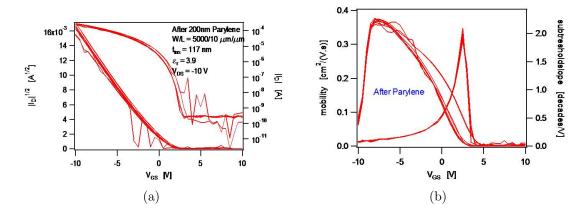

| 6.5  | OTFT curves after Paralyne coating                                                                   | 79  |

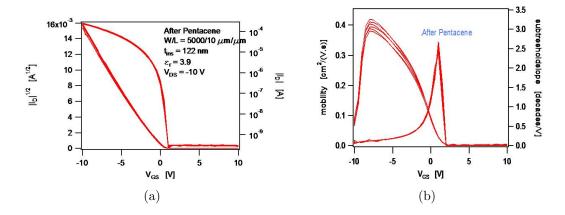

| 6.6  | OTFT curves after Pentacene evaporation                                                              | 80  |

| 6.7  | OTFT curves after Parylene coating                                                                   | 80  |

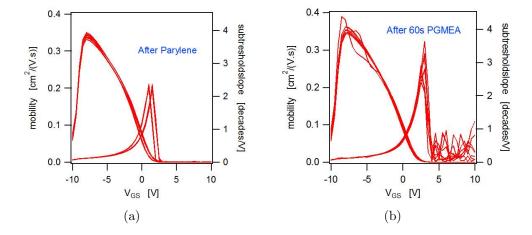

| 6.8  | Mobility curves after test in PGMEA                                                                  | 81  |

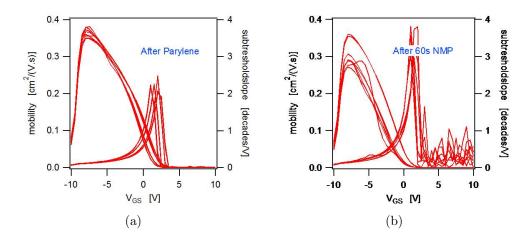

| 6.9  | Mobility curves after test in NMP                                                                    | 81  |

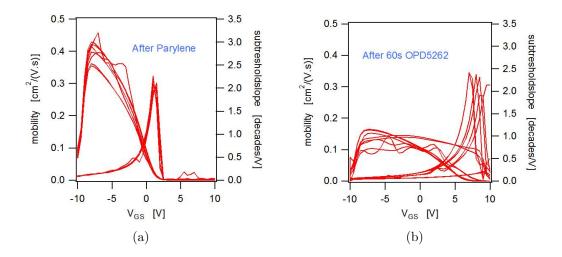

| 6.10 | Mobility curves after test in OPD5262                                                                | 82  |

| A.1  | Example of calibration phase                                                                         | 86  |

| A.2  | Example of temperature evaluation phase                                                              | 87  |

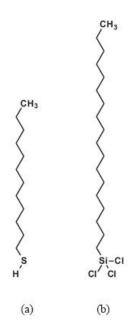

| B.1  | Thiol and OTS structural formula                                                                     | 90  |

| B.2  | $P \alpha MS$ structural formula                                                                     | 90  |

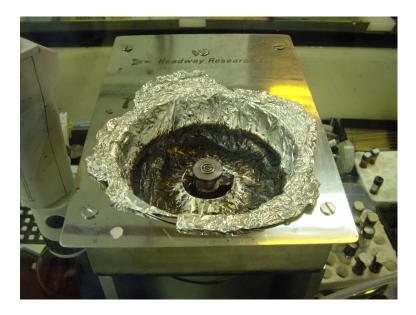

| D.1  | The Spin Coater with interchangeable support.                                                        | 93  |

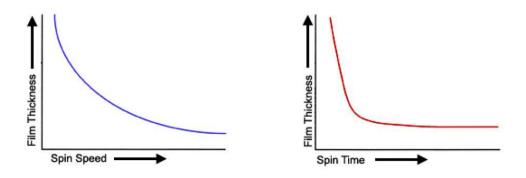

| D.2  | Typical Film Thickness vs Spin Speed and Film Thickness vs Spin Time characteristics.                | 94  |

| D.3  | Typical Thickness Uniformity vs Exhaust Volume and Film Thickness vs Exhaust Volume characteristics. | 94  |

| E.1  | Mask Aligner MA6                                                                                     | 97  |

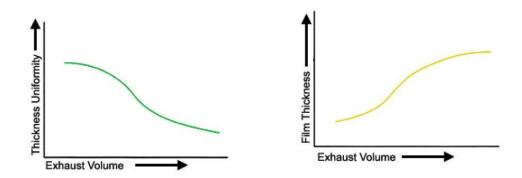

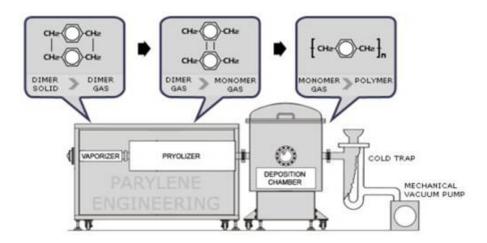

| F.1  | Parylene Deposition Process                                                                          | 100 |

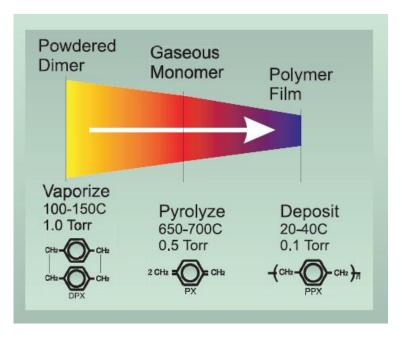

| F.2  | Parylene coating system                                                                              | 101 |

### Nomenclature

#### Chemicals

| a - Si | Amorpl | hous Silicon, | page | 5 |

|--------|--------|---------------|------|---|

|--------|--------|---------------|------|---|

- Ag Silver, page 59

- Al Aluminum, page 49

- Alq3 tris(8-hydroxyquinoline)aluminium, page 4

- Ar Argon, page 67

- Au Gold, page 55

- $C_{22}H_{14}$  Pentacene, page 10

- C60 Buckminsterfullerene, page 8

- $CF_4$  Carbon Tetrafluoride, page 67

- Cr Chromium, page 59

- Cu Copper, page 59

- CuPc Copper Phthalocyanine, page 4

- DIW Deionized Water, page 56

- GaN Gallium Nitride, page 85

- HFEs Hydrofluoroethers, page 60

- IPA Isopropanol, page 56

- $SiO_2$  Silicon Dioxide, page 55

- ITO Indium Tin Oxide, page 44

- *IZO* Indium Zinc Oxide, page 44

- LiF Lithium Fluoride, page 49

- MoOx Molibdenum Oxide, page 69

- NMP N-Methyl-2-pyrrolidone, page 81

NPDN,N´-Di-[(1-naphthyl)-N,N´-diphenyl]-1, 1´-biphenyl)-4, 4´-diamine, page 21

- $O_2$  Oxygen, page 67

- $O_3$  Ozone, page 89

- OTS Octadecyl Trichloro Silane, page 89

$P\alpha MS$  poly(alpha-methyl styrene), page 89

- Pd Palladium, page 57

- PEN Polyethylene naphthalate, page 72

- PES Polyethersulfone, page 57

- PGMEA 2-[1-methoxy]propyl acetate, page 80

- PVP Poly-vinyl-pyrrolidone, page 72

- Si Silicon, page 5

- ZnO Zinc Oxide, page 48

- ZnS Zinc Sulfide, page 69

#### Other Symbols

- $\varepsilon_0$  Vacuum dielectric constant, page 9

- $\varepsilon_{ins}$  Relative dielectric constant, page 9

- $C_{ins}$  Capacitance per unit area, page 9

- $I_{ds}$  Drain-source current, page 9

- LEP Light Emission profile, page 24

- $R_{th}$  Junction Thermal Resistance, page 43

- $T_i$  Junction Temperature, page 43

- $TTF_{70\%}$  70% time to failure, page 53

- $V_{ds}$  Drain-source voltage, page 78

- $V_{gs}$  Gate-source voltage, page 78

#### Acronyms

AFM Atomic Force Microscopy, page 49

AMdisplay Active Matrix display, page 6

- BL Blocking Layer, page 49

- CCD Charge-Coupled Device, page 17

- CVD Chemical Vapour Deposition, page 55

- EML EMissive Layer, page 49

- ETL Electron Transport Layer, page 4

- FOLED Flexible Organic Light Emitting Diode, page 75

- HIL Hole Injection Layer, page 4

- HIL Hole Injection Layer, page 49

- HTL Hole Transport Layer, page 4

- *IC* Integrated Circuit, page 5

- MOSFET Metal Oxide Field Effect Transistor, page 9

- OMBD Organic Molecular Beam Deposition, page 5

- $OTFTs\,$  Organic Thin Film Transistors, page 5

- $OVPD\,$  Organic Vapour Phase Deposition, page 2

- PhOLED Phosphorescent Organic Light Emitting Diode, page 13

- RF Radio Frequency, page 67

- RFID Radio Frequency IDentification, page 6

- RMS Roughness Measurement System, page 49

- SAM Self Assembled Monolayer, page 89

- TCO Transparent Conductive Oxide, page 49

- $TFT\;$  Thin Film Transistor, page 5

- UV Ultra Violet, page 61

- VDP Vapour Deposition Polymerisation, page 77

# Chapter 1

### **General Introduction**

In 1976 the Alan MacDiarmid sowed the seed of a revolutionary technology by proving the first conducting *polymer* [1]. Thanks to this discovery, he was invested with the Nobel prize for chemistry. Years later, when the first organic transistor was built, the applied physics tried to investigate the utility of these materials for a wide range of applications. The research field concerning the study of devices based on conductive polymers took the name of  $Organic^1$  Electronics.

In this first chapter it is provided a small introduction to organic electronics and to the organic devices that are more relevant within this work, i.e. OLEDs and OTFTs.

### **1.1 Organic Electronics**

Although crystalline silicon (Si) has been the dominating technology in the semiconductor industry over the last decades, semiconducting thin film technologies are better suited to realize some specific applications. Processing in crystalline Si technology always has to start from the high quality crystalline Si wafer, which limits the size of the application and the versatility. Semiconducting thin films on the other hand, can be deposited on such a arbitrary substrate of arbitrary size, enabling applications such as large area displays or solar cells covering complete windowpanes. Organic semiconductor technology is one of the available thin film technologies with the additional advantage that the low deposition temperatures allow the use of flexible substrates.

Since semi-conduction in organic crystals and polymers films has been proved (between the 1950s and 1970s [2, 3]), organic conjugated macromolecules and polymers have generated a large scientific interest. These materials combine the

<sup>&</sup>lt;sup>1</sup>The name "organic" is an historical name, dating back to  $19^{th}$  century, when it was believed that organic compounds could only be synthesised in living organisms through vis vitalis. Namely an organic compound is every member of a large class of chemical compounds whose molecules contain carbon, with exception of carbides, carbonates, carbon oxides and gases containing carbon. The dividing line between organic and inorganic is contended and historically arbitrary; generally speaking, however, organic compounds are defined as those compounds which have carbon-hydrogen bonds.

ability to conduct electronic charge, typical of semiconductors and metals, with specific plastic properties like reduced cost and mechanical flexibility. Moreover, organic materials offer several processing advantages over conventional semiconducting materials, including a reduced thermal budget and the possibility to process on the top of inexpensive substrates, such as polymers and glass. The perspective of low cost device fabrication on large, flexible substrates is clearly not achievable by using the standard inorganic semiconductor processing technology. Instead, manufacturing electronic devices on large substrates will most likely be based in printing-based techniques (e.g. screen printing, micro contact printing, ink jet printing, etc.), stamping, or low vacuum deposition methods, such as organic vapour phase deposition (OVPD). The lower processing costs entail lower cost for the finalized device. An important market for devices with massively low cost per unit could be the health one. Due to the safety requirements, single-use devices are highly desirable, without forgetting the bio-compatibility of the most of these polymers, which clearly makes them useful for specific bio-sensing applications.

Moreover, organic materials are characterized by a huge variation in structure and properties, and this adaptability is one of the principal reason for studying their application to electrical engineering problems. These remarkable materials still represent an enormous range of challenging in synthesis, and structure for chemists, such as the wide choice of their molecular structure and the possibility to incorporate side-chains or grains with specific behaviour into the bulk material or on the surface, enabling the production of films with specific physical and chemical properties [4]. Foe example many molecules and polymers have pronounced optical qualities that can be adjusted by modifications of chemical structure. Electrical properties such as conductivity are also dependent on molecular design. Thanks to this flexible, and/or optically transparent polymers and oligometric order of the new scenes to electronic devices in the next future. Totally new and innovative applications can be realized by achieving sufficient device performance at considerably reduced cost. Organic solar cells is for instance one of the promising research field of organic electronics [5]. Solar cells have been investigated for a long period of time, using several inorganic materials. Although organic solar cells most likely will never be able to compete with inorganic solar cells in terms of efficiency, they actually have a few advantages compared to their inorganic counterparts. They can be produced more cheaply, such that the price per unit energy generated by the cell may turn out to be lower than that of inorganic solar cells. Then, the absorption coefficient of organic semiconductors is much larger than that of inorganic semiconductors. Moreover, organic solar cells can be reproduced on flexible substrates, which allows for the integration of solar cells on textiles. Other *organic* fields of research are related to: Organic Light emitting Diodes (OLEDs, see section 1.2), organic thin film transistors (OTFTs, see section 1.3), organic lasers, organic sensors and other innovative devices. More complex organic designs, like flexible electronic circuits, photovoltaic panels and Radio Frequency IDentification (RFID) tags are under development, while OLEDs are going to conquer the lighting and the display worldwide market.

### 1.2 OLEDs

Research in the optoelectronic properties of organic material has already been going on for nearly 100 years, starting with the publication of the discover of photo-conductivity in organic crystals in 1906 [6]. The first actual OLED, based on anthracene, was fabricated in 1963 (even still with extremely high operating voltage). Nevertheless, for a real breakthrough we have to wait till 1987, with the work by Tang and Van Slyke about the performance of green emitting thin film OLEDs based on the small organic molecule tris(8-hydroxy quinoline) (Alq3) [7]. In 1990, Bradley described the first polymer OLED, based on poly(p-phenylene vinylene) (PPV) [8]. It showed that was possible to spin coat a precursor polymer onto the transparent conducting indium-tin-oxide (ITO) anode substrate, thermally converting the precursor to PPV, and finally evaporating a thin Aluminium cathode layer on the PPV. Since then, the competition between small-molecule OLEDs and solution processed OLEDs continues in parallel. Improvements, also in terms of reliability, have been terrific: from devices with a lifetime in air of less than 1 minute, to green OLEDs capable to operate continuously for over 20 thousands hours at a brightness of 100  $cd/m^2$  [9]. Moreover, these devices can count on several potential advantages:

- Relative easy and low cost fabrication

- Opportunity to be solution processed, or evaporated on any kind of substrate

- Wide viewing angle

- Great brightness

In the last years, several multinational companies (i.e. Sony, Samsung) have started to show previously passive, and subsequently active matrix displays based on OLEDs. Small OLED-based displays are already commercially available. usually in mobile applications, such as in cell phones, mp3-players, etc. Moreover, OLEDs are suitable for flexible displays not only because they have a thin, solid-state and flexible structure, but also because their wide viewing angle allows them to be viewed even when they are flexed. Other advantages of OLEDs are their wide colour gamut and quick response times, enabling full-colour smooth moving images even on flexible films. OLED technology is a promising candidate for the front plane of a high-quality flexible display and its performance can be enhanced when the OLED is driven in active-matrix (AM) operation. In 2005 Samsung presented a 40-inch OLED TV display, demonstrating the proof of principle for a large OLED display. Recently, Organic Light-Emitting Diodes have demonstrated efficiencies as high as 102 lm/W, demonstrating a path for future adoption of OLEDs as light sources [10]. Therefore, another market segment in which OLEDs could come into play, is ambient lighting. OLEDs provide a technology for large area diffuse light sources, while leaving the freedom to design panels in any kind of shape [11]. Whereas OLED displays consist of an array of small red, blue and green pixels, OLED lighting applications require an

homogeneous, pleasant white light, i.e. a required colour rendering index of at least 80. In addition, lighting requires high brightnesses (roughly 1000 cd/m<sup>2</sup>, as compared to 100 cd/m<sup>2</sup> for display applications), and OLED lighting panels need to be highly efficient. The luminous efficacy should be preferably larger than 50 lm/W. Therefore, it is clear that OLED lighting imposes different and more demanding requirements than OLED displays. One of the most critical part is nowadays the emitter used for the blue part of the spectrum, especially in terms of operational lifetime.

In the next paragraph we report the state of art of intrinsic degradation in Alq3-based OLEDs. An extensive study of this relevant topic is then reported in chapter 3.1.

#### 1.2.1 Intrinsic degradation on Alq3-based OLEDs

Since the report on the first efficient OLED by Tang and Van Slyke in 1987 [7], tris(8-hydroxyquinoline)aluminium (Alq3) has been one of the most widely adopted emitter material in OLED technology. Alq3 can be used for the realization of devices emitting in the green-red spectral region. The degradation of OLEDs during operation time can be strongly determined by the worsening of the properties of Alq3 layer. In fact, Alq3-based OLEDs can be affected by several failure mechanisms, such as the formation of dark spots [12, 13], catastrophic failures [14], and long-term intrinsic degradation that is responsible for the OLED brightness decrease over time, without any visible deterioration of the active area. Over the last decade, the first two issues have been overcome, by both using improved sealing techniques and depositing organic materials with high purity degree. On the other hand, intrinsic degradation still remains an open issue, which is worth of investigation, even though several hypotheses on the origins of this kind of degradation have been already proposed. For a long time the morphological instability of the Hole Transport Layer (HTL) has been depicted as one of the main mechanism responsible for OLED degradation [15, 16]. This resulted into the research of hole transport materials with high glass transition temperatures  $(T_G)$  [17, 18]. These studies led to the synthesis of several important OLED materials. Although it has been demonstrated that the use of HTLs with high  $T_G$  increases the device robustness to high temperature environments, it does not impact its operational stability, especially at room temperature [19, 20]. Furthermore, OLED stability has been chased by different methods, such as the introduction of a Copper Phthalocyanine (CuPc) buffer layer between the ITO and the Hole Injection Layer (HIL), and the doping of the HTL. Nevertheless, the argued reasons behind the success of these technological solutions were often incomplete and sometimes contradictory. In particular, the key issue concerned the localization of the degradation processes, in the HTL or in the Electron Transport Layer (ETL). A turning point was set by Aziz that observed that in Alq3 significant photo-luminescence decrease is observed during holes injection, while the photo-luminescence stays almost constant during electrons injection [21]. These results, therefore, provided strong evidence that injection of holes into the Alq3 layers can be responsible for the optical degradation of OLEDs. The enhanced stability of OLEDs developed inserting a mixed layer at the HTL-Alq3 interface,

confirmed this hypothesis, suggesting that OLEDs degradation mainly takes place at or close to that interface. Furthermore, the long-term luminance decrease has been related to the instability of the Alq3 cationic species [22] and to the accumulation of positive charge at the emitting OLED interface [23, 24]. The instability of the cationic species induces the creation of by-products that have been related to a decrease in device electro luminescence. Moreover, it has been shown that these by-products play different roles as charge traps, electron-holes recombination centres and fluorescence quenchers. However, holes injection into the Alq3 layer still appears to be one of the main factors responsible for OLED optical degradation. This hypothesis is confirmed by the fact that cyclic voltammetry on Alq3 in solutions showed the irreversibility of the Alq3 oxidation process [25].

### 1.3 OTFTs

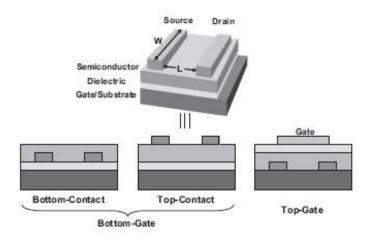

For more than two decades now, organic thin-film transistors (OTFTs) based on conjugated polymers, oligomers, or other molecules have been studied as a possible alternative to more traditional, mainstream thin-film transistors (TFTs) technology, based on inorganic materials. Traditional crystalline Silicon (Si) fieldeffect transistors are the leader technology in semiconductor industry. Nevertheless, there are application where crystalline Si is not the best option. Crystalline wafer limits the substrate size and the versatility, being a rigid base. On the contrary thin-film semiconductors do not come in wafers, but they can be deposited on arbitrary sized substrates. Although Crystalline Si performance and cost per transistor cannot be achieved by thin-film based devices, by using this technology unique products can be manufactured. The most established thin film technology is Amorphous Si (a-Si). Another emerging thin-film technology is the one related to metal oxide semiconductors. These materials showed high mobilities (up to 100 cm<sup>2</sup>/(Vs), versus 1 cm<sup>2</sup>/(Vs) for a-Si), low temperature deposition (availability of flexible substrates) and optical transparency.

Organic semiconductor technology is clearly another competitor of thin-film technologies. Integrated circuits (ICs) fabricated using organic TFTs (OTFTs), offer the potential of enabling low-cost processing, flexible, adequately performing logic circuits (an example of microprocessor on foil is reported in fig. 1.1). As mentioned before, organic semiconductors can be processed at low temperatures, allowing deposition on different kind of substrates (Silicon, glass, polymers, textiles). An organic semiconductor layer can be grown virtually on any kind of surface if properly treated. No epitaxial growth on a crystalline substrate is required. A wide range of deposition methods can be used (OMBD, CVD, etc). Moreover, OTFTs may be solution-processed, allowing the fabrication of large-area devices. Nowadays the mobility of OTFTs and of a:Si TFTs are comparable. Nevertheless, it is foreseen that OTFTs should be patterned by printing, potentially lowering down considerably the price of this technology compared to the a:Si one [26]. Therefore, Organic thin-film transistors have been recognized as a breakthrough technology for next generation electronics due to their unique advantages, such as light-weight, flexibility, and low-cost fabrication [27, 28]. Recently it has been proved that also a:Si TFTs can be processed at around 100°C on a flexible substrate, with good off-current and mobility, and great environmental stability [29]. However, low temperature processed a:Si are affected by low bias stability due to the huge amount of unsaturated bonds that can act as traps. On the contrary organic semiconductors do not show any unsaturated bonds.

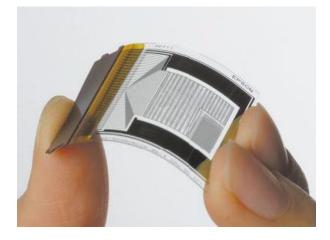

Figure 1.1: The industry's first flexible 8-bit asynchronous microprocessor by Epson.

To manufacture an organic TFT, the organic semiconductor and the other materials required (gate electrode, gate dielectric, source and drain contacts) are deposited as thin layers on the surface of an electrically insulating substrate, such as glass or plastic foil. The total thickness of the device can be less than 100 nm. Several methods exist for the deposition and patterning of the individual layers of the TFT. Gate electrodes and source and drain contacts are often prepared using inorganic metals. Non-noble metals, e.g aluminium or chromium, are suitable for the gate electrodes while noble metals, most notably gold, are a popular choice for the source and drain contacts, since they tend to provide better contact performance than other metals. The gate dielectric material must be compatible with the substrate used, and the thickness is a compromise between the desire to work at low voltage levels, and the need of a low leakage current.

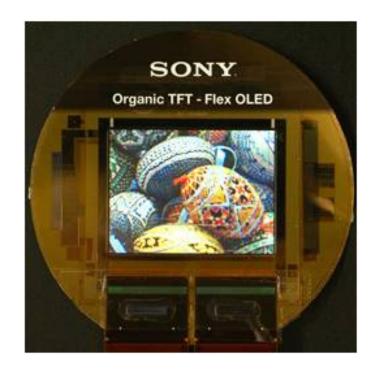

Organic transistors are potentially useful for applications that require electronic functionality with low or medium complexity distributed over large areas on unconventional substrates, i.e. applications in which the use of silicon devices and circuits is technically or economically not feasible. Potential applications include postage stamps [30, 31], radio frequency identification (RFID) tags [32], "smart" cards [4, 33, 34]. OTFTs can be processed on plastic films (like PEN or Parylene) achieving field-effect mobility higher than  $0.1 \ cm^2/Vs$  and a current on/off ratio greater than  $10^5$ . This means that they can be used in an Active-Matrix (AM) display allowing the production of thin, flexible displays [35, 36, 37]. The entry of these products in the worldwide market is imminent (see in Fig. 1.2 and 1.3, some *Sony* prototypes of flexible AM-OLED display). Strategies for increasing the performance of organic TFTs include further improvements in the carrier mobility of the organic semiconductor by synthesizing new materials, improving purification and enhancing the molecular order in the semiconductor layer [38], and scaling of the organic transistor dimensions.

Figure 1.2: Sony full-color top-emission QQVGA AM-OLED display.

Figure 1.3: Sony OTFT-OLED display operating with bending condition.

### 1.3.1 A bit of history

The first organic TFT with the small molecule Pentacene as organic semiconductor, was first reported in 1992 [39]. In 1995, an OTFT was fabricated by using the n-type semiconductor *Buckminsterfullerene* (C60), resulting in an electron field-effect mobility of almost 0.1  $cm^2/(Vs)$  [40]. In the same year, the Philips group published the worldwide first results of an organic integrated circuits [41]. For the first time, OTFTs were sufficiently good performing to construct logic gates that displayed voltage amplification. Moreover the fabrication of a ring oscillator demonstrated that these logic gates could switch subsequent gates and perform logic operations. This breakthrough delineated the start of a new era in the field of organic electronics, as it became clear that OTFTs might provide a useful technology for certain applications, accepting a relatively low performance, but at the same time requiring low cost. Since 1992 we have observed a constant increase in mobility, which was achieved either by improving the processes used for the fabrication of the transistors and by synthesizing new organic materials. In 1999, Pentacene OTFT were fabricated with a field-effect mobility in excess of  $2cm^2/(Vs)$  [42]. In terms of mobility, OTFTs became more performing than amorphous silicon TFTs. In order to obtain these high mobility values, the morphology of the Pentacene film was optimized by applying surface treatments. Thanks to the efforts of many research groups working in the field of organic electronics, the OTFT performance steadily increased. In 2003, the 3M research group showed that a Pentacene OTFT mobility in excess of  $5cm^2/Vs$  could be systematically fabricated [32]. Even so, the success of OTFTs is still not guaranteed. Potential obstacles are yield, lifetime, and insufficiently fast progress in low-cost production technologies (printing and solution processed OTFTs). In addition, other thin film technologies like Silicon, polysilicon, chalcogenide, Zinc Oxide (ZnO), and carbon nanotubes have progressed concerning the mobility as well as low deposition temperatures.

### 1.3.2 Basic Operation

Traditional Si transistors operate by exploiting the inversion of the channel. By increasing the gate-source voltage the channel is depleted and consequently a layer of minority carriers is formed. In this regime the transistor is on and applying a voltage between drain and source it is possible to have a current flow. On the contrary, if we increase the gate-source voltage in the other direction we get the creation of an accumulation layer with majority carriers, and applying a voltage between drain and source we have no current flow due to the double reverse biased pn junctions. Instead an organic transistor usually operates in accumulation. By increasing in the proper way the gate-source voltage, we get the creation of an accumulation layer that allows the flow of holes (in a p-OTFT) between the electrodes, if subjected to a voltage bias. If the gate voltage is increased in the other direction, the organic semiconductor gets depleted and can create an inversion layer. Nevertheless the flowing current is limited because most of organic semiconductors transports only one kind of carrier. In order to limit the parasitic currents , the thickness of the semiconductor is usually kept

small (30 to 50nm). Despite that, OTFTs can be modelled by using the inorganic typical transistor equations [43]. Two curves are usually measured to characterize a field-effect transistor: the transfer characteristics and the output characteristics.

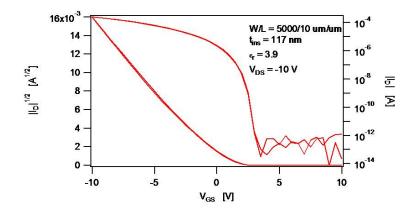

Figure 1.4: OTFT transfer characteristic in the linear regime.

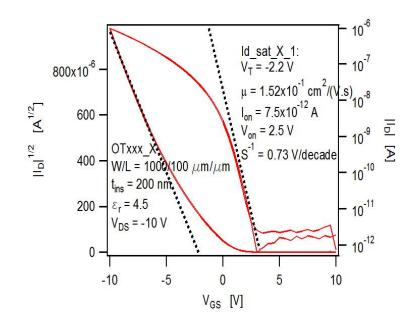

In order to measure the transfer characteristic, the drain-source voltage is kept constant, while we have a variation of the gate-source voltage. Depending on the drain-source voltage, the transistor is operating in the linear or in the saturation regime. Fig. 1.4 shows the transfer characteristics of a p-type organic transistor, measured in the saturation regime.

Assuming the conventional gradual channel approximation, the current  $I_{ds}$  measured between drain and source in the saturation and linear regime can be described as following:

$$I_{ds} = -\frac{W}{2L}\mu C_{ins}(V_{gs} - V_t)^2, \qquad |V_{ds}| > |V_{gs} - V_t| \qquad (1.3.1)$$

$$I_{ds} = -\frac{W}{L}\mu C_{ins}(V_{gs} - V_t - \frac{V_{ds}}{2})V_{ds}, \qquad |V_{ds}| < |V_{gs} - V_t| \qquad (1.3.2)$$

where W is the channel width, L the channel length,  $\mu$  the mobility,  $C_{ins}$  is the capacitance of the gate dielectric per unit area

$$C_{ins} = \frac{\varepsilon_0 \varepsilon_{ins}}{t_{ins}} \tag{1.3.3}$$

where  $\varepsilon_0$  is the vacuum dielectric constant,  $\varepsilon_{ins}$  is the relative dielectric constant, and  $t_{ins}$  is the thickness of the dielectric. Finally,  $V_t$  is the threshold voltage. For silicon MOSFETs, the threshold voltage  $V_t$  is defined as the minimum gate-source voltage required to induce strong inversion. As over mentioned, organic TFTs do not operate in inversion mode, so actually it should not be possible to define a threshold voltage. Nevertheless, the threshold voltage concept is useful for organic TFTs, since it represents the minimum gate-source voltage required to obtain appreciable drain current, and because it marks the transition between the different regions of operation.

Equations 1.3.1, 1.3.2 clearly state that is possible to extrapolate the mobility

of the OTFT from the  $I_{ds}$  vs.  $V_{gs}$  characteristic. In particular it follows that the mobility  $\mu$  is proportional to  $I_{ds}$  in linear regime and to its square root  $I_{ds}^{1/2}$ in saturation regime. The two mobilities can slightly differ, we have decide to work with the one calculated in saturation regime because it is less affected by parasitic currents. Two other parameters are usually consider to evaluate the performance of an organic transistor: one is the onset voltage  $V_{on}$ , defined as the gate-source voltage at which  $I_d$  increases abruptly (see figure: 1.4), and the inverse of the sub-threshold slope  $S^{-1}$ , that is the voltage step needed to gain one decade in current at  $V_{on}$ . The sub-threshold slope depends on the gate dielectric capacitance and on the trap states at the interface [44].

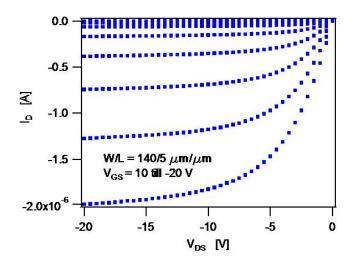

Figure 1.5: OTFT output characteristic.

An output characteristic is obtained by measuring the current  $I_{ds}$  varying the drain-source voltage for different gate voltage levels (see Fig. 1.5). Here we can distinguish two regimes, the linear one, where  $I_{ds}$  is linearly proportional to  $V_{ds}$ , and the saturation one, where  $I_{ds}$  should be almost independent of  $V_{ds}$ .

#### 1.3.3 Pentacene

All the OTFTs that we have manufactured within this work, used *Pentacene* as organic semiconductor. For this reason we have considered appropriate to dedicate a subsection to this organic material.

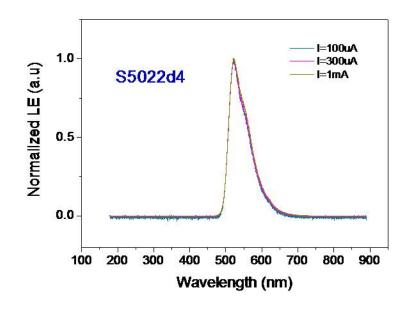

Although a substantial number of small-molecule semiconductors have emerged, Pentacene consistently provides the largest carrier mobilities, due to its favorable crystal structure. This organic material is constituted by five linearly-fused benzene rings ( $C_{22}H_{14}$ ) and it has the appearance of a dark-blue powder (its structure is shown in figure 1.6). Being a small molecule, Pentacene can be deposited by evaporation in ultrahigh-vacuum (around  $10^{-8}$  torr in our system) with a technique called Organic Molecular Beam Deposition (OMBD). The Pentacene is heated in a Knudsen cell until it sublimates (usually around 200°C). The molecules evaporate inside a chamber where the sample is usually anchored upside down (see App. C for more details). The growth of the Pentacene layer is highly influenced by the temperature of the cell and of the substrate. Pentacene can also be deposited using an OVPD system. In this case the molecules of the material are transported by a carrier gas at low vacuum.

Figure 1.6: Structure of a molecule of Pentacene  $(C_{22}H_{14})$ .

In the following I will provide some details about the Pentacene growth relying on Stijn Verlaak's PhD thesis about the growth of small-molecule organic semiconductors [45, 46]. During the semiconductor deposition from a gas phase, Pentacene molecules hit the substrate and start to accumulate at the surface. When several molecules aggregate, a *nucleus* is formed. This nucleation process can be modelled thermodynamically. Simulations reveal that due to the increasing number of aggregated molecules, the nuclei start to growth determining the start of the Pentacene thin-film growth. Depending on the growth condition, two-dimensional or three-dimensional nuclei can be formed. These two different growths are, electronically speaking, very different. Three-dimensional nuclei form ill-connected, isolated grains while two-dimensional growth, on the contrary, leads to the formation of a continuous film. The growth on one regime, or the other one, is determined by the deposition rate and the substrate temperature. Obviously, also the kind of substrate plays a role on the morphology of the film. Chemically treating the substrate, i.e with self-assembled monolayers, it is possible to tune the surface energy of the substrate (for more details see App. B). Prior to the real deposition, vacuum sublimation and/or absorption chromatography are used to purify Pentacene. The grade of purity of the material has a tremendous impact on the mobility of the finalized devices. As previously mentioned, with this organic semiconductor it is possible to obtain OTFTs with mobilities up to 5  $\rm cm^2/Vs$  [47]. One of the drawbacks of using this material, it is the fact that it quickly degrades in presence of oxygen and light. An unstable transistor can be characterized by a shift of the transfer curves towards more positive or negative voltages. This voltage shift can be influenced by an extended applied bias, illumination or other environmental conditions. For this reason, all the organic devices, manufactured using Pentacene as a semiconductor, need an effective encapsulation (a specific study about this topic is provided in chapter 6).

# Chapter 2 OLEDs optical investigation

For studying optoelectronic devices it is interesting not only to investigate the amount of light generated by the device, but also the distribution of this emitted light along the active area. Such a study can give many information about the device, like the current distribution, heat distribution, presence of defects, hot spots, etc. Often during the ageing, the device modifies its light emission distribution, and the investigation of this variation can help in understanding the physical mechanisms behind the degradation of the optical and electrical characteristics. The light emission distribution of an OLED along its active area, can be measured by using an emission microscope<sup>1</sup>. In this chapter we present two optical studies that we have carried out on phosphorescent OLEDs, and on solution-processed OLEDs.

### 2.1 PHOLED size and shape impact on light emission

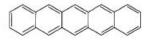

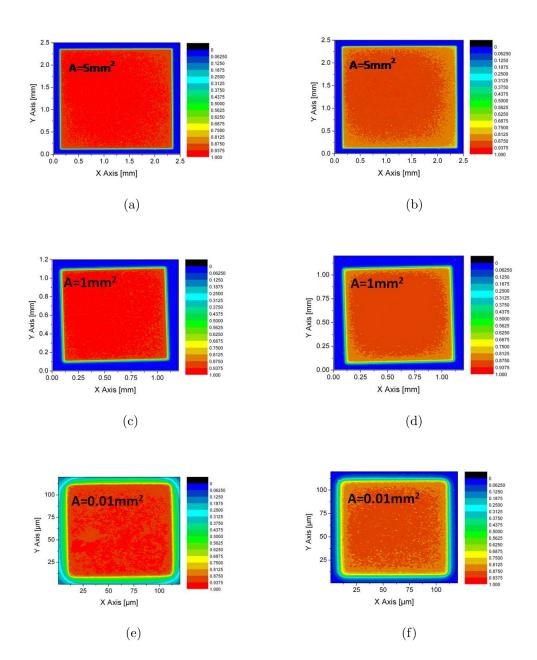

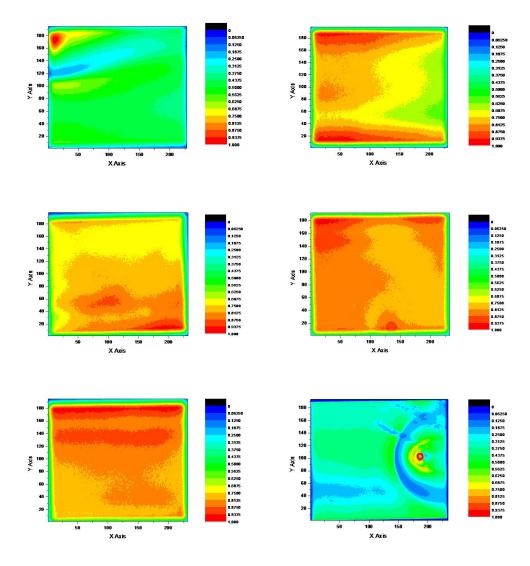

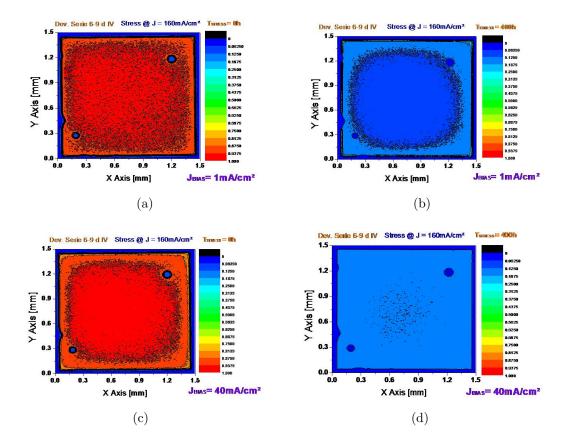

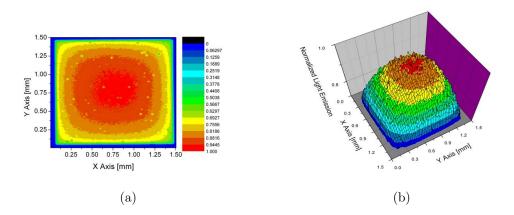

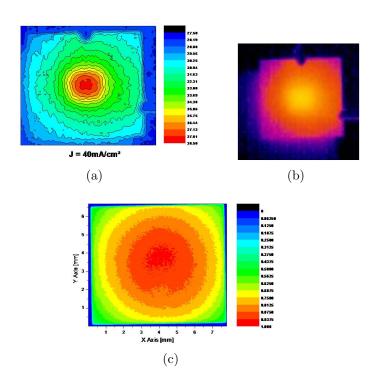

In the following we present an optical analysis that we have carried out on phosphorescent OLEDs (PhOLEDs), with different size and shape. In particular, we measured devices with  $5\text{mm}^2$ ,  $1\text{mm}^2$ , and  $0.01\text{mm}^2$  active area with square and circular shape. All the different devices have been biased with equal current density in order to correctly compare their light emission profiles, i.e. the distribution of the light emission intensity all along the active area. We have arbitrary decided to bias the devices at two different current density levels:  $1\text{mA/cm}^2$  and  $40\text{mA/cm}^2$ . In this study we have used an Hamamatsu emission microscope, and its parameters have been set in order to maximize the CCD acquisition range. We have used microscopic lenses with different magnifications and the light emission profiles have been normalized to their maximum.

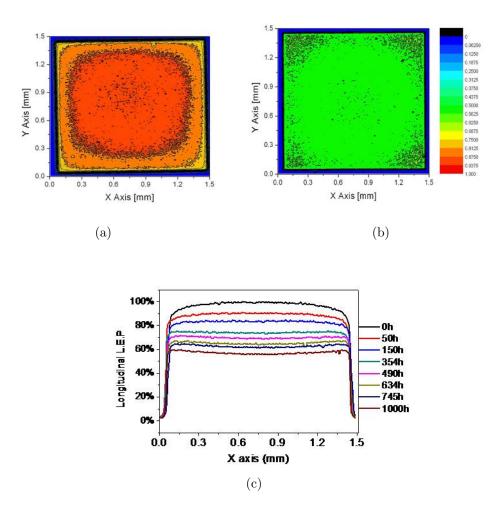

The Light Emission Profiles (LEP) have been analysed by using false colours

<sup>&</sup>lt;sup>1</sup>An emission microscope is a microscope furnished with a CCD camera that *counts* the photons emitted by the focused device, providing a number that is proportional to the light emitted. By keeping unchanged the measurement positions and parameters, it is possible to follow the optical degradation of a device over time.

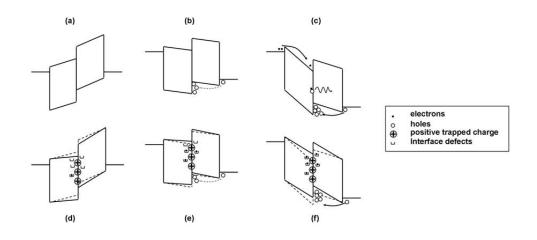

Figure 2.1: Light emission profiles of squared PhOLEDs with different size, measured at  $1mA/cm^2$  and  $40mA/cm^2$ : (a) square  $5mm^2$  at  $1mA/cm^2$ , (b) square  $5mm^2$  at  $40mA/cm^2$ , (c) square  $1mm^2$  at  $1mA/cm^2$ , (d) square  $1mm^2$  at  $40mA/cm^2$ , (e) square  $0.01mm^2$  at  $1mA/cm^2$ , (f) square  $0.01mm^2$  at  $40mA/cm^2$

Figure 2.2: Light emission profiles of circular PhOLEDs with different size, measured at  $1mA/cm^2$  and  $40mA/cm^2$ : (a) circular  $1mm^2$  at  $1mA/cm^2$ , (b) circular  $1mm^2$  at  $40mA/cm^2$ , (c) circular  $0.25mm^2$  at  $1mA/cm^2$ , (d) circular  $0.25mm^2$  at  $40mA/cm^2$ , (e) circular  $0.01mm^2$  at  $1mA/cm^2$ , (f) circular  $0.01mm^2$  at  $40mA/cm^2$

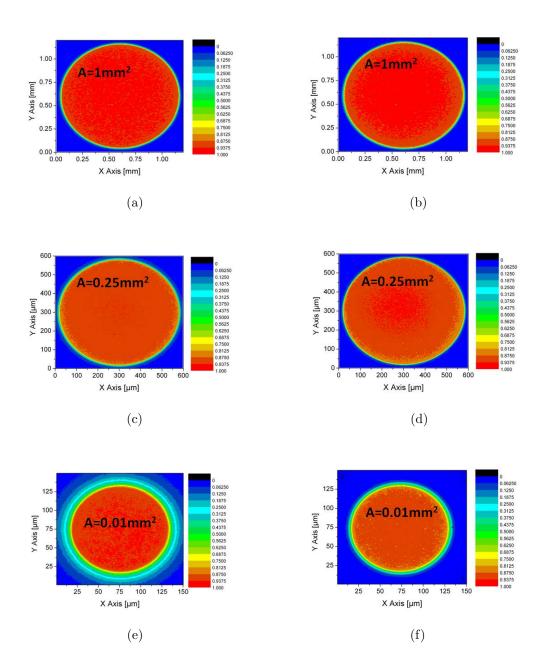

maps, normalized to the maximum intensity along the active area. As clearly shown in the LEPs shown in Fig. 2.1 and Fig. 2.2, light emission is quite concentrated in the centre of the active areas. The phenomenon is more pronounced at high current density  $(40 \text{mA/cm}^2)$ . The effect seems to be independent of the size of the device area, being present both in the small, medium and large area devices. Reducing the area, it is not possible to obtain a fully uniform emission pattern. As previously mentioned the light is concentrated more in the centre of the device, therefore at the corners of the squared structures we can observe a lower intensity of the light emitted (see Fig. 2.1). Nevertheless, even observing the circular devices reported in Fig. 2.2, we notice a border effect that is probably related to a crowding current effect. Such an effect will be further investigated in chapter 4 where it will be related with the surface thermal distribution of the devices. Finally, we have tried to compare the integrated optical power of a square device with a circular one on equal area, in order to understand if a structure could be more efficient than the other one in terms of total optical power. The experiment has been repeated at different bias current levels. The results are reported in Fig. 2.3, that shows that there is no significant difference in the total light emitted by the two different devices.

Figure 2.3: Integrated optical power of a circular and a square device of equal area  $(1mm^2)$ , measured at different current density levels.

### 2.2 Light emission distribution of solution processed OLEDs

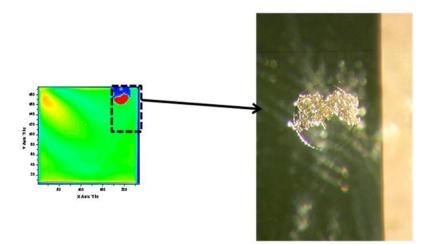

In the following, we report an investigation on the optical properties of solution processed OLEDs. We have performed emission profile and spectral measurements for analysing the optical uniformity of the devices. As in the study presented in the previous section, the emission profiles have been measured by using an *Hamamatsu Phemos* emission microscope. The devices have been biased by means of a Keithley current source. The  $2\text{mm}^2$  devices have biased with a current of  $60\mu\text{A}$ . The emission profiles reported in the figures below have been normalized to their maximum, in order to better describe the range of light intensity variation at devices surface. Measured emission profiles are shown in the following figures (Fig. 2.4 and Fig. 2.5) for a set of 7 devices.

Figure 2.4: Light emission profiles of solution processed OLEDs biased at 1mA.

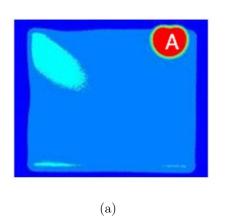

For devices reported in Fig. 2.5 the bias current level has been adjusted in order not to saturate the  $CCD^2$  of the microscope. This device showed a non-uniform emission pattern, with a spot-like emission behaviour (region A in Fig. 2.5(a)). After the electro-optical characterization we have noticed that the emission pattern in region A has changed (see Fig. 2.5(b)). This effect has been attributed to the presence of some material, accumulated between the anode and the coating that seems the result of a combustion process (shown by using a stereoscopic microscope in Fig. 2.6).

$<sup>^2\</sup>mathrm{CCD}$  stands for Charge-Coupled Device.

Figure 2.5: Light emission distribution measured before (a) and after (b) electro-optical characterization.

Figure 2.6: Stereoscopic microscope picture of impurities formed upon device.

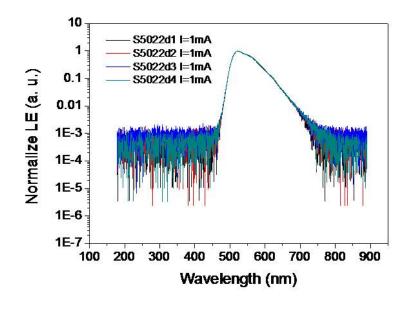

Using an Ocean Optics USB 4000 spectrometer we have measured the emission spectra of this solution processed OLEDs. The light emission has been normalized to the peak value in order to allow the comparison of the spectra shape of the different devices. We did not detect any dependence of the spectral shape on the injected current level (see Fig. 2.7). For this reason, we have arbitrary compared the behaviour of the different OLEDs carrying out spectra measurements at 1mA (see Fig. 2.8). All the devices showed nearly the same spectral shape. In particular, not even the spectrum of device with uneven light emission distribution, previously shown in Fig. 2.5, has shown any significant difference from other devices.

Figure 2.7: OLED Emission spectrum at different current levels.

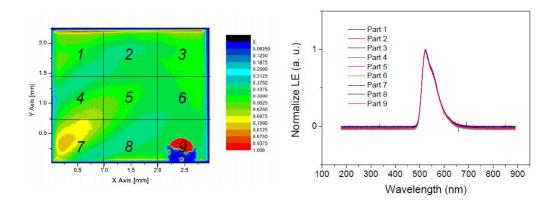

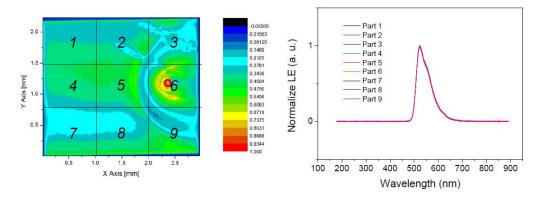

In order to further investigate possible relation between luminescence unevenness and spectrum emission, we have measured local emission spectra by integrating our spectrometer with a microscope. In this way we were able to obtain small focused portion of the active area. The emission spectra collected in 9 different regions are reported in Fig. 2.9 and 2.10. We have normalized the light emission spectra to their peak values in order to detect possible variations of spectral shape among the nine zones of the active area. Nevertheless, no significant variation has been detected between the different regions.

Therefore, the solution processed OLEDs that we have tested showed uneven emission distribution all along the active area, especially if compared with the evaporated OLEDs showed in the previous section. This fact suggests that the unevenness of the emission profile does not correspond to modification in the spectral characteristics, but it is correlated only to differences in current/emission distribution, reasonably related to technological defects.

Figure 2.8: OLED emission spectra of different devices.

Figure 2.9: Emission spectra measured in 9 different parts of the active area.

Figure 2.10: Emission spectra measured in 9 different parts of the active area.

# Chapter 3

# Reliability stress tests on Alq3/NPD OLEDs

In this chapter, first we present a study about the investigation of the reliability of small molecules OLEDs, with simplified structures, consisting of NPD as hole transport layer, and Alq3 as electron transport layer. The results of this analysis provide information on the physical processes responsible for OLED degradation. Secondly, we focused on a reliability study that we have performed on phosphorescent OLEDs stressed at different current levels. The variation of the electrical and optical characteristics of these devices have been monitored in order to study the degradation effects, and extrapolate a time to failure law.

## 3.1 Optical and electrical degradation of NPD/Alq3 OLEDs

As previous mentioned, OLEDs have attracted much attention for their large potential in flat panel display application. In this context lifetime of OLEDs is a critical parameter in order to fulfil market standards. OLEDs luminance reduction over time has been deeply investigated [48, 49, 50, 51] and driving strategies and new materials have been developed in order to solve this criticality in OLEDs spread [52, 53, 54]. In the following we present our study on the electro-luminescence degradation mechanism in NPD/Alq3 based (a resume of the state of the art of this relevant topic has been reported in chapter 1.2.1). Moreover, we focused on intrinsic degradation phenomena that determine the decrease in the optical power of OLEDs during standard operation. The study was carried out on simplified OLED structures, by means of combined optical and electrical characterization techniques. Our investigations were carried out on simplified undoped OLED structures, because such devices allow an easy interpretation of the impedance measurements. The approach we followed here, favours simplicity in studying the degradation mechanisms of the organic materials interface, over exactness in determining the real device lifetime, which is not our primary goal. In fact, the degradation kinetic highlights a quite fast degradation (with a strong reduction after 1000-hour stress), which is not unexpected, but it is due to the simple OLEDs structure.

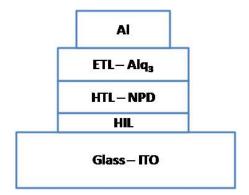

In this work we have tested OLEDs with NPD as HTL and Alq3 as ETL and as Emitting Layer (EML). The device structure is reported in Fig. 3.1. The analysis was performed on devices with different thicknesses for the HTL and ETL layers (as summarized in Fig. 3.2), with the aim of understanding whether the thickness of the different layers could influence the OLED reliability. Samples were prepared on commercial Glass-ITO substrates, which consisted of a 20nm  $SiO_2$  barrier layer between the soda lime glass and 120nm thick ITO. All organic layers were deposited under high-vacuum conditions  $(1 \times 10^{-7} \text{ Torr})$  and the devices were transferred directly from vacuum into an inert environment glove-box, where they were encapsulated using a UV-curable epoxy, and a glass lid with a moisture getter. A 10nm thick HIL is deposited between the HTL and the ITO, in order to improve the hole injection rate from the anode during the forward bias condition. The cathode consisted of Aluminum deposited on Lithium Fluoride and the active areas were defined by an insulating grid. The OLED emission profiles were assumed to be Lambertian, and the luminance was measured with a Si-photodiode mounted on an integrating optical sphere.

Figure 3.1: Cross section of the device structure employed in this study.

| Anode | HIL  | HTL         | ETL          | Cathode    |

|-------|------|-------------|--------------|------------|

| 120nm | 10nm | NPD [100nm] | Alq3 [60nm]  | AI [100nm] |

| 120nm | 10nm | NPD [60nm]  | Alq3 [60nm]  | Al [100nm] |

| 120nm | 10nm | NPD [40nm]  | Alq3 [60nm]  | AI [100nm] |

| 120nm | 10nm | NPD [60nm]  | Alq3 [100nm] | AI [100nm] |

| 120nm | 10nm | NPD [60nm]  | Alq3 [80nm]  | AI [100nm] |

| 120nm | 10nm | NPD [60nm]  | Alq3 [40nm]  | AI [100nm] |

Figure 3.2: Table with the layers thicknesses of OLEDs studied within this work.

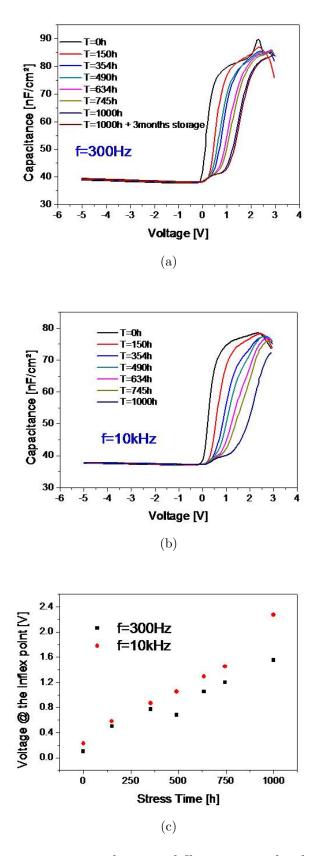

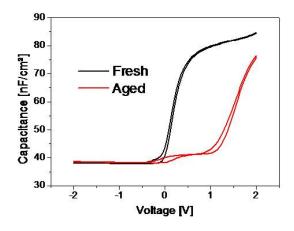

The devices were fully electrically and optically characterized. In particular, we periodically carried out Current density vs Voltage (J-V), Capacitance vs Voltage (C-V), and Luminance vs. Current density (L-J) measurements during

ageing time. We also used an *Hamamatsu Phemos* light emission microscope to measure the luminance profile all over the device active area. The devices subjected to this characterization and reliability study have an active area of  $2\text{mm}^2$ .

Figure 3.3: Luminance of OLED plotted as a function of bias current density.

Figure 3.4: OLED Current density (log scale in the left, linear scale in the right) vs. voltage.

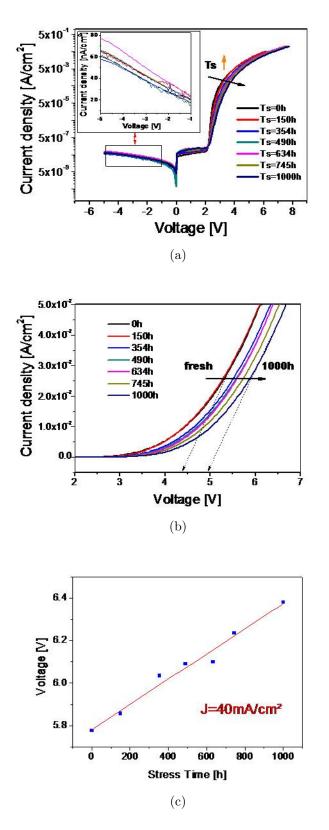

Fig. 3.3 shows the luminance as a function of the current density (L-J) for a typical OLED with the structure above described. The curve shows quite a linear relation between optical power and the injected current density. Fig. 3.4 shows the J-V typical curve taken on a device with 100nm Alq3 and 60nm NPD layers, plotted in semi-logarithmic scale. In order to simplify the following discussion, we arbitrary distinguish four regions on the basis of current dependence on applied voltage  $(V^*)$ :

**Region 1:** The reverse bias region  $V^* < 0V$

**Region 2:** The low-forward bias regions  $V^* > 0V$  and  $V^* < 2V$

- **Region 3:** The exponential forward region (namely,  $2 < V^* < 5V$ ), where the current exponentially increases with voltage

- **Region 4:** The linear forward region (namely  $V^* > 5V$ ), where the current linearly increases with the anode voltage

The horizontal marker in Fig. 3.4 defines the operative current of our OLEDs, i.e.  $40\text{mA/cm}^2$ . In the following, we will arbitrarily refer to  $V_{ON}$  as the anode voltage needed to achieve such current density level. All the devices were stressed at a constant current density of  $120\text{mA/cm}^2$ , i.e. three times larger than the nominal current density. We chose such a current in order to achieve a reasonable acceleration of the life tests, avoiding the formation of parasitic leakage paths across the organic films, and the consequent device breakdown. During the electrical stress the devices were kept at room temperature. The accelerated electrical stress was periodically interrupted in order to perform the characterization of the devices (L-I, J-V, and C-V).